一種并行多通道數(shù)據(jù)獲取系統(tǒng)設計

郭 潔,潘燁煬,張林穎,李 婷,王 鵬

(中北大學 信息與通信工程學院,山西 太原 030051)

0 引言

近20年里無損檢測技術在我國得到了迅速的發(fā)展,其若干單項技術在研制和運用水平上都已經(jīng)進入了國際先進行列,并在航空航天、武器制造、汽車制造以及海關檢查等工農(nóng)業(yè)生產(chǎn)和生活中得到廣泛應用。通過多次技術合作和攻關,已制定了回彈法、超聲回彈綜合法、取芯法、拔出法等一系列無損檢測的規(guī)程。伴隨著無損檢測技術的發(fā)展和日益完善,除了常用的超聲波外,紅外成像技術、雷達技術、波動分析技術、電磁、激光等技術也逐漸被應用。隨著配套開發(fā)和研制的檢測設備發(fā)展到智能化時代,相位信息已在無損檢測領域廣泛應用[1-3]。與此同時,激振檢振技術在工程應用中更是無損檢測研究的一個重要的方向[4,5]。

傳統(tǒng)的數(shù)據(jù)獲取系統(tǒng),多采用異步多路數(shù)據(jù)采集模式,此類系統(tǒng)僅能獲取模擬信號的頻率幅度信息,本文根據(jù)激振檢振技術相位信息運用需求,介紹了一種多通道同步數(shù)據(jù)獲取系統(tǒng),此系統(tǒng)不但能夠采集到模擬信號的頻率幅度信息,同時能夠保持不同模擬信號之間的相位信息[6]。

1 系統(tǒng)設計方案

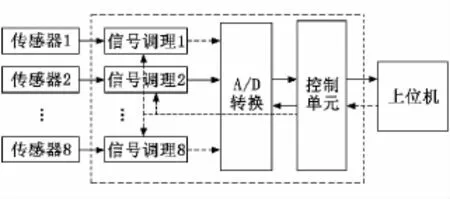

多通道數(shù)據(jù)獲取系統(tǒng)總體框圖如圖1所示。系統(tǒng)提供8通道模擬信號輸入通道,多路模擬開關應用于系統(tǒng)的擴展,以增加模擬通道的路數(shù);傳感器模擬輸出信號常夾雜高頻噪聲,由調(diào)理電路完成對高頻噪聲的濾除,同時為提高A/D轉(zhuǎn)換器模擬輸入的動態(tài)范圍,調(diào)理電路還需對模擬信號進行放大;A/D轉(zhuǎn)換模塊采用8通道同步模擬轉(zhuǎn)換器,以完成8路模擬信號的同步采樣;控制單元主要完成A/D轉(zhuǎn)換器的驅(qū)動、多路模擬開關的導通控制、信號調(diào)理模塊的相應控制及與硬件系統(tǒng)和上位機間的通信。

圖1 多通道數(shù)據(jù)獲取系統(tǒng)總體框圖

2 分系統(tǒng)設計

根據(jù)總體設計方案,該系統(tǒng)包括調(diào)理模塊、多路模擬開關、A/D轉(zhuǎn)換器、通信接口及控制單元等。

2.1 調(diào)理電路

信號調(diào)理模塊包括低通濾波和信號放大兩個部分。

2.1.1 濾波電路

傳感器輸出的模擬信號常含有高頻噪聲,需設計一低通濾波電路將高頻噪聲進行濾除。常用的低通濾波電路有兩種[7]:①運放加阻容元件;②采用集成濾波芯片。集成濾波芯片具有精度高、體積小的特點,本系統(tǒng)采用集成低通濾波芯片[8]MAX291。

MAX291具有外部時鐘和內(nèi)部時鐘兩種工作方式,根據(jù)其工作原理,本系統(tǒng)采用內(nèi)部時鐘方式,電路較為簡單,使用方便。當使用內(nèi)部時鐘時,其時鐘頻率f(kHz)由CLK引腳與地之間跨接的一電容C確定,具體關系如下:

其中:C為CLK與地之間跨接的電容,pF。

MAX291的截止頻率為時鐘頻率的1/100,根據(jù)工程需要,本系統(tǒng)時鐘驅(qū)動電容C取值為20pF。為保持各路相位信息的一致性,系統(tǒng)采用一片電容驅(qū)動各路濾波芯片內(nèi)部時鐘。低通濾波電路如圖2所示。

圖2 低通濾波電路

2.1.2 放大電路

由于輸入模擬信號的動態(tài)范圍無法滿足A/D轉(zhuǎn)換器的模擬輸入要求,為使輸入信號與采樣信號匹配,在濾波電路之后加一程控運算放大電路,如圖3所示。

圖3 程控放大電路

程控放大電路為一同相輸入運算電路,由高速高精度運算放大器和數(shù)字電位器構(gòu)成。通過控制數(shù)字電位器的阻值實現(xiàn)電路放大倍數(shù)的控制。高速運算放大器選用OP37,該運放具有噪聲低、失調(diào)電壓小、溫漂小等特點,增益帶寬積達到63MHz。數(shù)字電位器選用MAX5484,該電位器具有非易失、線性變換的特性[9],有1 024個抽頭,最大電阻為50kΩ。

2.2 采集模塊設計

信號采集電路采用MAXIM公司生產(chǎn)的MAX1308,其具有獨立8通道模擬輸入端口,獨立的采樣保持電路為每個通道提供同時采樣,提供5V的模擬信號電壓輸入范圍,采樣精度為12位,采樣頻率達到每通道456ks/s。為了保證ADC芯片的12位采樣精度,在每個模擬輸入通道之前設計了一個由OP37構(gòu)成的電壓跟隨器,作為輸入緩沖模塊。

根據(jù)MAX1308的工作原理,系統(tǒng)使用其內(nèi)部參考時鐘,因為ADC芯片的8個通道在電路使用中均一直處于工作狀態(tài),所以在電路設計中放棄關斷模式和通道關斷模式,將芯片的SHDN管腳置為低電平,CHSHDN置為高電平;其余的控制管腳與控制器FPGA相連,12位數(shù)字總線與FPGA的IO口連接,并行輸出轉(zhuǎn)換后的12位數(shù)字信號,同時D0~D7端口作為配置信息輸入端口。ADC芯片連接示意圖見圖4。

2.3 輔助電路設計

輔助電路包括系統(tǒng)電源及通信接口設計兩個部分。ADC芯片的供電電壓為±5V,采用LM7805和LM7905進行供電,控制器EP3C10E144C8N的供電電壓為3.3V、1.5V 和1.2V,采用LM1117系列芯片進行供電。為方便與上位機相連,通信接口選用RS232-USB通信方式[10],轉(zhuǎn)換芯片選用Prolific公司生產(chǎn)的PL2303,該芯片僅需外接幾只電容便可實現(xiàn)USB信號與RS232信號的轉(zhuǎn)換,實現(xiàn)上、下位機的雙向通信。

圖4 ADC芯片連接示意圖

2.4 控制模塊設計

完成信號調(diào)理及ADC模塊硬件設計之后,最重要的便是其ADC轉(zhuǎn)換邏輯、程控放大自動增益控制以及整個系統(tǒng)的時序控制。系統(tǒng)選用ALTERA公司生產(chǎn)的FPGA芯片EP3C10E144C8N,完成與上位機之間的通信和對ADC芯片的驅(qū)動及程控放大的控制。下位機軟件采用分層模塊化設計,運用VHDL語言及集成開發(fā)工具定制文件實現(xiàn)。下位機軟件大致可以分為3個部分,即系統(tǒng)總體控制程序、ADC驅(qū)動控制程序及程控運放控制程序。

程控運放程序主要完成信號調(diào)理中運放的自增益設置。首先從控制器RAM中讀取數(shù)控電位器控制數(shù)據(jù),若數(shù)據(jù)有效便將數(shù)據(jù)寫入數(shù)控電位器,若無效則初始化后寫入,啟動一次ADC,并根據(jù)采集回的數(shù)據(jù)進行運放電阻調(diào)制,直至將測量電壓調(diào)制在4.5V~-4.5V附近,最后將電位器控制參數(shù)寫入控制器RAM,具體流程如圖5(a)所示。

ADC控制程序主要完成ADC芯片的驅(qū)動控制。首先通過數(shù)據(jù)總線D0~D7對ADC芯片進行配置,使模擬8通道均處于使用狀態(tài)。配置完畢后,啟動ADC芯片,等待所有通道均轉(zhuǎn)換完畢后,對各通道數(shù)據(jù)進行依次讀取,具體流程如圖5(b)所示。

下位機主控制程序負責下位機整體時序的控制。程控運放增益倍數(shù)調(diào)制合適后,將數(shù)字電位器控制參數(shù)發(fā)送回上位機,啟動ADC芯片進行數(shù)據(jù)采集,并將采回的數(shù)據(jù)發(fā)給上位機。若系統(tǒng)為連續(xù)采集,則重新啟動ADC芯片重復上述步驟;如非連續(xù)采集,則結(jié)束此次數(shù)據(jù)采集。主程序流程如圖5(c)所示。

圖5 下位機軟件流程圖

3 實驗結(jié)果

完成系統(tǒng)的硬件設計以后,運用分層模塊化的方式,對ADC控制軟件進行了實現(xiàn),并進行了在線仿真,通過信號convt對ADC進行啟動控制,當各通道數(shù)據(jù)全部轉(zhuǎn)換完畢后(eolc0和eolc1均為低電平),通過連續(xù)的8個rd信號,完成8通道采集數(shù)據(jù)的讀取,具體仿真結(jié)果如圖6所示。

圖6 ADC控制仿真

4 結(jié)語

本文根據(jù)激振檢振工程運用需求,介紹了一種基于MAX1308的并行數(shù)據(jù)采集系統(tǒng)方案,可以完成8通道模擬數(shù)據(jù)的同時采集,能夠很好地保持各通道數(shù)據(jù)間的相位信息,并利用VHDL語言及集成開發(fā)工具定制文件,通過分層模塊化的方式,很好地完成了在電壓范圍內(nèi)的采樣,實現(xiàn)了對ADC控制軟件的設計和仿真。

[1] 劉穎韜,郭廣平,楊黨綱.脈沖相位法用于復合材料層析檢測的研究[J].激光與紅外,2009,39(4):390-392.

[2] 張娟,沙愛民,孫朝云,等.基于相位編組法的路面裂縫自動識別[J].中國公路學報,2008,21(2):39-42.

[3] 趙瑩瑩,田裕鵬.脈沖相位光熱輻射測量中的數(shù)據(jù)擬合處理方法[J].無損檢測,2007,29(11):637-640.

[4] 梅志遠,羅忠,周欣,等.夾心復合材料基座激振[J].振動與沖擊,2009,28(1):152-165.

[5] 王曉,張朝暉,藍金輝,等.基于振動能量分析的管道裂痕診斷[J].儀器儀表學報,2005,26(s2):606-607.

[6] 陳子為,鄧芳.基于ADS8364的多通道高速數(shù)據(jù)采集處理系統(tǒng)[J].數(shù)據(jù)采集與處理,2006,21(12):226-231.

[7] 李志強.12電極ECT傳感器和數(shù)據(jù)采集系統(tǒng)的研究[D].哈爾濱:哈爾濱理工大學,2009:3.

[8] 劉國營,劉俊,李杰.基于ADS8364和DSP的高速數(shù)據(jù)采集系統(tǒng)設計[J].微計算機信息,2007,23(8):190-191.

[9] 周建會,韓焱,王鑒.考場防作弊干擾器的設計[J].傳感技術學報,2010,23(1):43-46.

[10] 胡寧博.非閉合式電極電容層析成像傳感器的設計及實驗研究[J].計算機測量與控制,2012,20(2):520-522.