基于RocketIO的SATA物理層實(shí)現(xiàn)

楊佳朋,張 剛,郝 敏

(太原理工大學(xué)信息工程學(xué)院,山西太原 030024)

基于RocketIO的SATA物理層實(shí)現(xiàn)

楊佳朋,張 剛,郝 敏

(太原理工大學(xué)信息工程學(xué)院,山西太原 030024)

以Virtex-5系列FPGA內(nèi)嵌的RocketIO收發(fā)器模塊為平臺,分析SATA(串行高級技術(shù)附件)協(xié)議的物理層功能,把RocketIO收發(fā)器的內(nèi)部結(jié)構(gòu)特點(diǎn)與協(xié)議要求相結(jié)合,設(shè)計了基于RocketIO收發(fā)器的SATA物理層電路。

Rocket IO;SATA協(xié)議;高速串行傳輸

隨著硬盤等存儲設(shè)備容量的增加,對數(shù)據(jù)傳輸?shù)乃俣仍絹碓礁撸瑐鹘y(tǒng)的并口硬盤(PATA)的速度已達(dá)瓶頸(133 Mbit/s),進(jìn)一步提高頻率,將加大16根數(shù)據(jù)線間的干擾,使得串行數(shù)據(jù)傳輸技術(shù)應(yīng)運(yùn)而生。SATA(Serial Advanced Technology Attachment)[1],即一種串行數(shù)據(jù)傳輸協(xié)議,相比并傳,改用串行線路進(jìn)行信號傳輸,一次只傳一位,干擾的降低可以在一定條件下大幅提高頻率,一代傳輸速率已達(dá)到150 Mbit/s,再定義更加完善的校驗(yàn)措施使得SATA總線具有廣闊的應(yīng)用前景。但其串并傳喚和高頻傳輸增加了實(shí)現(xiàn)難度,Xilinx公司在其Virtex-5 LX 系列產(chǎn)品中推出的 RocketIO GTP[2],速率可高達(dá)3.125 Gbit/s,是一種可靈活可配置的千兆位級高速串行收發(fā)器,為SATA協(xié)議相關(guān)的傳輸要求提供了重要參考,簡化了設(shè)計。

1 SATA協(xié)議物理層

本文參照的SATA協(xié)議是2001年由 Intel、APT、Dell、IBM、希捷、邁拓等幾大廠商組成的 Serial ATA委員會正式確立的 Serial ATA 1.0[1]規(guī)范。

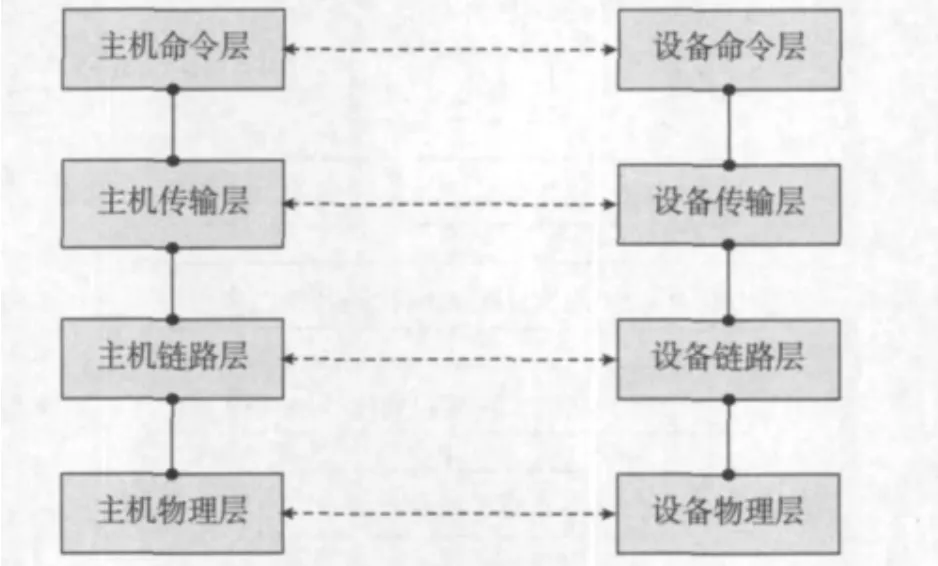

協(xié)議分4層架構(gòu),又下至上依次是物理層、鏈路層、傳輸層和命令層,如圖1所示。上面3層交互通過物理層實(shí)現(xiàn),故物理層的實(shí)現(xiàn)對上面3層的功能具有重要意義。物理層建立SATA信號傳輸?shù)谋忍亓魍罚M(jìn)行鏈路初始化、電源管理和熱插拔等操作。鏈路層和傳輸層協(xié)同進(jìn)行原語的收發(fā)、幀信息結(jié)構(gòu)(FIS)[3]的編解碼等工作。命令層代表大腦,向下發(fā)送讀寫命令,并接收下層的幀信息向主機(jī)端反饋。

圖1 SATA架構(gòu)

物理層位于協(xié)議的最底層,用于實(shí)現(xiàn)最基本的數(shù)據(jù)通信環(huán)境。內(nèi)部結(jié)構(gòu)包括模擬前端和控制模塊,控制模塊與鏈路層進(jìn)行交互,向其反饋物理層的工作狀態(tài),把控制信號傳給模擬前端。作為最基本的傳輸層,由于各種硬件具備不同的特性和來源,使它實(shí)現(xiàn)起來很復(fù)雜。采用Xilinx公司Virtex5芯片中的RocketIO收發(fā)器,可以簡化設(shè)計。

2 RocketIO GTP簡介及工作原理

2.1 RocketIO GTP 簡介

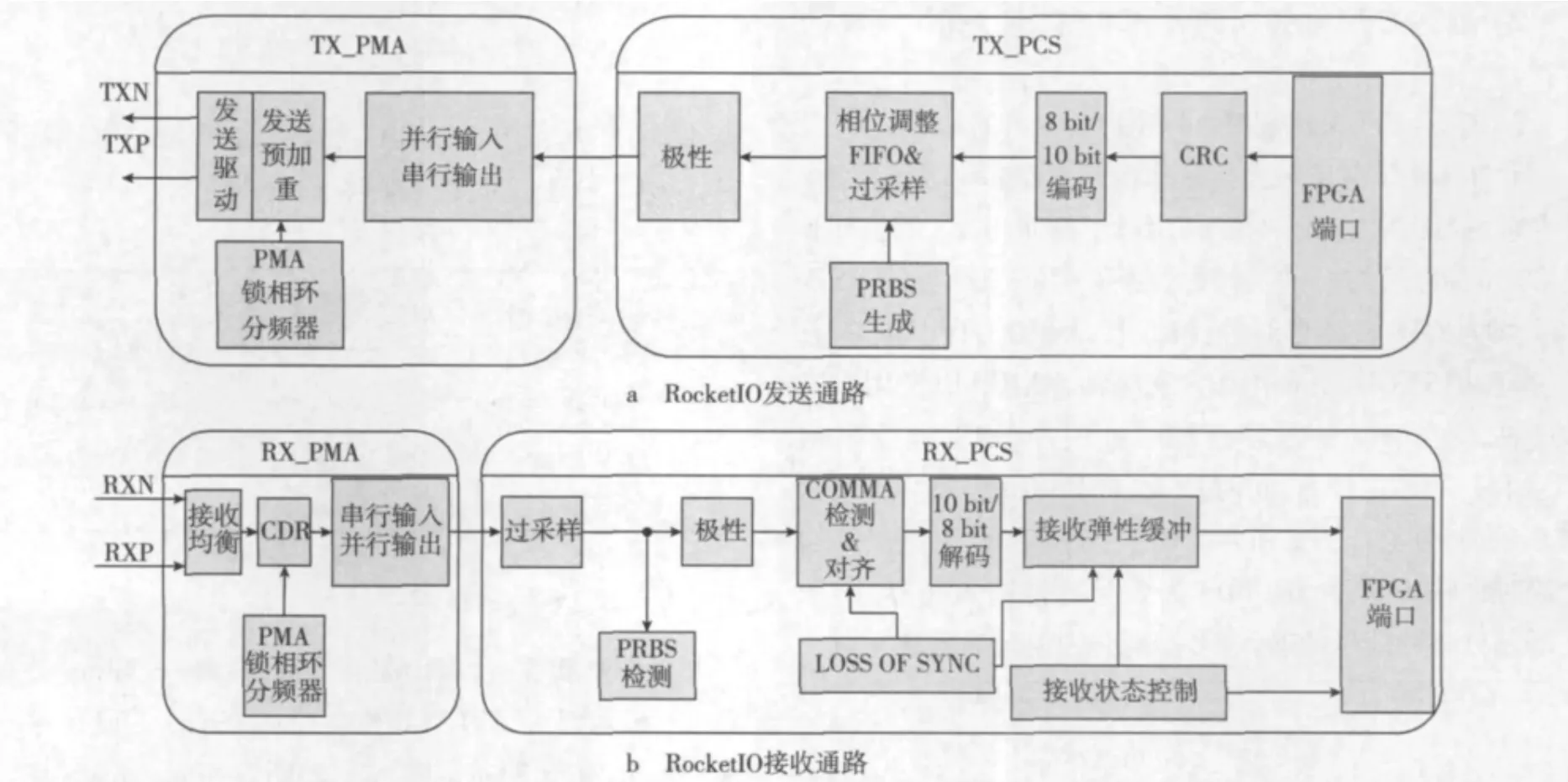

如圖2所示,RocketIO GTP由物理介質(zhì)附屬子層(PMA)和物理編碼子層(PCS)組成,內(nèi)部結(jié)構(gòu)緊湊,可根據(jù)設(shè)計需要自由配置。PMA主要實(shí)現(xiàn)串并變換和時鐘優(yōu)化功能,另外包括發(fā)送預(yù)加重、接收均衡器等在線配置技術(shù)以實(shí)現(xiàn)最優(yōu)信號完整性。PCS部分負(fù)責(zé)編解碼工作,包含8 bit/10 bit編解碼器和支持通道綁定和時鐘校正的彈性緩沖器[4-5],并支持 comma[3]字符檢測,確保字節(jié)的準(zhǔn)確接收。PRBS為偽隨機(jī)二進(jìn)制序列,用于測試高速串行通道傳輸?shù)恼`碼率。CDR(Clock and Data Recovery)為時鐘數(shù)據(jù)恢復(fù)電路,和接收均衡器協(xié)同負(fù)責(zé)從一個復(fù)合的信號中把時鐘和數(shù)據(jù)都正確地恢復(fù)出來。圖中CRC校驗(yàn)在鏈路層實(shí)現(xiàn),在本模塊并不涉及。可見,RocketIO GTP的相關(guān)功能為SATA物理層內(nèi)部關(guān)鍵模塊的實(shí)現(xiàn)提供了重要技術(shù)支持。

圖2 RocketIO結(jié)構(gòu)

2.2 RocketIO GTP 工作原理

并行數(shù)據(jù)進(jìn)入RocketIO GTP發(fā)送端經(jīng)過8 bit/10 bit編碼,寫入到發(fā)送端FIFO,再轉(zhuǎn)換成串行差分?jǐn)?shù)據(jù)發(fā)送給設(shè)備。接收端的串行數(shù)據(jù)信號要首先經(jīng)過均衡器處理,寫入到接收端緩沖,恢復(fù)出接收時鐘,在時鐘的驅(qū)動下轉(zhuǎn)換成并行數(shù)據(jù),再次經(jīng)過10 bit/8 bit解碼,被寫入彈性緩沖區(qū),并做CRC檢驗(yàn)后并行輸出。簡而言之,就是將輸入的并行數(shù)據(jù)經(jīng)過編碼,轉(zhuǎn)化為高速的差分串行信號;同時接收高速串行信號,進(jìn)行時鐘和數(shù)據(jù)恢復(fù),轉(zhuǎn)換成并行數(shù)據(jù)輸出。

3 系統(tǒng)設(shè)計

SATA1.0協(xié)議[1]規(guī)定物理層的數(shù)據(jù)傳輸速率為1.5 Gbit/s,每個時鐘周期傳輸一位,考慮8 bit/10 bit編碼,故實(shí)際速率為150 Mbit/s,參考時鐘設(shè)為150 MHz。OOB[6]信號為帶外控制信號,分別為 COMWAKE,COMRESET,COMINIT,相對于數(shù)據(jù)傳輸具有優(yōu)先級,實(shí)現(xiàn)初始化和電源管理模塊。COMRESET只由主機(jī)發(fā)送,開始復(fù)位,COMWAKE雙方都可以發(fā)送,交互中喚醒對方,COMINIT只由設(shè)備發(fā)送,表示初始化連接。配置過程中,每2個GTP0和1共用1個鎖相環(huán)(PLL),構(gòu)成1個 GTP_DUAL,根據(jù)開發(fā)板 Datasheet選用了 GTP_DUAL_X0Y0。RocketIO GTP端口參數(shù)配置如表1所示。

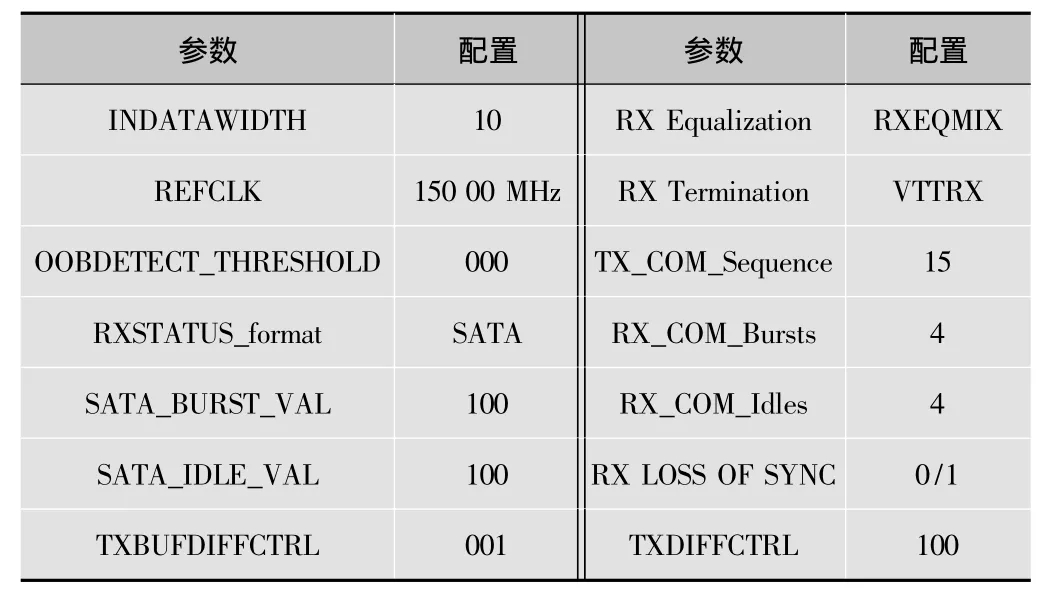

表1 GTP配置參數(shù)

并行數(shù)據(jù)位寬INTDATAWIDTH信號設(shè)置為10 bit。當(dāng)選擇SATA時,接收狀態(tài)控制信號RXSTATUS[0]表示OOB信號操作完成,RXSTATUS[1]表示收到COMWAKE信號,RXSTATUS[2]表示收到 COMRESET或 COINIT信號。RX Termination配置終端,VTTRX表示參考內(nèi)部電壓擺幅。RXLOSSOFSYNC為0代表8bit/10bit錯誤,1代表彈性緩沖中的通道綁定序列。TXENOOB用于發(fā)送,RXSIGDET用于接收共同管理OOB控制信號,通過配置的RocketIO GTP作為SATA物理層[7]的模擬前端電路。

3.1 時鐘控制

為提高時鐘精度,降低抖動,滿足GTP的高速運(yùn)作,需要配置高精度的時鐘。首先參考時鐘分頻產(chǎn)生鎖相環(huán)時鐘,借助于內(nèi)嵌在GTP_DUAL中的共享PMA鎖相環(huán),驅(qū)動GTP收發(fā)器的發(fā)送和接受通路。參考時鐘有3種方式提供:

1)使用外部振蕩器驅(qū)動專用時鐘布線;

2)通過專用時鐘布線使用相鄰 RocketIO模塊的時鐘;

3)使用 FPGA 內(nèi)部時鐘(GREFCLK[2])。

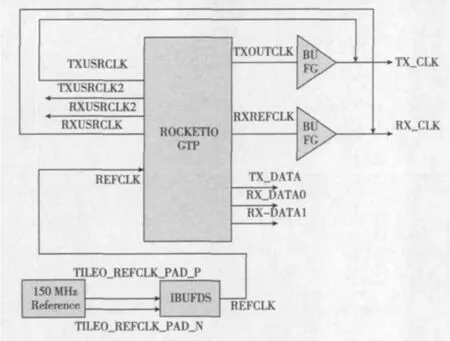

由于GREFCLK數(shù)據(jù)傳輸率低于1 Gbit/s,不予考慮。綜合前兩種時鐘方式,本文采用以下解決方案:150 MHz的參考時鐘經(jīng)過差分時鐘輸入緩存(IBUFDS)生成REFCLK作為GTP的參考時鐘;根據(jù)RocketIO GTP內(nèi)部四通道綁定,把TXOUTCLK用作發(fā)送時鐘,RXREFCLK用作接收時鐘,兩個時鐘信號經(jīng)全局時鐘緩沖(BUFG)輸出到TX_CLK和RX_CLK,同時作為 TXUSRCLK和 RXUSRCLK的時鐘源,如圖3所示。BUFG為Xilinx用戶提供的全局時鐘輸入緩存,IBUFDS為差分時鐘輸入緩存,用于外部差分時鐘信號的輸入,可提高時鐘信號的驅(qū)動能力。

圖3 時鐘分布圖

3.2 復(fù)位模塊

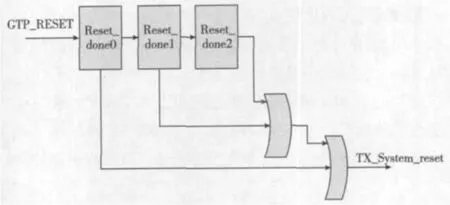

復(fù)位分為發(fā)送部分和接收部分,分別維護(hù)系統(tǒng)的穩(wěn)定。以發(fā)送模塊為例,如圖4所示,為了抑制外部復(fù)位信號輸入時的抖動情況,對GTP_RESET信號進(jìn)行兩級移位寄存器與操作,產(chǎn)生2個時鐘周期的延遲,保證足夠的復(fù)位時間,這樣該信號使能時的抖動就基本被濾除,配合時鐘信號從而保證整個系統(tǒng)邏輯的穩(wěn)定可靠。

3.3 數(shù)據(jù)通路

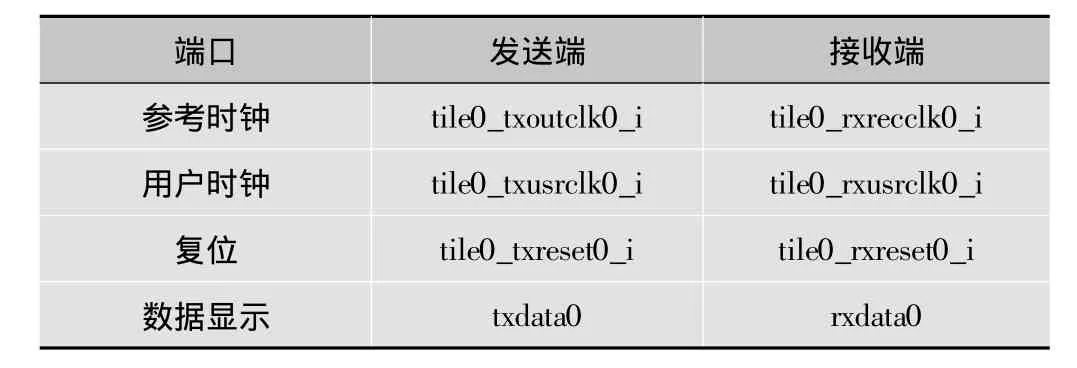

由于只是模擬物理層,沒有上層架構(gòu)發(fā)送數(shù)據(jù),故在發(fā)送時鐘tileo_txusrclk0_i的驅(qū)動下,由計數(shù)器發(fā)數(shù)、由RAM存儲。在接收時鐘的觸發(fā)下,由接收端接收、由串口模塊顯示。構(gòu)成GTP_DUAL的0和1兩端口復(fù)用相同資源,只列舉0端口重要的參數(shù),如表2所示。

圖4 復(fù)位模塊

表2 端口配置

4 驗(yàn)證及總結(jié)

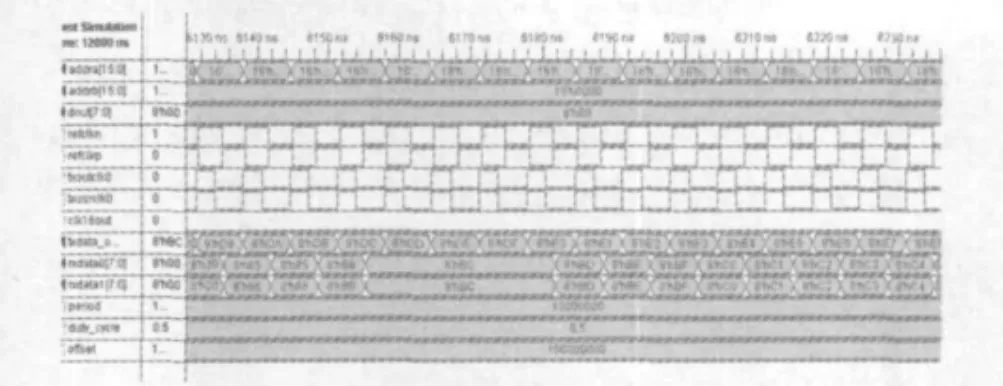

整個流程采用VHDL語言編寫,基于Xilinx公司的Vritex-5系列XC5VLX110T芯片在ISE10.1設(shè)計平臺上完成綜合、仿真和布局布線。如圖5所示,txdata在計數(shù)器的驅(qū)動下發(fā)送數(shù)據(jù),rxdata0和rxdata1為2條接收通道,經(jīng)過系統(tǒng)預(yù)設(shè)的20,65,85,6B后從BC開始接收數(shù)據(jù),與發(fā)送端數(shù)據(jù)一致,實(shí)現(xiàn)了正確接收。通過驗(yàn)證,本文對時鐘部分的設(shè)計可以正確接收發(fā)送的數(shù)據(jù),同時符合SATA1.0協(xié)議,集成度高、穩(wěn)定性強(qiáng)。

圖5 仿真圖(截圖)

5 小結(jié)

高速串行傳輸技術(shù)把時鐘與數(shù)據(jù)合并發(fā)送,再利用同步檢測正確恢復(fù)出時鐘,解決了高速數(shù)據(jù)傳輸過程中的抖動問題,降低設(shè)計復(fù)雜性和成本。本文基于Xilinx公司的Virtex 5 LX系列FPGA器件中內(nèi)嵌的Rocket IO IP核具有配置靈活、集成度高等優(yōu)點(diǎn),把它用于SATA物理層,實(shí)現(xiàn)了高效穩(wěn)定的數(shù)據(jù)傳輸,具有重要的現(xiàn)實(shí)意義。

:

[1]Serial ATA:High Speed Serialized ATAttachment Rev.1.0a[EB/OL].[2012-06-01].http://www.doc88.com/p-015901791536.html.

[2]Xilinx.Virtex-5 FPGA RocketIO GTP Transceiver User Guide[EB/OL].[2012-06-01].http://wenku.baidu.com/view/f76b533210661 ed9ad51f34f.html.

[3]鄧焰,戎蒙恬.基于FPGA的3.125Gbit/s串行通道設(shè)計實(shí)驗(yàn)[J].電子工程師,2004,30(11):16-18.

[4]李江濤.RocketIO高速串行傳輸原理與實(shí)現(xiàn)[J].雷達(dá)與對抗,2004,23(4):48-50.

[5]武榮偉,蘇濤,梁中英.RocketIO在高速數(shù)據(jù)通信中的應(yīng)用[J].通信技術(shù),2010,43(11):9-11.

[6]歐陽科文,黎福海,唐純杰.基于RocketIO的SATA物理層高速串行傳輸實(shí)現(xiàn)[J]. 計算機(jī)測量與控制,2009,17(5):937-938.

[7]胡錦,彭成,譚明.基于RocketIO的高速串行協(xié)議設(shè)計與實(shí)現(xiàn)[J].微計算機(jī)信息,2008,24(18):196-197.

Implementation of SATA Physical Layer on RocketIO

YANG Jiapeng,ZHANG Gang,HAO Min

(College of Information Engineering,Taiyuan University of Technology,Taiyuan 030024,China)

The functional requirements of SATA(Serial Advanced Technology Attachment)protocol physical layer is analyzed in this paper.On the Virtex-5 family of FPGA embedded RocketIO transceiver platform,it combines the characteristics of the internal structure with the protocol demand and designs the physical layer circuit based on the RocketIO.

RocketIO;SATA protocol;high-speed serial transmission

TP393.04

A

【本文獻(xiàn)信息】楊佳朋,張剛,郝敏.基于RocketIO的SATA物理層實(shí)現(xiàn)[J].電視技術(shù),2013,37(3).

國家自然科學(xué)基金項目(60772101)

楊佳朋(1988— ),碩士生,主研嵌入式與通信;

張 剛(1953— ),教授,博士生導(dǎo)師,主研視頻編碼與嵌入式系統(tǒng);

郝 敏(1988— ),碩士生,主研視頻監(jiān)控。

責(zé)任編輯:魏雨博

2012-06-29