Tilepro64多核處理器的軟件無線電平臺構建

王晟宇,黃芝平

(國防科學技術大學 機電工程與自動化學院,長沙410000)

引 言

無線通信是通信領域中最為活躍的部分,在各個方面都得到了廣泛的應用。但是,通信技術在給我們生活帶來便利的同時也帶來了很多困擾,我們需要面對的通信系統也越來越多。如果一種無線技術能配置一種無線設備應用于多種通信方式,比如可以用于蜂窩網的手機、衛星接收機,也可用于簡單的收音機、對講機,甚至是遙控器,這樣使得一種無線設備可以面對多種通信需要的技術前景是非常誘人的。軟件無線電正是針對這樣一種需求而提出的。對于多種調制模式的無線信號,經射頻接收和數字化之后都可以僅通過配置軟件來完成信號的解調、解碼等處理,這也符合軟件定義無線電的要求。

1 軟件無線電平臺簡介

軟件無線電平臺是指將模塊化、標準化和通用化的硬件單元以總線或交換方式連接起來構成通用平臺,通過在這種平臺上加載模塊化、標準化和通用化的軟件,實現各種無線通信功能的一種開放體系結構及技術。它擺脫了面向用途而完全依賴硬件的傳統無線電設計思路,通過一種模塊化的通用硬件平臺,把系統提供的業務從長期依賴于固定電路的方式中解放出來,利用軟件可編程、易修改和成本低的優勢,把無線通信技術水平提升到一個新的高度。

通常的軟件無線電系統如圖1所示,射頻信號經模擬前端耦合、放大、下變頻等操作,然后在中頻對信號進行數字化處理,解調、解碼等操作在數字信號處理器中進行。本設計中僅進行中頻信號的接收及其以后的工作。

圖1 軟件無線電接收平臺系統框圖

2 Tilepro64多核處理器簡介

Tilepro64處理器是一款完全可編程的高性能多核處理器,它內部集成了64顆高性能的處理器內核,采用高效的iMesh總線連接內核、內存與I/O接口。該處理器能夠采用標準C或C++語言編程。

Tilepro64有64個內核組成二維處理器陣列,每個內核都可單獨運行,也可與其他內核組成并行處理陣列。64個處理器內核組成8×8的二維結構,內核之間通過二維的iMesh網絡進行連接。

在進行應用設計時,內核的映射位置和數量需要根據需求來確定(如進行復雜數字視頻流處理和高強度網絡流處理時)。Tilepro64處理器在設計時就考慮到了單核處理能力、核心數量以及總體功耗之間的平衡,因此它能夠達到很高的單位功耗處理能力,即使在大規模復雜設計時也能夠應對自如。

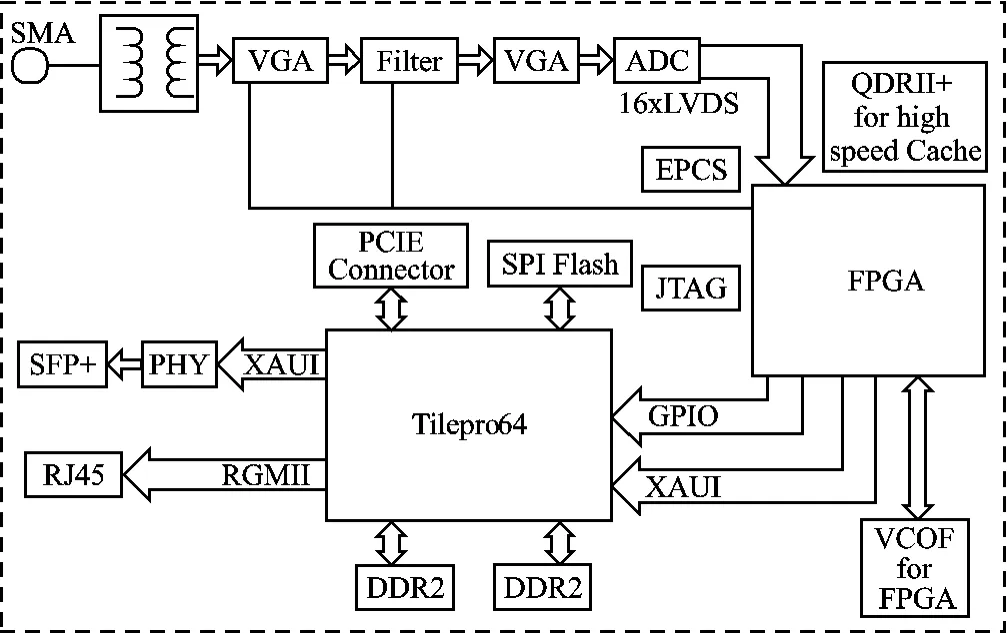

3 系統整體硬件設計

軟件無線電系統硬件架構如圖2所示,中頻信號經耦合、濾波、放大、模/數轉換,進入FPGA。FPGA作為數字前端對信號進行數字濾波和數字下變頻的處理。數字濾波有中值濾波法、算數平均值法、加權濾波法等。實現下變頻的功能框圖如圖3所示。完整的信號流程示意圖如圖4所示。

圖2 軟件無線電平臺硬件架構框圖

圖3 FPGA實現數字下變頻

下變頻以后基帶信號通過XAUI高速接口交由Tilepro64多核處理器處理。處理完畢后通過另外一個XAUI接口將數據發送到外部設備或者上位機。XAUI接口是一種引數器、自發時鐘串行總線,可達到10Gbps的有效數據速率,能滿足軟件無線電平臺中模擬信號數字傳輸的實時性要求。

4 Tilepro64多核處理器部分的軟硬件設計

4.1 硬件設計以及引導模式

Tilepro64處理器運行在125MHz的參考時鐘下,核心頻率可達700MHz,需要1.0V、1.8V、2.5V、3.3V等多種電壓來維持各個模塊的正常工作。內存模塊支持高達800 MHz數據速率的DDRII內存。本設計采用兩塊DDRII SODIMM內存條,共2GB容量。

多核處理器擁有多種引導模式,通過PCIe接口由計算機引導是最基本的一種,系統初步調試需要用PCIe進行,所以板卡上需要設計PCIe接口。另一種引導方式是基于SPI-ROM的,經過配置,系統上電后可以直接從SPI-ROM中獲取引導的二進制信息和上層的應用程序,具體軟件配置如圖5所示。Tilepro64具有兩個XAUI接口,一個用來與FPGA交互,另一個用來與外界交互。RGMII口既可以用來加載應用程序,也可以用來與外界通信。

圖4 信號流程示意圖

圖5 Tilepro64軟件配置流程

4.2 應用程序設計

應用程序方面,由于是無線信號未經解調直接數字化,模擬信號進行數字傳輸,在數字信號處理器中需要加入解調模塊。數字域解調靈活性比較大,只要完成判定,就可以采取多種判定模式。由于ADC輸出數據量較大,多核處理器采用多個核心以時分方式分別處理不同時序的數據(如圖6所示),每個核稱為一個Tile,再用一個獨立的核負責將多路數據按照時序重新組合。

內存在這個過程中發揮非常重要的緩沖作用,XAUI的速度很快,必須先將數據放入內存,才方便讀取。如果處理進行之中內存的數據溢出,便會導致數據的覆蓋或者丟失而無法完整地處理數據,所以內存必須足夠大。另外,每個核都可以與內存互相通信,并且都具有本地L1緩存和共用的L2緩存4MB,可以用來存儲小部分將要處理的數據。存儲空間的安排與運用、內存與緩存的交互是程序實現良好實時性的關鍵。

圖6 用多核處理器完成無線信號的解調、解碼處理

Tilepro64的64個處理器內核組成8×8的二維結構,通過不同的裁剪,多核處理器可以同時運行多個應用程序。在程序設計時,雖然每個核都可以與內存通信,但是根據拓撲結構,遠近不同的核與讀寫內存耗費的時鐘周期不同。數據若流經多個核,也會增加相應的時序延遲。所以,并行處理時要采用合適的陣列結構,以保證時序不會因為路徑長短不同而過度打亂,以利于接下來按時序重新組合。另外,外圍的某些核專門用于操控一些接口,比如XAUI和RGMII,當用到這些接口時這些核負責操控接口的輸入/輸出,不能同時進行其他處理,所以在配置陣列時應該避開。

經解調后的數字基帶信號,還需要進行解碼的操作。之后便可將數據發送至上位機或者外部存儲。由于是軟件控制,根據不同需要,Tilepro64之中可以加入更多的處理模塊。

結 語

多核處理器是一種新型的處理器,其并行處理能力在處理無線數字信號時可以得到充分的發揮,這是其他數字信號處理器所不具有的特性。基于多核處理器的軟件無線電平臺可以完整地完成無線信號接收、模/數轉換、解調、解碼的工作。利用其并行處理的性能,完成無線信號的處理,并用高速接口XAUI將數據送到上位機存儲。

應用程序方面,通過并行化的處理模式,利用多個核來同步解調數字化的模擬信號,保證了無線信號處理的較高實時性。

軟件無線電要求可以方便地重新配置應用程序來完成對不同格式信號的處理,本設計中通過RGMII用RJ45接口可以直接配置應用程序,從而重新配置過程通過網口進行,非常方便。未來還可以在Tilepro64的程序中加入判別功能,完成識別調制模式的功能,并針對性地解調。

[1]Tore Ulversoy.Software Defined Radio:Chanllenges and Opportunities[J].IEEE Communications Surveys & Tutorials,2010(12).

[2]Cummings M,Haryana S.FPGA in the Software Radio[J].IEEE Communications Magzine,1999(2).

[3]Tuttlebee Walter.Advances in software defined radio[J].IEEE Electronics Systems and Software,2003(2).

[4]栗欣,許希斌.軟件無線電原理與技術[M].北京:人民郵電出版社,2010.