FPGA 實現海德漢絕對式編碼器與上位機的智能通訊

陳 琳,鐘 文,韋慶情,潘海鴻,羅海國,黃炳瓊

(1.廣西大學,廣西南寧530004;2.廣西制造系統與先進制造技術重點實驗室,廣西南寧530004)

0 引 言

隨著現代工業快速發展,精密數控機床、工業機器人等工廠設備對伺服驅動系統提出越來越高的要求,準確測量控制對象的位置信息對提高伺服系統的控制精度十分重要[1]。光電編碼器具有精度高、慣量小、穩定性好等優點被廣泛應用于需要檢測角度的裝置和設備中,如回轉臺、數控機床、機器人等[2]。

絕對式編碼器作為一種融合數字技術的精密測角裝置,其輸出位置值和電機軸的位置一一對應,便于記憶和保存,且可實現快速、及時、準確的位置檢測與控制[3]。絕對式編碼器數據輸出方式一般采用串行通訊方式。EnDat 接口協議采用全雙工同步串行數據傳輸方式,具有連線簡單、傳輸速度快、抗干擾能力強等優點,通常作為海德漢編碼器、光柵尺的通用數據傳輸接口協議,并已成為行業標準[4]。海德漢公司提供專用數據處理芯片供用戶使用,即將海德漢絕對式編碼器輸出的串行信號輸送到上位機控制器中處理,但該芯片通常價格比較昂貴。為了實現EnDat 絕對式編碼器與上位機之間的通訊,提出采用FPGA 實現對EnDat (EnDat 2.1 和EnDat 2.2)絕對式編碼器通訊接口電路設計。

1 EnDat 接口協議介紹

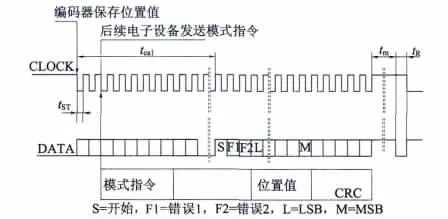

海德漢編碼器的雙向數字接口——EnDat 接口,不僅能給絕對式和增量式編碼器傳輸它們的位置值,而且還可以傳輸或更新在編碼器中所存儲的信息。EnDat 接口協議典型時序如圖1 所示[5],數據幀傳輸周期從時鐘信號CLOCK 的第一個下降沿開始,編碼器就開始保存測量值并且計算位置值;兩個時鐘信號周期后,編碼器接收后續電子設備發送的模式指令;經tcal時間后,編碼器從S 開始向后續電子設備進行數據的傳輸;圖1 中錯誤位F1 和F2一般只存在EnDat 2.2 指令中,它們是檢測類信號,表示編碼器發生可導致不正確位置信息的故障;編碼器從最低有效位(LSB)開始發送絕對位置值,直到發送完5 位循環冗余校驗碼(CRC),這才完成一個傳輸周期的數據幀傳輸。

圖1 EnDat 接口典型時序圖[5]

在數據幀結尾處,通常時鐘信號和數據信號必須被置為高電平,再經過tm時間后,數據信號由高電平變為低電平,維持低電平tR時間之后,時鐘信號才可以再次啟動新的一次數據傳輸。編碼器恢復時間tm通常為10 μs 到30 μs,但采用EnDat2. 2 接口的編碼器可通過參數設置將編碼器的恢復時間tm設置為1.25 μs 到3.75 μs;tR最大為500 ns。

2 EnDat 絕對式編碼器智能通訊接口設計

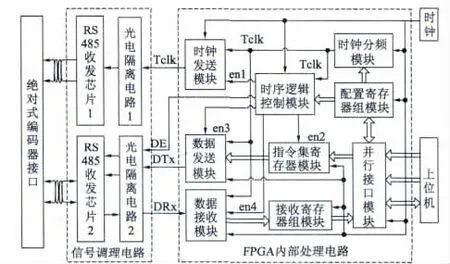

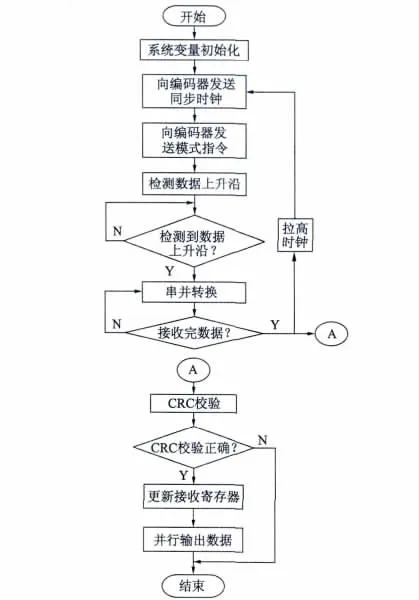

基于FPGA 芯片的EnDat 絕對式編碼器智能通訊接口結構框圖如圖2 所示。其包括絕對式編碼器接口、信號調理電路、FPGA 內部處理電路、上位機和時鐘。絕對式編碼器接口外接EnDat 絕對式編碼器;信號調理電路由RS-485 收發芯片1、RS-485收發芯片2、光電隔離電路1、光電隔離電路2 組成;以FPGA 芯片為核心,實現編碼器與上位機的智能通訊。在Altera 公司Quartus II 7.2 集成環境下運用硬件描述語言[6]Verilog HDL 編寫程序完成所設計的整個FPGA內部處理電路功能模塊(圖2):并行接口模塊、配置寄存器組模塊、時鐘分頻模塊、時序邏輯控制模塊、時鐘發送模塊、指令集寄存器模塊、數據發送模塊、數據接收模塊和接收寄存器組模塊,實現EnDat 絕對式編碼器輸出串行數據的解碼轉換等處理;其主程序流程圖如圖3 所示。

圖2 EnDat 絕對式編碼器通訊接口結構框圖

圖3 FPGA 內部處理電路的主程序流程圖

結合圖2 中對FPGA 中各個功能模塊闡述如下。

時鐘分頻模塊可以根據配置寄存器組模塊中的配置信息值,對輸入的時鐘信號進行分頻產生所需頻率的同步時鐘信號Tclk。

在可編程邏輯器件完成初始化后,時序邏輯控制模塊產生使能信號en1、en2、en3、en4 和DE。當使能信號en1 有效時,時鐘發送模塊接收同步時鐘信號Tclk,并將該同步時鐘信號Tclk 由光電隔離電路1、RS-485 收發芯片1 發送到絕對式編碼器接口;使能信號en2 有效時,指令集寄存器模塊根據并行接口模塊發送的指令選擇信號對指令集寄存器模塊中存儲的并行模式指令進行選擇,并將選擇的并行模式指令輸送給數據發送模塊;使能信號en3 有效時,數據發送模塊將指令集寄存器模塊輸出的并行模式指令轉換為串行模式指令DTx,該串行模式指令DTx 經光電隔離電路2 和RS-485 收發芯片2發送到絕對式編碼器接口;使能信號en4 有效時,數據接收模塊開始檢測經絕對式編碼器接口、RS -485 收發芯片2、光電隔離電路2 傳輸來的串行數據DRx 的上升沿,一旦上升沿到來說明接收到數據起始位S,啟動數據接收模塊接收串行數據DRx,并對該串行數據DRx 進行串并轉換和CRC 校驗,且將校驗正確的并行數據更新到接收寄存器組模塊;使能信號DE 用于控制切換RS-485 收發芯片2 的工作狀態。

由于EnDat 傳輸的數據類型分為位置值、位置值及附加信息或參數,且編碼器發送的數據類型由后續電子設備發送給編碼器的模式指令決定。因此,基于FPGA 所設計出的EnDat 絕對式編碼器智能通訊接口具有多種工作狀態,以滿足不同的數據幀格式要求。其工作狀態包括:讀編碼器位置值、讀編碼器位置值及附加信息、讀編碼器參數等。這些工作狀態可以由上位機通過并行接口模塊向配置寄存器組模塊寫入配置信息值:發送給編碼器同步時鐘的頻率信息值、編碼器傳輸位置值所需的時鐘脈沖數信息值等。這些配置信息值分別被傳送給時序控制模塊和時鐘分頻模塊進而產生相應的使能信號en1、en2、en3、en4、DE 和所需頻率的同步時鐘信號Tclk。

3 實驗與結果

根據圖2 搭建基于FPGA 的EnDat 絕對式編碼器智能通訊接口實驗平臺,如圖4 所示。伺服電機型號為SGMPH-01A1A21;海德漢絕對式編碼器型號是ECN1313,遵循EnDat 2.2 數字接口協議,絕對位置值為13 位;調理電路板實現海德漢絕對式編碼器輸出信號進行差分變單端、光電隔離等調理左右;采用EP1C6Q240C8 型芯片作為FPGA 板核心,根據圖1~圖3 編程實現智能通訊接口;實驗過程中用邏輯分析儀采集FPGA 輸出信號進行實驗結果分析。

圖4 EnDat 絕對式編碼器智能通訊接口實驗平臺

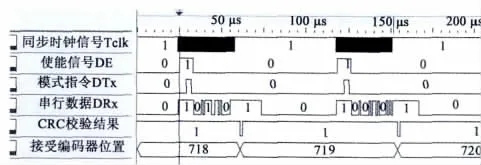

實驗中,編碼器智能通訊接口數據傳輸速率設定為1 MHz,數據采集結果如圖5 所示。圖5 中使能信號DE 為高電平時RS-485 收發芯片2 切換為發送狀態;當DE 為低電平時,RS-485 收發芯片2切換為接收狀態,FPGA 接收串行數據,并進行串并轉換和CRC 檢驗;當CRC 校驗結果為低電平表示一幀數據傳輸正確,并將該幀并行數據更新到接收寄存器組模塊。圖5 中接收到編碼器位置值以1 為基數遞增,表示伺服電機正方向旋轉。

圖5 實驗數據采集圖

上述實驗結果證明,所提出的基于FPGA 的EnDat 絕對式編碼器通訊接口設計方案可行,能夠完成對EnDat 絕對式編碼器輸出的串行數據進行串并轉換、CRC 校驗等處理,并可實現EnDat 絕對式編碼器與上位機之間的智能通訊。

4 結 語

根據海德漢公司EnDat 接口協議,采用Verilog HDL 語言設計出基于FPGA 的EnDat 絕對式編碼器智能通訊接口。通過實驗平臺驗證了所設計的智能通訊接口可完成對接收到的串行數據進行串并轉換、CRC 校驗等處理,實現EnDat 絕對式編碼器與上位機之間的通訊。此外該設計可通過改變FPGA內部配置寄存器組模塊中的配置信息值,進而改變接口工作狀態,可連接不同型號的EnDat 絕對式編碼器。這表明基于FPGA 的智能通訊接口具有很強的實用性,可以替代專用接口芯片,為實現通過上位機獲取電機準確的位置信息提供一種新的方法。

[1] 馬有良,任同.光電編碼器脈沖檢測電路設計[J].儀表技術與傳感器,2009(10):76-77.

[2] 劉琳,陳建平.通過ENDAT 接口獲取絕對編碼器位置[J].微電機,2009,42(12):77-79.

[3] 史敬灼,王秀麗,徐殿國.交流伺服系統光電編碼器信號處理電路設計與實現[J].微特電機,2007,35(11):18-19.

[4] Heidenhain.Endat 2.2 position encoder bi-directional interface[M].Heidenhain 公司,2011.

[5] Heidenhain.Endat 2.2 位置編碼器雙向數字接口[DB /OL].http:/ /www.haidenhain.com.cn.

[6] 夏宇聞.復雜數字電路與系統的Verilog HDL 設計技術[M].北京:北京航空航天大學出版社,1999.