基于SOPC的電網參數監測裝置的設計

周國棟,陳 迅,曹珍珍

(江蘇科技大學 電子信息學院,江蘇 鎮江 212003)

隨著用戶用電量需求的不斷增加,與各種大容量非線性負載的投入使用,使得電力系統的諧波污染越來越嚴重[1]。傳統電網監測裝置大多采用單片機,或基于數字信號處理器(DSP)及ARM處理器實現[2],這些系統開發周期長,系統升級困難,而采用MicroBlaze軟處理器的SOPC技術彌補了上述不足。

文中設計了基于Xilinx公司FPGA的SOPC電網參數監測裝置。該裝置將FPGA硬件邏輯具有的快速并行執行能力和MicroBlaze軟處理器的靈活性相結合,前者保證了數據處理的實時性,后者則實現了前者不易實現的功能。該監測裝置可實時監測三相電網電壓電流有效值、各次諧波含有率、有功功率、無功功率和功率因數等電網參數。

1 SOPC及MicroBlaze簡介

SOPC(System on a Programmable Chip),即可編程片上系統[3]。它是一種特殊的嵌入式系統,將CPU、存儲器、I/O口等系統設計所需要的功能模塊集成至一片FPGA芯片上,構成可編程的片上系統,完成傳統嵌入式系統所能完成的任務。SOPC設計靈活,具備軟、硬件系統均可在線編程的特性,因而系統升級容易。還可根據實際功能需求進行功能模塊的裁剪。它占用面積小,可騰出更多面積給電路板上的其它外圍電路使用。

MicroBlaze嵌入式軟核是一個被Xilinx公司優化過的可以嵌入在FPGA中的RISC處理器軟核[4]。它采用傳統的單處理器方法進行的基礎設計,配合Spartan-3E系列FPGA在80MHz的時鐘頻率下,性能達到 68 Dhrystone MIPS(DMIPS),運行速度快的同時占用資源少,可配置性強[5]。用戶可以從PPC405,PPC440和MicroBlaze這 3種內核處理器中選擇一款合適的處理器。PPC405和PPC440是內嵌在Xilinx高端FPGA中的硬核處理器,工作頻率更高,性能更佳,靈活性稍差;MicroBlaze是軟核處理器,一般用于低成本的FPGA上,較之前者工作頻率較低,性能稍差,但靈活性很強。除此之外,用戶還可以從多個已經歸類的外設IP核和用戶自定義IP核中進行選擇 (IP核指具有知識產權的集成電路設計模塊),以構成可裁剪的SOPC系統。

2 監測裝置總體設計

監測裝置主要由信號調理電路、過零檢測電路、鎖相倍頻電路、模數轉換(A/D)電路、FFT運算單元、CPU處理單元、LCD顯示、鍵盤等模塊構成。實現對三相電壓電流有效值、有功功率、無功功率、功率因數和各次諧波含有率等參數的測量與本地顯示及數據傳送。

三相電壓三相電流六路信號,經電壓互感器、電流互感器變換,經信號調理電路(轉換、濾波、電平值提升)處理后,提供給模數轉換芯片ADS7864進行采樣和轉換。在信號調理電路中經濾波后的信號,提供給過零檢測電路,輸出的方波經鎖相倍頻電路,輸出的信號作為ADS7864開始工作的觸發信號。

諧波參數的計算采用傅立葉變換算法 (FFT)實現,該FFT算法由Xilinx公司成熟的FFT IP核完成。該FFT IP核由 ISE(Xilinx軟件集成開發環境)工具 Core Generator,根據計算精度需求和芯片邏輯資源,綜合判斷后配置生成。在50 MHz的時鐘頻率下,完成一次512點的FFT運算只需要65.7μs,可實時在線計算六路電網信號的諧波。

FFT處理后的數據存入輸出雙口RAM,當六路信號的FFT計算完畢存入輸出雙口RAM后,產生一個外部中斷,通知MicroBlaze軟處理器來取走數據,做一些簡單的數據算術處理。最后將處理結果送給本地LCD顯示,或通過RS-232傳給上位機做進一步的數據分析與處理。監測裝置原理圖如圖1所示。

圖1 監測裝置總體結構框圖Fig.1 Overall structure diagram of monitoring device

3 硬件電路設計

3.1 信號預處理電路

AD轉換芯片只可接受其可接受量程范圍內的信號,因而在信號采樣前須對輸入信號做必要的預處理,主要包括信號隔離轉換電路,濾波電路,電平值提升電路。信號隔離轉換電路完成強電轉換成弱電的過程,濾波電路濾除電網高次諧波,以免造成后期信號處理時出現頻譜混疊,而電平提升電路,將電平值提升至ADS7864可接受的電平值。另外,電網頻率在50 Hz上下波動,為了使AD芯片能在均勻時間間隔內對輸入信號進行采樣,須進行頻率跟蹤,以免頻譜泄露。經過濾波電路后輸出的電壓信號,通過過零檢測電路和鎖相倍頻電路實現頻率跟蹤技術,實時準確地采樣和轉換輸入信號。

3.2 A/D轉換模塊

A/D芯片采用德州儀器TI公司的ADS7864,它內含兩個12位,2μs的逐次比較型模數轉換器,6個全差分采樣保持放大器[6]。ADS7864具有6個模擬輸入通道,被分為3組(A,B和 C),每個 A/D 轉換器對應 3 個輸入 A0、B0、C0和 A1、B1、C1,能同時進行采樣和轉換。將三相電壓分別接至A0、B0和C0,三相電流分別接至A1、B1和C1。每組輸入對應一個控制信號nHOLDA,nHOLDB和nHOLDC,將這3個控制信號接到一個控制信號nHOLDX上,可以允許6個通道同時采樣。通過拉低控制信號nHOLDX至少15 ns,轉換開始。轉換過程中,輸出信號nBUSY將會出現3個負脈沖,分別表示每組數據轉換完成。6個通道的轉換結果分別保存在6個輸出寄存器上。拉低讀取信號nRD和片選信號nCS來讀取寄存器并行輸出總線上的數據。輸出值由16 bits組成,最高位為’1’表示數據有效,接著3 bits用來標示6個通道,低12 bits為轉換值。輸出寄存器數據讀取模式有3種:單通道讀取,循環讀取和FIFO模式,通過控制信號線A0,A1,A2實現。本設計采用循環讀取模式,第一個負脈沖nRD到來時讀取A0寄存器值,第二個負脈沖nRD到來時讀取A1寄存器值,以此類推,循環讀取 B0、B1、C0和 C1寄存器值。

根據ADS7864 datasheet上的工作時序圖,編寫狀態機控制。該狀態機控制器用HDL硬件描述語言綜合實現。圖2為通過ISE片內邏輯分析儀工具ChipScope捕捉到的該控制器的實際工作波形。控制過程如下,在系統復位reset信號下,狀態機進入初始化狀態,設置讀取模式等參數,然后無條件進入IDLE狀態等待轉換。當FPGA內的邊沿檢測模塊檢測到鎖相倍頻電路的輸出信號PLLCLK的上升沿時,產生一個負脈沖送給nHOLDX,轉換開始,進入轉換狀態。nBUSY信號出現第一個負脈沖表示第一組通道A0和A1轉換完成,第二個負脈沖表示第二組通道B0和B1轉換完成,第三個負脈沖表示第三組通道C0和C1轉換完成。對nBUSY負脈沖計數,達到3時Flag_nBUSY_Ov產生一個脈沖表示所有通道轉換完成。接著狀態機進入讀取狀態,由于事先將byte信號接至高電平,為字節讀取模式,因此6個通道的轉換值需要讀取12次。在12個nRD負脈沖作用下,AD_Data出現了12個字節數據,依次構成6個通道的高低位部分。當Flag_nRDv由0變為1時讀取完成,回到IDLE狀態,等待觸發信號PLLCLK上升沿的到來。

圖2 ADS7864采樣控制器的實際波形Fig.2 Actual waveform of ADS7864 sampling controller

3.3 FPGA電路

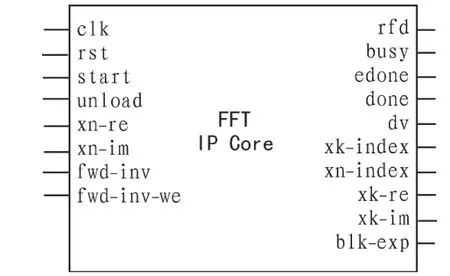

諧波參數通過FFT算法計算,該算法使用Xilinx邏輯IP核FFT IPCore實現,該IP核是經過成功驗證的高性能低功耗的集成設計模塊,能高效進行離散傅里葉變換[7]。FFTIPCore的I/O數據流采用基-2 Burst I/O結構,設置點數為512點,數據格式為定點,數據輸出順序為自然順序。如圖3所示,為FFT IPCore例化模塊方框圖。

圖3 FFT IPCoreFig.3 FFT IPCore

如圖4所示,A/D控制器控制外部ADS7864采樣轉換數據,將轉換值讀取至輸入雙口RAM。內部讀寫邏輯控制模塊通過控制FFT讀取輸入雙口RAM中的數據計算諧波,當FFT計算完畢,內部讀寫邏輯控制模塊將FFT計算結果存入輸出雙口RAM。另外,ADS7864采樣的三相電流電壓原始值通過一個數據通道存入輸出雙口RAM,以供后續計算電流電壓有效值、有功功率、無功功率和功率因數等。MicroBlaze嵌入式系統總線PLB上掛有Bram控制器 (BRAM CNTLR),BRAM CNTLR的一端與PLB總線連接,另一端與輸出雙口RAM連接。當輸出雙口RAM中的數據準備好后,以中斷方式通知MicroBlaze處理器取數據,MicroBlaze通過操縱BRAM CNTLR的地址指針來讀取輸出雙口RAM中的數據,然后進行一些算術運算,求三相電流電壓有效值、各次諧波含有率、有功功率和無功功率等參數,最后將求得的結果送給本地LCD顯示或通過RS232總線送給上位機進行進一步數據分析與計算。

3.4 鍵盤和顯示單元

圖4 FPGA電路圖Fig.4 Circuit of FPGA

鍵盤、顯示單元負責人機對話。MicroBlaze處理器將處理后的數據送給LCD,實時顯示參數信息。LCD型號采用LCD1602,該LCD只需7根信號線進行控制,這7根控制信號線分別為讀寫控制信號RW,數據/指令識別信號RS,使能信號E,4位數據總線DB0-DB3。在Xilinx的XPS嵌入式開發平臺上通過CIP(Create or Import Peripheral)工具設計用戶自定義LCD IP核,在該IP核參數配置選項中勾選一個8位的軟件寄存器,低四位對應4位數據總線,高四位對應控制線。由于用戶自定義IP核不是Xilinx公司提供的現成IP核,所以需要自己編寫相應的驅動程序供應用程序調用[8]。例如,編寫LCD初始化函數,清屏函數,文本設置函數等。根據LCD1602讀寫時序,由MicroBlaze控制寄存器進行數據顯示。通過鍵盤按鍵操作來切換屏幕顯示不同相電力參數值。

4 監測裝置軟件設計

軟件部分包括FPGA HDL程序和MicroBlaze嵌入式C程序。HDL程序在Xilinx集成開發環境ISE中完成,使用Verilog HDL硬件描述語言編寫代碼,并編寫相關測試代碼進行功能驗證[9-10]。Verilog HDL硬件模塊由以下幾部分構成:A/D采樣控制器模塊、FFT IPCore模塊、輸入雙口RAM與輸出雙口RAM模塊和內部邏輯讀寫控制模塊,這些硬件模塊在系統時鐘節拍的驅動下按照邏輯時序有序運行。首先A/D控制器將ADS7864轉換后的數據送入輸入雙口RAM,通過內部讀寫控制邏輯將輸入雙口RAM中的數據送給FFT運算,處理的結果以中斷的方式通知MicroBlaze處理器讀取。

MicroBlaze從輸出雙口RAM獲得數據后,用C語言編寫代碼計算三相電壓有效值、電流有效值、各次諧波含有率、有功和無功功率等參數。MicroBlaze軟件設計采用模塊化設計方法,由初始化模塊、數據計算模塊、通信顯示模塊等構成。采用模塊化設計提高了程序可讀性,并且利于今后擴展和維護。Xilinx嵌入式軟件開發環境SDK具有完整的軟件開發流程,既有標準的C/C++編程界面也有豐富的調試界面。既可以選擇 XMD(Xilinx MicroBlaze Debugger)命名行調試,也可以選擇GND(GNU Debugger)代碼界面調試(設置中斷點、單步和連續運行等)。選擇GND方式調試時,XMD扮演中間媒介角色,一端連接GND,另一端通過JTAG電纜連接掛在MicroBlaze系統總線上的MDM(MicroBlaze Debugger Module)模塊,實時在線調試系統。參數計算結果既可以送給本地LCD顯示,也可以通過RS232傳給上位機做進一步數據分析與計算。MicroBlaze軟件程序流程圖如圖5所示。

圖5 MicroBlaze軟件程序流程圖Fig.5 Flow chart of MicroBlaze software program

5 結 論

MicroBlaze是一個功能強大,應用靈活的嵌入式軟處理器,特別是其強大的用戶自定義IP核功能,極大地方便了系統設計。基于嵌入式軟處理器的SOPC開發方法,將擁有廣闊的應用前景。本文采用FPGA邏輯設計與MicroBlaze軟處理器相結合的方法設計了電網參數監測裝置,基于該裝置,可以實時在線監測三相電網電壓、電流、諧波、有功功率、無功功率等參數。

[1]德拉羅薩.電力系統與諧波分析[M].趙琰,孫秋野,等譯.北京:機械工業出版社,2009.

[2]沈偉,謝拴勤.基于DSP的電能質量監測系統設計[J].計算機測量與控制,2008,16(9):1240-1242,1261.SHEN Wei,XIE Shuan-qin.Design of power quality monitor system based on DSP[J].Computer Measurement&Control,2008,16(9):1240-1242,1261.

[3]楊強浩.基于EDK的FPGA嵌入式系統開發[M].北京:機械工業出版社,2008.

[4]Xilinx.MicroBlae Processor Reference Guide[EB/OL].(2012).[2013].http://www.xilinx.com.

[5]Xilinx.Spartan-3E FPGA Family Data Sheet.[EB/OL].(2012).[2013].http://www.xilinx.com.

[6]TI.ADS7864數據手冊.[EB/OL]. (2005)[2013].http://www.ti.com.cn/product/cn/ads7864.

[7]趙永新,夏榮,羅衛湘,等.基于高性能FPGA的快速并行FFT及其在諧波監測上的應用[J].制造業自動化,2008,30(8):82-83.ZHAO Yong-xin,XIA Rong,LUO Wei-xiang,et al.The highspeed collateral FFT of high-powered FPGA and its application on harmonic waves monitor[J].Manufacturing Automation,2008,30(8):82-83.

[8]Xilinx.Device Driver Programmer Guide[EB/OL].(2012).[2013].http://www.xilinx.com.

[9]王鈿,卓興旺.基于Verilog HDL的數字系統應用設計[M].北京:國防工業出版社,2007.

[10]吳繼華,王誠.設計與驗證 Verilog HDL[M].北京:人民郵電出版社,2006.