基于EDA技術的PS/2接口電路設計

王 勇 宋 瀟 孫孟方

(1.河南科技大學電氣工程學院,河南 洛陽 471023;

2.中國航空工業集團公司洛陽電光設備研究所,河南 洛陽 471009)

基于EDA技術的PS/2接口電路設計

王 勇1宋 瀟1孫孟方2

(1.河南科技大學電氣工程學院,河南 洛陽 471023;

2.中國航空工業集團公司洛陽電光設備研究所,河南 洛陽 471009)

基于EDA技術,使用FPGA芯片和VHDL語言,設計了一種PS/2設備接口電路。介紹了硬件連接、通信協議、設計過程及仿真結果。采用自頂向下的設計思路,充分發揮EDA技術的優勢,大大縮短了設計周期。軟件仿真及硬件調試表明,設計中的各個模塊之間能夠正確地傳送數據,性能穩定,達到了預期目標。

PS/2接口;FPGA;VHDL;通信協議

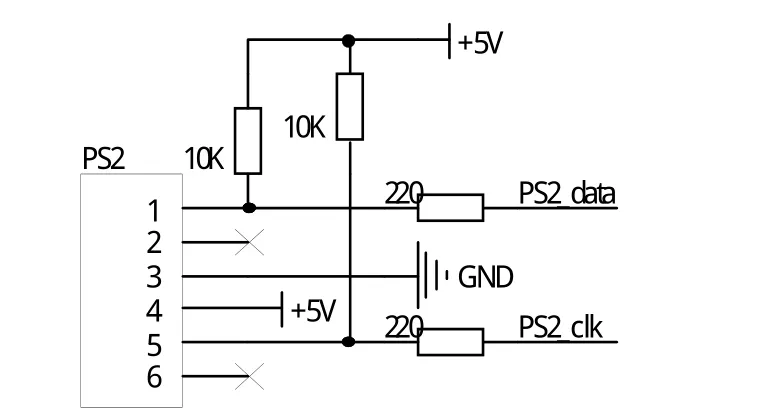

圖1 PS/2接口外圍硬件電路

1.引言

PS/2作為常用的人機接口,在嵌入式系統中有著廣泛應用。例如PS/2鍵盤內含自動去抖功能,軟硬件開發簡便,價格便宜,通用性強[1]。基于FPGA的EDA技術在近些年發展迅速,正逐漸成為電子系統設計的主流,設計人員利用它可以設計出自定義功能的專用集成電路,縮短了開發周期,降低了開發成本。FPGA還具有靜態可重復編程和動態在系統重構的特性,使得硬件功能可以像軟件一樣通過編程來修改。VHDL主要用于描述數字系統的結構、行為、功能和接口,除了含有具有硬件特征的語句外,其語言形式、描述風格與句法類似于一般的計算機高級語言。VHDL程序的結構特點是將一項工程設計分成外部接口部分和內部結構部分,一旦內部開發完成,其它的設計可以直接調用這個實體。因此采用VHDL硬件描述編程語言,在FPGA系統中嵌入PS/2設備接口電路,在產品開發中是可行和必要的。

2.PS/2接口及通信協議

2.1 PS/2接口

物理上的PS/2接口有兩種連接類型,即5腳的DIN和6腳的MINI-DIN。實質上,這兩種類型都只有4個腳有意義,它們分別是1腳數據(data)、3腳電源地(GND)、4腳電源(VCC)和5腳時鐘(clk)。在PS/2設備與主機的物理連接上只要保證這四根線一一對應即可。PS/2設備靠主機提供+5V電源,另外兩個腳clk和data都是集電極開路的,需要在外圍硬件設計上進行上拉,相應電路如圖1所示。

2.2 通信協議

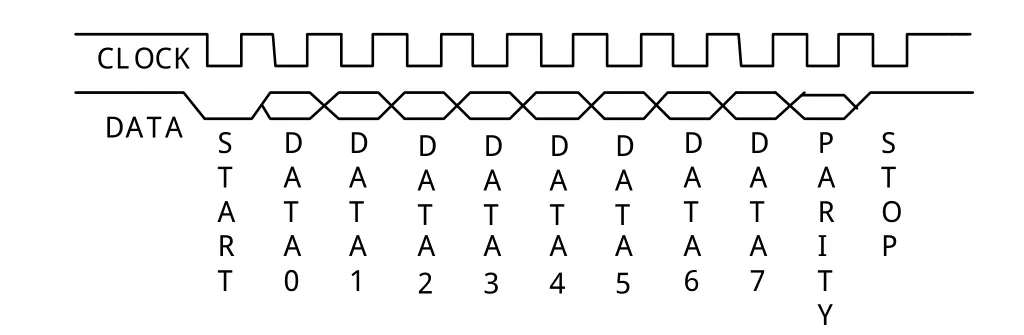

PS/2接口遵循一種雙向同步串行通信協議。PS/2設備可以發送數據到主機,主機也可以發送數據到PS/2設備,主機在總線上有優先控制權,它可以在任何時候抑制來自于PS/2設備的通信。PS/2設備發送到主機的數據在時鐘信號的下降沿被讀取;主機發送到PS/2設備的數據在上升沿被讀取。不管通信的方向怎樣,PS/2設備總是產生時鐘信號,最大的時鐘頻率是33KHz,一般設計為15KHz左右。通信數據安排在字節中,每個字節為一幀,包含了11或12位,如圖2所示。其中第1位是起始位(低有效),緊跟8個數據位(低位在前),第10位為校驗位(奇校驗),第11位為停止位(高有效),第12位為應答位(僅用在主機對設備的通信中)。若數據中包含偶數個“1”,校驗位置“1”;若數據中包含奇數個“1”,校驗位置“0”。數據位中“1”的個數加上校驗位為奇數,這可用來檢測傳輸過程是否有錯。當主機發送數據給PS/2設備時,設備回送一個信號來應答數據包,表示已經收到,該位不會出現在設備發送數據到主機的過程中。下面以設備到主機的數據傳輸過程為例闡述PS/2的通信過程[2]。

當PS/2設備等待發送數據時,它首先檢查時鐘以確認它是否為高電平,如果不是,則說明主機抑制了通信,設備必須緩沖任何要發送的數據直到重新獲得總線的控制權;如果時鐘此時為高電平,設備則可以傳送數據。每位在時鐘的下降沿被主機讀入,通信時序如圖2所示。當時鐘為高時,數據線改變狀態,在時鐘信號下降沿,數據被鎖存。從時鐘脈沖的上升沿到一個數據傳送的時間至少需要5μs。數據變化到時鐘脈沖的下降沿的時間也至少需要5μs,這個定時應該嚴格遵循。在停止位發送后,設備在發送下一幀數據前至少應該等待50ms,這是因為主機在處理接收字節時抑制了發送。

圖2 PS/2設備到主機通信時序

2.3 PS/2設備返回值介紹

PS/2設備(以鍵盤為例)的處理器如果發現有鍵被按下或釋放將發送掃描碼信息到主機。掃描碼有兩種不同的類型:通碼和斷碼。當某鍵被按下則發送通碼,當該鍵被釋放則發送斷碼,每個按鍵被分配了唯一的通碼和斷碼。這樣主機通過查找掃描碼就可以識別按鍵。一整套的通斷碼組成了掃描碼集,目前常用的有三套標準的掃描碼集,現代的PS/ 2鍵盤幾乎均默認使用第二套掃描碼。設計者不用總是通過查表來找出按鍵的斷碼,在通碼和斷碼之間存在著必然的聯系。多數第二套斷碼有兩字節長,第一個字節是F0H,第二個字節是這個鍵的通碼值。擴展按鍵的斷碼通常有三個字節,前兩個字節是E0H、F0H,最后一個字節是這個按鍵通碼值,每個按鍵具體的通斷碼值可查閱相關的碼表,這里不再贅述。

3.PS/2接口的VHDL硬件實現

設計的PS/2接口模塊的主要功能是將輸入的PS/2按鍵值轉換成掃描碼,并最終轉換成ASCII碼輸出,同時要求能夠響應PS/2鍵盤上的所有按鍵,包括基本按鍵和擴展按鍵,頂層實體如圖3所示。模塊內部用VHDL語言編寫,用系統時鐘掃描PS/2設備時鐘線的變化,接收數據線上的數據,然后按照PS/2的通信協議進行解析,并暫存解析后的8位數據。另一方面需要對接收到的數據的判斷,判斷它是通碼還是斷碼,最后將斷碼進行格式轉換,對于字母和數字,程序將斷碼通過譯碼程序轉換成ASCII碼,以備后續使用。在進行PS/2接口模塊設計時需要注意以下兩點:

(1)PS/2的時鐘線需要多次鎖存

設計中發現,需要對PS/2的時鐘線進行多次鎖存,否則可能出現鍵值識別錯誤。在調試過程中將時鐘進行兩級鎖存,發現按鍵識別時誤碼比較嚴重,時鐘線在每次按鍵時都會隨機地產生多余的干擾脈沖,使程序檢測到的時鐘數多出幾個,造成無法連續識別。當將時鐘進行十級鎖存后,誤碼率顯著降低,問題得到解決。

(2)兼容基本按鍵和擴展按鍵

PS/2鍵盤上的基本按鍵和擴展按鍵發送的鍵碼格式不同,但是對鍵盤掃描的結果需要輸出統一的格式,這就需要對數量較少的擴展按鍵做特殊處理。設計時發現,擴展按鍵斷碼的最后一個字節和基本按鍵的并沒有沖突,簡單的做法是忽略它的第二個字節E0H,將鍵碼格式看成和基本按鍵的相同,當檢測到通碼F0H,則使能標志位,將其后的鍵碼取出進行解析即可[3]。

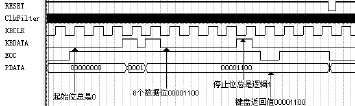

圖3PS/2模塊

模塊中KBCLK是時鐘信號,KBDATA是按鍵的輸入值,PDATA是輸出掃描碼,功能仿真結果如圖4所示。由圖4可以看出,當RESET為低電平時,執行清零操作;根據PS/2協議的數據幀格式,第1位起始位,并總是邏輯‘0’,接下來的8位是數據位,低位在前,接下來1位是停止位,總是邏輯‘1’,圖中的鍵盤輸入KBDATA值是0001100001,PS/2設備返回值PDATA是00001100,說明按鍵識別正確。

圖4 時序仿真波形圖

4.結束語

采用現場可編程門陣列FPGA設計了一種PS/2設備接口電路,該電路主要由分頻模塊、通信協議控制模塊、譯碼模塊等組成。PS/2設備的數據輸入通過外圍接口單元進入FPGA內部,經過控制與解析生成ASCII碼輸出,從而方便后續按鍵處理程序使用。程序采用VHDL語言編寫,具有較強的功能可移植性。FPGA芯片選用Altera公司的成熟產品EP2C8Q208,充分利用了其高速、大容量、組合靈活等優點,并使用QuartusⅡ開發環境所提供的庫資源,最大限度地發揮FPGA的優勢,大大簡化了系統設計,縮短了設計周期。軟件仿真及硬件調試表明,設計中的各個模塊能夠正確地進行數據傳送,工作性能穩定,達到了預期目標。

[1]魏軍輝,王福源,周子昂等.基于FPGA的PS/2鍵盤接口的設計[J].微計算機信息,2008,24(26):138-140.

[2]李攀峰.基于SOPC技術的PS/2鍵盤接口電路設計[J].自動化與儀器儀表,2012,6:139-141.[3]劉昌華.數字邏輯EDA設計與實踐[M].北京:國防工業出版社,2005.

Design of PS/2 Interface Circuit Based on EDATechnology

Wang Yong1Song Xiao1Sun Mengfang2

(1.Henan University of Science and Technology,Luoyang 471023,Henan;

2.Luoyang Research Institute of Electro-Optical Equipment ofAVIC,Luoyang 471009,Henan)

A PS/2 interface circuit is designed based on FPGA chip and VHDL language.Hardware connection,communication protocol,design process and simulation result are introduced.Using the top-down design ideas,giving full play to the advantage of EDA technology,the design greatly shortens the design cycle.Software simulation and hardware debugging demonstrate that data can be transmitted accurately between the modules in the design and the system runs normally.

王勇,男,河南淮濱人,碩士,講師,研究方向:應用電子電路開發與設計。

河南省教育廳科學技術研究重點項目,項目編號:14A510003;河南省教育廳自然科學研究項目,項目編號:13A510263。

【 Keywords】 PS/2 interface;FPGA;VHDL;communication protocol