基于DSP和FPGA雙CPU架構的導航微機系統

高延濱,劉輝煜,何昆鵬,張興智

哈爾濱工程大學自動化學院,黑龍江哈爾濱 150001

基于DSP和FPGA雙CPU架構的導航微機系統

高延濱,劉輝煜,何昆鵬,張興智

哈爾濱工程大學自動化學院,黑龍江哈爾濱 150001

為了滿足慣性系統的小型化發展,設計了一種體積小、功耗低、價位低的高性能導航微機系統。此導航微機系統由TI公司數字信號處理器芯片TMS320C6726和Altera公司的FPGA芯片EP3C10E144A7兩種CPU組成,DSP主要負責導航數據處理和算法運算,FPGA主要負責慣性測量單元(IMU)的數據采集和接口控制。該微機系統充分利用了TMS320C6726的運算速度快、浮點數據處理能力強和FPGA的SOPC技術的特點,通過VHDL語言編程實現雙口RAM接口完成雙CPU的快速數據通信。兩種CPU能分別發揮自身優勢,協調地工作,提高了導航計算機的運行效率。

導航微機系統;信號處理器;雙CPU;雙口RAM;捷聯解算

隨著捷聯慣性導航技術的成熟及其在無人機上的應用,促使捷聯慣性導航系統向低成本、小體積和低功耗方向發展。捷聯式導航系統采集信號種類多,算法較復雜,因此導航計算機需要有豐富的接口和快速的數據處理能力。傳統的導航計算機大多為專用計算機、通用計算機平臺、嵌入式工控機(PC104)等,它們體積大、功耗大、價格高,不適用于小型制導場合[1]。近年來,隨著各種嵌入式處理器的發展,出現了運算能力強大的數字信號處理器和可編程的邏輯器件。數字信號處理器(DSP)是專為高速數據處理而設計的微處理器,其改進的哈佛結構、先進的多地址/數據總線和多級流水線機制、專用的硬件乘法器和高效的指令集使芯片的指令周期降到10 ns以下;先進的制造工藝使其功耗僅有數十毫瓦;其體積通常在25 mm×25 mm左右。現場可編程門陣列(FPGA)具有編程方便靈活、集成度高、處理速度快、低功耗、高性價比、可靠性高等優點。在此,結合DSP和FPGA各自的特點,設計一種主從式、雙處理器體系結構,適用于小體積、低功耗和低成本捷聯慣性導航系統[2]。

1 導航微機系統的總體設計

導航微機系統主要有2個功能:一是數據的輸入和輸出,包括采集慣性器件的輸出信號,接收上位機的校正信息、初始對準信息和控制信息,輸出解算后的導航參數[3]。二是數據處理和計算,包括初始對準、導航解算、在線校正、誤差補償和濾波等。這就要求導航計算機有較強的數據處理能力和靈活的控制功能。對于后者是DSP的優勢所在,可以很好的完成。但是對于前者,和外界進行大量的數據交換和外圍設備的控制則是DSP的弱項,勉強令其完成,則其賴以進行高速數據處理的多級緩沖和高速流水線機制將被頻繁打斷,最終使DSP的優勢無法發揮[4]。

FPGA是隨著微電子設計技術和工藝的發展而產生的一種現場可編程邏輯門陣列。它通用性強,可根據用戶不同的需求實現特定的功能,內部有大量的觸發器和I/O接口,采用高速CHMOS工藝,大大降低了芯片的功耗,擴充接口和增加控制單元只需FPGA內部資源滿足即可,不再會有新增元器件和擴大計算機體積的額外負擔,這些特點恰好符合導航計算機的多接口,多流程控制以及小型化的需求,可以和DSP進行優勢互補。做為導航計算機中的外設通信和控制單元,負責數據傳輸和流程控制,DSP則只用來導航算法處理,這樣能使導航計算機的體積指標和整體性能得到提高。

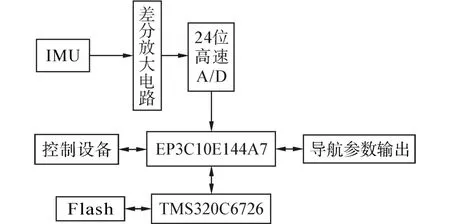

本系統設計以發揮DSP和FPGA的最佳性能為原則,DSP完成導航的算法處理,FPGA完成慣性器件的數據采集和簡單的處理,比如剔除野值,平滑濾波等,系統和外界所有的通訊都由FPGA負責,總體結構如圖1所示。

圖1 總體結構

2 數據處理系統的設計

2.1 數據采集系統設計

數據采集負責導航系統中所有信號的輸入,主要包括陀螺、加速度計、里程計和GPS的信號輸出。根據信號的格式不同,需要設計不同的接口電路:里程計和GPS的信號輸出通常為串行模式,利用Al-tera公司提出來的SOPC方案,即在FPGA上嵌入NiosII軟核處理器,通過UART內核接收數據提供給NiosII軟核處理器。陀螺和加速度計的輸出一般分為數字脈沖和模擬電壓2種,如果輸出是數字脈沖,可以在軟核上設計一個高精度頻率采樣系統[5],這樣的設計比一般的計數器設計可靠性高;如果慣性測量單元(IMU)輸出是模擬電壓,則需要一個A/D電路把模擬電壓轉換成數字信號,A/D電路做為信號進入FPGA的前端,關系到IMU信息的準確性和可信度。本系統是針對模擬電壓輸出設計的,根據系統的精度要求,選用了Linear公司的24位高速差分A/D芯片LTC2440。

LTC2440是一款只有5 μV偏移的高速24位無延遲增量累加模數轉換器,它是SPI接口輸出,采用專有的增量累加型架構,實現了無延遲的可變速度和分辨率。10種速度/分辨率組合可通過一個簡單的串行接口來設置,也可以通過把單個引腳連接至高電平或低電平來輕松地選擇一種快速超低噪聲速度/分辨率組合。轉換的準確度和器件的功耗與所選的速度無關,但是輸入電壓變化范圍較小,只有±2.5 V。為了擴大LTC2440的電壓輸入范圍,在電路前端加一個全差分衰減放大器AD8475,可提供精密衰減0.4倍,慣性器件的輸出可以擴大到±5 V以上。由于慣性器件的輸出有高頻噪聲,需要插入一個前置采樣濾波器,將前置采樣濾波器的帶寬設置為采樣頻率的1/3,并在FPGA中對數據進行滑動平均濾波,以上的設計能很好的保證數據的精度和實時性。

2.2 DSP處理器的外圍電路設計

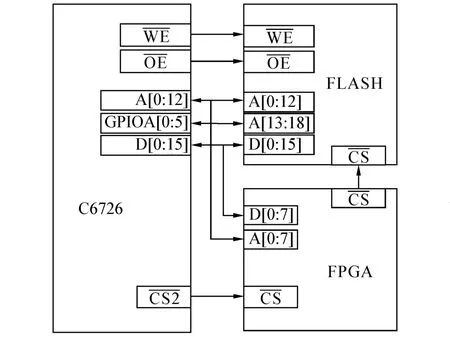

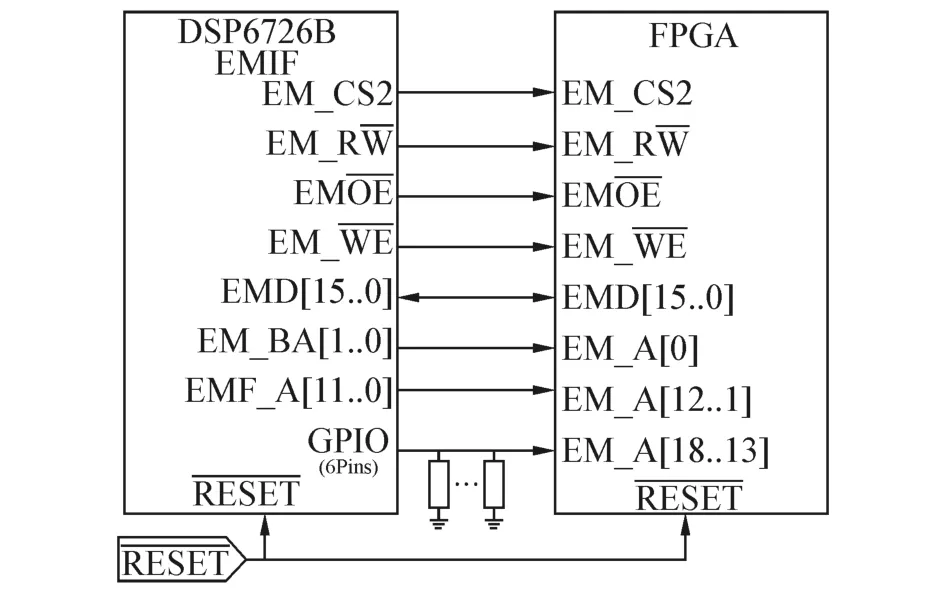

本系統DSP選用TMS320C6726處理器,C6726支持32位單精度浮點和64位雙精度浮點運算[6],在系統中負責導航解算的功能。設計了DSP的最小系統,其外圍電路控制主要就是Flash讀寫操作和與FP-GA的數據通訊,如圖2所示。

圖2 DSP最小系統及外圍電路

在本設計中,FPGA與DSP的通信是通過雙口RAM來實現的。在FPGA內部設計雙口RAM,雙口RAM的地址線和數據線連接到DSP的EMIF接口上,同時Flash也連接到EMIF接口上,這樣就涉及到共用地址線和數據線的問題。在本設計中,在FPGA內部使用VHDL硬件描述語言設計邏輯電路,通過DSP的GPIO控制片選信號連接到RAM上或Flash上。DSP與Flash和FPGA的接口如圖3所示。

圖3 Flash與DSP接口

2.3 FPGA的基礎平臺設計

FPGA的主要任務是將A/D轉換后的數據進行采集并將數據發送給DSP進行解算。在Altera公司提供的Quartus II軟件中利用Qsys,即可進入Nios II軟核定制設計界面。基于SOPC的設計中,Nios II處理器、SDRAM控制器、EPCS控制器、SYSTEM ID和JTAG UART內核是系統運行最基本的定制,其他的內核都是根據所設計系統的需求而進行的定制[7]。在本設計中,使用的都是系統自帶的內核。

3 DSP與FPGA數據傳輸

隨著FPGA的應用越來越廣泛,Altera公司的Qsys嵌入式系統中添加了為外設進行預留接口的功能。因此本文設計了一種基于Qsys的雙口RAM與DSP6726的EMI外部存儲器擴展接口,雙口RAM可用于提高 RAM吞吐率,用于實時數據緩存[8-9],實現了DSP6726與NiosII軟核之間導航數據的交互傳輸。

3.1 基于Qsys的雙口RAM

Qsys是Altera公司在Quartus II 11.0版中開始發布的系統集成工具,它在SOPC Builder基礎上實現了新的系統開發特性,提高了FPGA設計者的工作效率。Qsys系統內部處理器和外設之間遵循Avalon交互式總線。Avalon交互式總線在Qsys系統生成中自動完成,包括Avalon外設、Avalon信號和Avalon端口3部分[10]。

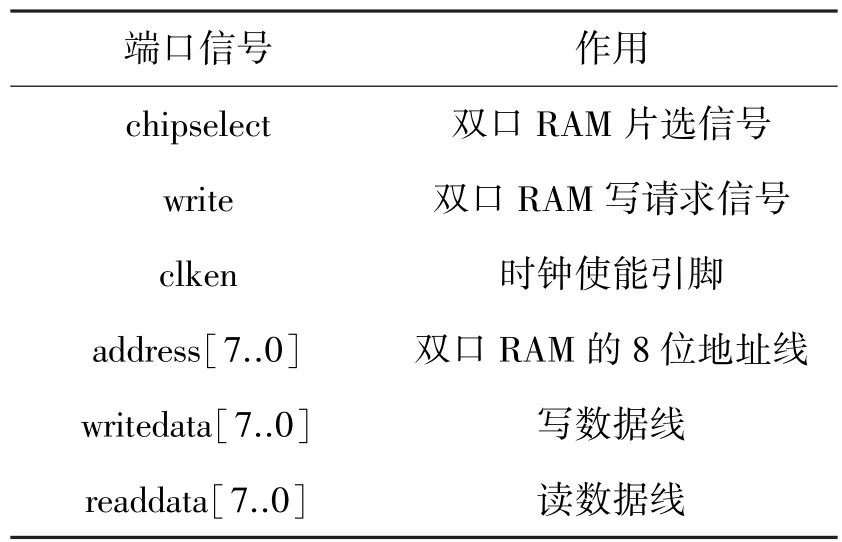

在進行Qsys系統建立、添加片上存儲器外設時,將其設置為雙口RAM的模式,數據寬度選取為8位數據模式,RAM大小設置為256 bits。設置完成后雙口RAM的一端的地址線以及數據線自動連接到Qsys系統的Avalon交互式總線上,另一端口的數據線可以由用戶分配到相應的I/O口與 DSP的EMIF接口連接。在雙口RAM中的各個端口信號含義如表1所示。

表1 雙口RAM各端口信號含義

3.2 雙口RAM的時序仿真設計

為了使生成的雙口RAM與DSP6726的EMIF接口設計時序匹配,對生成的雙口RAM進行了時序仿真,如圖4所示。

圖4 雙口RAM基本讀寫時序仿真

從仿真結果得出雙口RAM的基本寫時序為:控制chipset信號變為高電平,給出要寫入的地址信號和數據信號,再給出write信號和clken信號,將要寫入的數據寫入到雙口RAM中;雙口RAM的基本讀時序為:給出要讀出的數據地址信號,控制chipset信號和clken信號變為高電平,在經過一段延遲時間后,數據將在readdata上進行輸出。

3.3 DSP與雙口RAM接口電路的設計

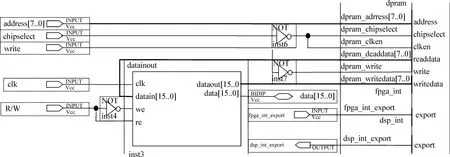

由于DSP的數據線是雙向的,而Qsys生成的數據輸入和輸出線是分開的,所以需要加入數據方向控制電路,否則DSP將只能進行數據讀操作或寫操作。TMS320C6726 DSP只有一個異步片選信號CS2,而雙口RAM與Flash共用外部的地址線與數據線,當DSP對Flash進行讀操作時同時也對雙口RAM進行讀操作,這樣必然導致讀取的數據出錯。為了不讓Flash和DPRAM存儲空間地址重疊,設計通過DSP的一個GPIO控制CS2片選信號。

當GPIO置高時可以讀寫DPRAM數據;GPIO置低時讀寫Flash的數據。DSP6726擴展FPGA為異步存儲器的接口如圖5所示。

圖5 DSP6726擴展FPGA為異步存儲器的接口

圖6 Quartus II中雙口RAM的接口電路

考慮到DSP6726擴展外部存儲器的時序要求和為了匹配Avalon從外設讀寫時序,DSP的chipse-lect和write信號經過非門接到了DPRAM相應端口上;在數據轉換電路中,通過DSP的EMRW信號對方向進行選擇,EMRW信號在DSP的讀數據區間呈高電平狀態,在DSP的寫數據區間呈低電平狀態,因此將R/W信號通過非門連接到datainout模塊的we端口,同時R/W信號又直接連接到re端口;clk-en引腳只需在讀寫周期內有效,因此直接連到DPRAM的chipselect上,接口電路如圖6所示。

4 結束語

以DSP和FPGA雙CPU構架為核心的導航微機系統經過調試表明,系統的性能明顯優于傳統的捷聯導航微機系統。此導航微機系統具有體積小、功耗低、性價比高、功能擴展靈活的特點,已成功地用在基于石英音叉陀螺(微機械陀螺)的小型捷聯制導系統中,出色地完成了捷聯制導計算的工作。本系統的研制對于擴展捷聯慣性導航系統的應用領域具有一定的積極作用。

[1]羅廣紅.基于 DSP/FPGA的捷聯導航計算機研究[D].哈爾濱:哈爾濱工程大學,2012:2-3.

[2]劉勇.基于DSP和AVR單片機的主從式雙CPU導航計算機[J].壓電與聲光,2003(6):456-458.

[3]張樹俠,孫靜.捷聯式慣性導航系統[M].北京:國防工業出版社,1992:8-9.

[4]胡文彬,高延濱,許德新.新型雙CPU架構的捷聯慣性導航微機系統[J].應用科技,2007,34(6):23-25.

[5]高延濱,詹俊妮,何昆鵬,等.高精度石英振梁加速度計頻率采樣系統設計[J].應用科技,2012,39(3):61-64.

[6]陳美燕.基于FPGA+DSP的信息采集板的設計[D].成都:西南交通大學,2009:45-46.

[7]周立功.SOPC嵌入式系統基礎教程[M].北京:北京航空航天大學出版社,2006:9-54.

[8]秦鴻剛,劉京科,吳迪.基于FPGA的雙口RAM實現及應用[J].電子設計工程,2010,18(2):72-74.

[9]季強,劉利強.雙口RAM在數據采集系統中的應用[J].應用科技,2004,31(5):22-24.

[10]劉杰.基于模型的設計——Qsys篇[M].北京:機械工業出版社,2012:33-35.

The design and implementation of navigation computer with dual CPU based on DSP and FPGA processor

GAOYanbin,LIU Huiyu,HE Kunpeng,ZHANG Xingzhi

College of Automation,Harbin Engineering University,Harbin 150001,China

In order to meet the development of the inertial system,a new kind of navigation computer with the char-acteristics of small size,low power,low cost and high performance was presented in this paper.The navigation computer system is made up of digital signal processor(DSP)chip TMS320C6726 from TI company and FPGA chip EP3C10E144A7 from Altera company.DSP is mainly responsible for the navigation calculation and data pro-cessing,and FPGA is mainly responsible for inertial measurement unit(IMU)data acquisition and interface con-trol.The microcomputer system takes advantages of fast processing speed and strong float point data processing ca-pability of TMS320C6726 and SOPC technology of FPGA.The dual-CPU can quickly transmit data through double-port RAM which is achieved by VHDL language.The operating efficiency of the navigation computer is improved.

navigation computer;DSP;double CPU;dual-port RAM;strap-down algorithm

TP273.4

A

1009-671X(2014)03-0023-04

10.3969/j.issn.1009-671X.201305025

2013-05-30.

國家自然科學基金資助項目(51309059).

高延濱(1963-),男,教授,博士生導師;

劉輝煜(1990-),男,碩士研究生.

劉輝煜,E-mail:liuhuiyu415@163.com.