基于嵌入式CPU的加解密子系統(tǒng)

王劍非,馬 德,熊東亮,陳 亮,黃 凱,葛海通

(1.公安部第一研究所,北京100048;2.杭州電子科技大學(xué)微電子CAD所,杭州310018;

3.浙江大學(xué)超大規(guī)模集成電路設(shè)計(jì)研究所,杭州310027;4.杭州中天微系統(tǒng)有限公司,杭州310012)

基于嵌入式CPU的加解密子系統(tǒng)

王劍非1,馬 德2,熊東亮3,陳 亮3,黃 凱3,葛海通4

(1.公安部第一研究所,北京100048;2.杭州電子科技大學(xué)微電子CAD所,杭州310018;

3.浙江大學(xué)超大規(guī)模集成電路設(shè)計(jì)研究所,杭州310027;4.杭州中天微系統(tǒng)有限公司,杭州310012)

針對(duì)信息安全等級(jí)和應(yīng)用場(chǎng)合變化時(shí)IP級(jí)復(fù)用的片上系統(tǒng)(SoC)集成驗(yàn)證效率低的問(wèn)題,提出一種基于嵌入式CPU的加解密子系統(tǒng)。子系統(tǒng)包括RSA,DES,AES等多種加解密模塊,通過(guò)硬件上的參數(shù)配置,構(gòu)造滿足不同信息安全應(yīng)用和等級(jí)的子系統(tǒng);采用低功耗高性能的嵌入式CPU,作為SoC中主CPU的協(xié)處理器,控制各加解密模塊的工作,可減少對(duì)主CPU的訪問(wèn),以降低功耗。將經(jīng)過(guò)驗(yàn)證的加解密子系統(tǒng)作為整體集成到SoC中,實(shí)現(xiàn)子系統(tǒng)復(fù)用,可減少SoC設(shè)計(jì)和集成工作量,降低SoC驗(yàn)證難度;利用門(mén)控時(shí)鐘技術(shù),根據(jù)各加解密模塊的工作狀態(tài)管理時(shí)鐘,從而降低加解密子系統(tǒng)的功耗。采用CKSoC設(shè)計(jì)集成方法,在SoC集成工具平臺(tái)上可快速集成不同配置下的基于嵌入式CPU的加解密子系統(tǒng)。實(shí)驗(yàn)結(jié)果表明,構(gòu)造子系統(tǒng)后的SoC設(shè)計(jì)和驗(yàn)證工作量明顯減少,提高了工作效率。

加解密子系統(tǒng);系統(tǒng)復(fù)用;片上系統(tǒng)集成;高級(jí)加密標(biāo)準(zhǔn);數(shù)據(jù)加密標(biāo)準(zhǔn)

1 概述

近年來(lái),片上系統(tǒng)(System-On-Chip,SoC)設(shè)計(jì)領(lǐng)域的信息安全問(wèn)題越來(lái)越受到重視,密碼技術(shù)是信息安全的核心和關(guān)鍵技術(shù)。從密碼體系方面看,密碼體制包括對(duì)稱(chēng)密碼和非對(duì)稱(chēng)密碼兩大類(lèi)。對(duì)稱(chēng)密碼體制在加密和解密中采用相同的密鑰,又稱(chēng)私鑰密碼體制,典型的算法有數(shù)據(jù)加密標(biāo)準(zhǔn)(Data Encryption Standard,DES)和高級(jí)加密標(biāo)準(zhǔn)(Advanced Encryption Standard,AES)。DES是使用最為廣泛的對(duì)稱(chēng)密鑰算法,但面臨著嚴(yán)重的窮舉攻擊問(wèn)題,安全性有待提高。AES是NIST于2001年11月發(fā)布的替代DES的對(duì)稱(chēng)分組密碼算法,具有比3DES更高的安全性。非對(duì)稱(chēng)密碼體制,在加密和解密中采用不同的密鑰,又稱(chēng)公鑰密碼體制。加密的密鑰稱(chēng)為公鑰,向公眾公開(kāi);解密的密鑰稱(chēng)為私鑰,由解密人持有,用來(lái)解密由公鑰加密的數(shù)據(jù)。典型的算法有RSA,其可靠性基于大整數(shù)素因子分解的困難性,具有較高的安全性。

為了降低設(shè)計(jì)復(fù)雜度和縮短芯片的開(kāi)發(fā)周期, IP復(fù)用的設(shè)計(jì)方法被廣泛采用于SoC設(shè)計(jì)中,但隨著系統(tǒng)規(guī)模的擴(kuò)大,IP集成和驗(yàn)證的工作量越來(lái)越大,同時(shí)也帶來(lái)了巨大的風(fēng)險(xiǎn)。通過(guò)將多個(gè)IP單元模塊整合到一起而成為一個(gè)完整、預(yù)集成和預(yù)驗(yàn)證子系統(tǒng),能夠顯著減少設(shè)計(jì)師在SoC設(shè)計(jì)和集成的工作量,縮短系統(tǒng)的開(kāi)發(fā)周期,同時(shí)降低系統(tǒng)復(fù)雜性和設(shè)計(jì)風(fēng)險(xiǎn),保證了產(chǎn)品的安全性。為了提高IP和系統(tǒng)平臺(tái)在不同設(shè)計(jì)環(huán)境中的重用性,學(xué)術(shù)界和工業(yè)界制定了多種重用標(biāo)準(zhǔn),如 OSCI[1],OCP-IP[2], IP-XACT[3]等。

IP-XACT標(biāo)準(zhǔn),由于在IP配置與SoC集成自動(dòng)化方面的優(yōu)越性,是目前應(yīng)用最為廣泛的IP復(fù)用標(biāo)準(zhǔn)之一。IP-XACT標(biāo)準(zhǔn)規(guī)定了一種基于XML的數(shù)據(jù)結(jié)構(gòu),從不同方面描述IP的全部信息:配置信息,信號(hào)端口,總線接口和寄存器地址分配等,同時(shí)該標(biāo)準(zhǔn)還可用于描述子系統(tǒng)和完整的SoC。采用IP-XACT標(biāo)準(zhǔn)描述的IP和系統(tǒng),能夠被任何支持IP-XACT標(biāo)準(zhǔn)的EDA工具集成,從而有效提高IP和系統(tǒng)在不同EDA工具間的移植重用性[4]。

本文提出了一種基于嵌入式CPU的加解密子系統(tǒng)結(jié)構(gòu),包含了預(yù)先驗(yàn)證過(guò)的常用加解密模塊——DES,AES,RSA,可減少集成后的驗(yàn)證工作量,而其中的嵌入式CPU可以將數(shù)據(jù)加解密任務(wù)從主處理器上卸下來(lái),提高SoC的性能和效率。采用基于IP-XACT的CKSoC設(shè)計(jì)集成方法將其集成到工具平臺(tái)上,入庫(kù)并支持參數(shù)可配,可以根據(jù)需要有效快速地生成相應(yīng)的加解密子系統(tǒng),進(jìn)而生成更復(fù)雜的SoC系統(tǒng)。

2 SoC中的加解密系統(tǒng)

為了提高SoC系統(tǒng)的安全性,SoC系統(tǒng)中加解密系統(tǒng)的設(shè)計(jì)越來(lái)越受重視。目前,SoC設(shè)計(jì)中加解密系統(tǒng)的設(shè)計(jì)主要通過(guò)集成嵌入式CPU和單個(gè)加解密模塊,文獻(xiàn)[5]中的 Cryptosystem SoC (CSoC),整合虛擬微處理器和AES模塊組成一個(gè)加解密系統(tǒng),并對(duì)該系統(tǒng)進(jìn)行低功耗設(shè)計(jì);文獻(xiàn)[6]提到基于嵌入式Linux的RSA加密子系統(tǒng),采用軟硬件結(jié)合的方式,軟件負(fù)責(zé)密鑰生成存儲(chǔ)等,硬件負(fù)責(zé)RSA的模冪運(yùn)算。而針對(duì)多個(gè)加解密模塊的子系統(tǒng)研究相對(duì)較少,文獻(xiàn)[7]中提到的多模加解密系統(tǒng)(Multi-cipher Cryptosystem,MCC),其加解密核由AES、DES和TDES組成,對(duì)一段通信會(huì)話實(shí)現(xiàn)多個(gè)加解密算法的操作,但是其僅僅限于對(duì)稱(chēng)密碼體制算法,而且不支持根據(jù)SoC應(yīng)用需求的硬件可配置,使其應(yīng)用范圍受限制。

加解密系統(tǒng)的設(shè)計(jì),除了性能之外,對(duì)于功耗也有很高的要求。文獻(xiàn)[8]設(shè)計(jì)的DES/3DES處理器的最高工作頻率達(dá)到110 MHz,數(shù)據(jù)處理帶寬達(dá)到7 Gb/s,但是該模塊占用面積較大,功耗也大,無(wú)法滿足當(dāng)前低功耗低成本SoC設(shè)計(jì)的需要。與當(dāng)前加解密系統(tǒng)相比,本文提出的基于嵌入式CPU的加解密子系統(tǒng)支持多個(gè)加解密算法,同時(shí)涵蓋對(duì)稱(chēng)和非對(duì)稱(chēng)密碼體制,而且采用功耗較低的加解密模塊,能夠根據(jù)加解密等級(jí)動(dòng)態(tài)關(guān)閉對(duì)應(yīng)模塊時(shí)鐘降低功耗,降低子系統(tǒng)功耗。子系統(tǒng)通過(guò)IP-XACT標(biāo)準(zhǔn)進(jìn)行封裝,支持硬件靈活配置,擴(kuò)大子系統(tǒng)應(yīng)用范圍。基于穩(wěn)定可配子系統(tǒng)的SoC設(shè)計(jì),可有效減少SoC設(shè)計(jì)時(shí)間和降低驗(yàn)證難度。

3 加解密子系統(tǒng)

3.1 子系統(tǒng)通用架構(gòu)

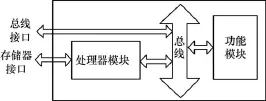

特定功能的子系統(tǒng)主要由三部分組成:控制整個(gè)子系統(tǒng)工作的處理器模塊,實(shí)現(xiàn)特定功能的功能模塊,以及負(fù)責(zé)子系統(tǒng)內(nèi)部模塊之間和子系統(tǒng)與外部主系統(tǒng)之間連接通信的總線。特定功能的子系統(tǒng)的通用架構(gòu)如圖1所示。

圖1 基于嵌入式CPU的子系統(tǒng)通用架構(gòu)

子系統(tǒng)的處理器模塊,將子系統(tǒng)的控制任務(wù)從外部主處理器中卸下來(lái),再通過(guò)中斷的方式反饋,提高了SoC的整體性能和效率。子系統(tǒng)的接口設(shè)計(jì)一般包含兩部分:存儲(chǔ)器接口和總線接口。存儲(chǔ)器接口用于子系統(tǒng)內(nèi)部處理器獲取指令和讀寫(xiě)數(shù)據(jù);總線接口,不僅用于外部主處理器訪問(wèn)內(nèi)部IP模塊,還可以用于實(shí)現(xiàn)內(nèi)外處理器之間的通信。

3.2 加解密子系統(tǒng)架構(gòu)

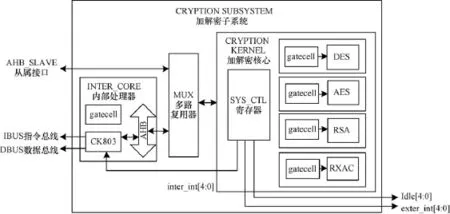

根據(jù)子系統(tǒng)通用架構(gòu),搭建出基于嵌入式CPU的加解密子系統(tǒng),該加解密子系統(tǒng)主要由三部分組成:包含嵌入式CPU CK803的內(nèi)部處理器模塊[9]、負(fù)責(zé)仲裁子系統(tǒng)內(nèi)部及與外部通信的多路復(fù)用器、包含各個(gè)加解密模塊的加解密核心模塊,總體架構(gòu)如圖2所示。

圖2 基于嵌入式CPU的加解密子系統(tǒng)架構(gòu)

該子系統(tǒng)共有三組接口信號(hào),分別是供外部CPU控制信號(hào)傳輸?shù)膹膶俳涌凇?nèi)部CPU CK803訪問(wèn)存儲(chǔ)器的指令總線和數(shù)據(jù)總線。此外,子系統(tǒng)還包括5個(gè)中斷信號(hào)和5個(gè)空閑信號(hào),用于表示內(nèi)部加解密核的工作狀態(tài)。

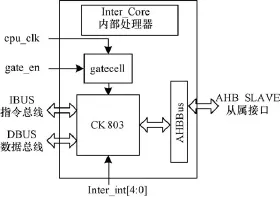

3.3 內(nèi)部處理器

內(nèi)部處理器包含嵌入式CPU、AHB總線及門(mén)控時(shí)鐘單元,是子系統(tǒng)的控制模塊,負(fù)責(zé)子系統(tǒng)內(nèi)部功能模塊的運(yùn)算過(guò)程,其結(jié)構(gòu)如圖3所示。

圖3 內(nèi)部處理器結(jié)構(gòu)

CK803是一款低功耗、高性能的國(guó)產(chǎn)嵌入式CPU,不僅性能上可以滿足子系統(tǒng)的控制要求,而且它的低功耗特性也能滿足子系統(tǒng)的功耗要求。為了進(jìn)一步的降低功耗,CK803有4種工作模式,分別對(duì)應(yīng)系統(tǒng)不同的功耗狀態(tài):

(1)工作模式:所有子系統(tǒng)模塊時(shí)鐘正常提供,動(dòng)態(tài)功耗最大;

(2)等待模式:CPU執(zhí)行完WAIT指令后,進(jìn)入等待低功耗模式,此時(shí)CPU停止工作,其他IP模塊正常工作,可大大減少系統(tǒng)動(dòng)態(tài)功耗;

(3)休眠模式:CPU執(zhí)行完DOZE指令后,進(jìn)入休眠低功耗模式,此時(shí)CPU和空閑的IP時(shí)鐘關(guān)斷,其他IP正常工作,進(jìn)一步降低動(dòng)態(tài)功耗;

(4)停止模式:只有喚醒邏輯工作,其他IP關(guān)閉,系統(tǒng)動(dòng)態(tài)功耗處于最小值。

CK803內(nèi)部集成了中斷控制器,在其等待、休眠或停止模式下,子系統(tǒng)可通過(guò)伸給它的5個(gè)中斷信號(hào)inter_int[4:0]將其喚醒。inter_int[0]由外部CPU寫(xiě)SYS_CTL寄存器產(chǎn)生的中斷信號(hào),inter_int [4:1]是分別由DES、AES、RSA和RXAC 4個(gè)數(shù)據(jù)加解密模塊產(chǎn)生的中斷信號(hào)。

3.4 多路復(fù)用器

多路復(fù)用器包含一個(gè)互聯(lián)矩陣ICM模塊,接收多層AHB從屬接口信號(hào),按照配置的優(yōu)先級(jí)進(jìn)行仲裁,選擇相應(yīng)的 AHB從屬接口信號(hào)輸出給后面的IP。

加解密子系統(tǒng)中的互聯(lián)矩陣模塊接收兩層AHB從屬接口信號(hào):內(nèi)部處理器的AHB從屬接口信號(hào)和子系統(tǒng)外部的AHB從屬接口信號(hào),其中前者的接口優(yōu)先級(jí)高于后者。

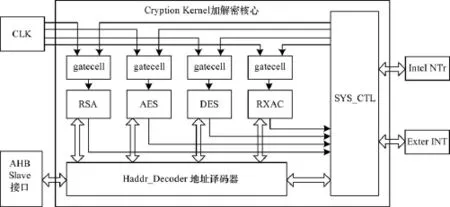

3.5 加解密核心

加解密核心主要由AHB地址譯碼器、SYS_CTL寄存器、及AES、DES、RSA和RXAC加解密模塊組成,其結(jié)構(gòu)如圖4所示。

圖4 加解密核心結(jié)構(gòu)

(1)AHB地址譯碼器:總線信號(hào)解析模塊,根據(jù)各個(gè)模塊的地址空間分配,解析出目標(biāo)寄存器的位置,并進(jìn)行相應(yīng)的讀寫(xiě)操作。

(2)SYS_CTL:包含系統(tǒng)控制寄存器,主要有內(nèi)部CPU指令基地址寄存器INS_BADDR、時(shí)鐘開(kāi)關(guān)控制寄存器GATE_REG、內(nèi)部CPU中斷屏蔽寄存器INTER_INT_MASK、外部CPU中斷屏蔽寄存器EXTER_INT_MASK、內(nèi)部CPU中斷產(chǎn)生寄存器INTER_CPU_INT、外部 CPU中斷產(chǎn)生寄存器EXTER_CPU_INT。

(3)DES模塊:DES算法使用64位密鑰,其中, 56位隨機(jī)生成并直接用于算法,其他8位用于奇偶檢測(cè)。加密的數(shù)據(jù)只能使用加密用的密鑰才能恢復(fù),但是由于只有56位有效密鑰,因此DES算法很容易被采用暴力方法“窮舉攻擊”破解,安全性較差。TDES進(jìn)行3次DES算法,有3組密鑰,使得密鑰有效位變成168位,大大提高了安全性[10]。

本文的DES模塊同時(shí)實(shí)現(xiàn)了DES和TDES加解密算法。當(dāng)硬件實(shí)現(xiàn)時(shí),在不犧牲太大性能的前提下,以面積作為優(yōu)先考慮設(shè)計(jì),僅采用一級(jí)數(shù)據(jù)通道,結(jié)構(gòu)簡(jiǎn)單,占用資源較少。當(dāng)運(yùn)算結(jié)束或密鑰數(shù)據(jù)奇偶校驗(yàn)錯(cuò)誤時(shí),該模塊發(fā)出中斷信號(hào)。此外, DES模塊對(duì)外有空閑IDLE信號(hào),在其工作結(jié)束后置為有效,表示DES模塊處于空閑狀態(tài),可將其時(shí)鐘關(guān)閉,以減少功耗。

(4)AES模塊:AES算法,即Rijndael算法,是一種對(duì)稱(chēng)分組密碼算法,數(shù)據(jù)分組長(zhǎng)度固定為128 bit,使用的密鑰長(zhǎng)度可為128 bit,192 bit和256 bit。對(duì)于AES算法,算法的輪數(shù)依賴(lài)于密鑰長(zhǎng)度,128 bit密鑰時(shí)輪數(shù)為10,192 bit密鑰時(shí)輪數(shù)為12,256 bit密鑰時(shí)輪數(shù)為14。AES算法的輪函數(shù)由4個(gè)不同的以字節(jié)為基本單位的變換復(fù)合而成:1)字節(jié)替代(S盒);2)將狀態(tài)矩陣的每一行循環(huán)移位不同的位移量;3)將狀態(tài)矩陣中的每一列的數(shù)據(jù)進(jìn)行混合; 4)將輪密鑰加到狀態(tài)上。對(duì)于AES算法沒(méi)有發(fā)現(xiàn)弱密鑰或半弱密鑰,所以對(duì)密鑰選取沒(méi)有限制[11]。作為一種替代DES算法的新標(biāo)準(zhǔn),AES算法具有更高的安全性。

AES模塊根據(jù)AES算法標(biāo)準(zhǔn),基于AMBA總線接口,分組長(zhǎng)度固定為 128 bit,支持 128 bit, 192 bit和256 bit密鑰的AES算法。AES算法的基本運(yùn)算包括加密、解密和密鑰擴(kuò)展,數(shù)據(jù)通道實(shí)現(xiàn)了加密和解密資源復(fù)用,使得占用資源較少。數(shù)據(jù)通道每一個(gè)周期實(shí)現(xiàn)一輪輪變換,輪變換需要的密鑰由密鑰擴(kuò)展器生成,加密時(shí)采用動(dòng)態(tài)密鑰調(diào)度,解密時(shí)采用靜態(tài)密鑰調(diào)度。當(dāng)運(yùn)算結(jié)束或密鑰數(shù)據(jù)奇偶校驗(yàn)錯(cuò)誤時(shí),該模塊發(fā)出中斷信號(hào)。此外,AES模塊對(duì)外有空閑IDLE信號(hào),在其工作結(jié)束后置為有效,表示AES模塊處于空閑狀態(tài),可將其時(shí)鐘關(guān)閉,以減少功耗。

(5)RSA模塊:RSA算法,是由Ron Rivest,Adi Shamir和Leonard Adleman于1978發(fā)表的一種非對(duì)稱(chēng)密碼算法,可用于加密和數(shù)字簽名中。RSA加密過(guò)程:將明文用數(shù)字M表示,然后計(jì)算M的E(公鑰)次冪,再取除以公開(kāi)的模N后的余數(shù)作為密文。模N由2個(gè)私有的素?cái)?shù)p和q相乘而得,加密用的公鑰E和解密用的私鑰D滿足E×D≡1(mod(p-1)(q-1)),解密的過(guò)程與加密一致,只是要用私鑰D。RSA算法的安全性依賴(lài)于模 N素?cái)?shù)分解的難度[12]。

RSA模塊采用蒙哥馬利模乘算法,通過(guò)循環(huán)實(shí)現(xiàn)RSA算法中的核心運(yùn)算模冪。蒙哥馬利算法是一種快速的大數(shù)模乘算法,將大數(shù)相乘后的求模運(yùn)算簡(jiǎn)化成一次減法,提高了計(jì)算效率,而且由于每次循環(huán)的中間結(jié)果較小,節(jié)省了很多存儲(chǔ)空間。RSA模塊采用AMBA總線接口,支持192 bit,256 bit, 512 bit,1 024 bit,2 048 bit的 RSA加解密。由于RSA算法加解密速度相比DES、AES算法會(huì)慢很多,為提高數(shù)據(jù)吞吐率,其數(shù)據(jù)通路進(jìn)行了3級(jí)流水線設(shè)計(jì)。采用軟硬件協(xié)同工作的方式,軟件負(fù)責(zé)模和密鑰的生成,硬件負(fù)責(zé)加解密運(yùn)算,以達(dá)到更好的性能。另外,RSA模塊支持中斷和低功耗模式。

(6)RXAC模塊:Rotate and Xor Accelerator,一個(gè)持?jǐn)?shù)據(jù)異或和循環(huán)移位的硬件加速模塊,解決安全芯片中大量的異或和循環(huán)移位數(shù)據(jù)處理操作占用存儲(chǔ)器資源、導(dǎo)致系統(tǒng)性能下降的問(wèn)題。可通過(guò)靈活的配置,實(shí)現(xiàn)8 bit,16 bit,32 bit,64 bit,128 bit數(shù)據(jù)位寬的異或、向左循環(huán)移位和向右循環(huán)移位操作。

3.6 子系統(tǒng)功耗設(shè)計(jì)

隨著SoC芯片在便攜式領(lǐng)域的廣泛應(yīng)用,對(duì)于功耗的要求越來(lái)越高,在基于嵌入式CPU的加解密子系統(tǒng)的設(shè)計(jì)過(guò)程中,通過(guò)門(mén)控時(shí)鐘來(lái)動(dòng)態(tài)關(guān)閉各加解密模塊的時(shí)鐘以減少功耗。

CMOS集成電路的功耗可分為動(dòng)態(tài)功耗和靜態(tài)功耗兩部分,動(dòng)態(tài)功耗包括翻轉(zhuǎn)功耗、內(nèi)部短路功耗,靜態(tài)功耗包括漏電功耗。靜態(tài)功耗是由器件物理特性決定,在系統(tǒng)供電時(shí)一直存在,而動(dòng)態(tài)功耗與系統(tǒng)工作狀態(tài)直接相關(guān),系統(tǒng)工作頻率越高,系統(tǒng)消耗的動(dòng)態(tài)功耗就越大,其中翻轉(zhuǎn)功耗要占到所有功耗的70%以上。

在模塊空閑狀態(tài)下,如果能夠停止模塊時(shí)鐘的供給,可以有效地降低系統(tǒng)的動(dòng)態(tài)功耗。在加解密子系統(tǒng)中,采用門(mén)控時(shí)鐘控制模塊的時(shí)鐘狀態(tài)。門(mén)控時(shí)鐘單元由一個(gè)鎖存器和一個(gè)與門(mén)組成,結(jié)構(gòu)如圖5所示。當(dāng)模塊不工作時(shí),使能信號(hào)無(wú)效,門(mén)控時(shí)鐘單元輸出給模塊的門(mén)控時(shí)鐘將置低,不再翻轉(zhuǎn),以減少該模塊的動(dòng)態(tài)功耗。

圖5 門(mén)控時(shí)鐘單元

為了減少子系統(tǒng)的動(dòng)態(tài)功耗,在各個(gè)IP模塊前插入門(mén)控時(shí)鐘單元,運(yùn)用門(mén)控時(shí)鐘單元關(guān)閉各模塊時(shí)鐘,使子系統(tǒng)具有功耗管理功能。對(duì)于子系統(tǒng)中的各模塊,其具體策略如下:

(1)加解密模塊:伸出IDLE信號(hào)給SYS_CTL,當(dāng)IDLE有效時(shí),處理器配置SYS_CTL中的門(mén)控時(shí)鐘寄存器,關(guān)閉該模塊時(shí)鐘;

(2)CK803:時(shí)鐘在默認(rèn)狀態(tài)是關(guān)閉的,當(dāng)處于工作狀態(tài)時(shí),配置SYS_CTL的門(mén)控時(shí)鐘寄存器可將時(shí)鐘打開(kāi);當(dāng)處于等待、休眠和停止?fàn)顟B(tài)時(shí),IDLE信號(hào)有效,關(guān)閉時(shí)鐘。

4 加解密子系統(tǒng)的實(shí)現(xiàn)

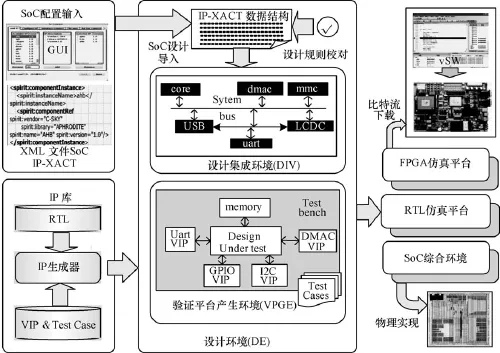

CKSoC設(shè)計(jì)集成方法是一種基于IP-XACT標(biāo)準(zhǔn)的高效SoC集成方法,采用自底向上的集成策略,支持IP級(jí)和子系統(tǒng)級(jí)的復(fù)用,并能生成3個(gè)不同的平臺(tái)——RTL仿真平臺(tái)、FPGA原型仿真平臺(tái)和門(mén)級(jí)網(wǎng)表邏輯綜合環(huán)境,有利于IP和子系統(tǒng)的測(cè)試和驗(yàn)證,可以明顯提高SoC設(shè)計(jì)集成效率。CKSoC設(shè)計(jì)集成方法主要由三部分組成:用于導(dǎo)入SoC架構(gòu)與配置信息的SoC用戶(hù)接口,用IP-XACT封裝的IP庫(kù)和用于產(chǎn)生 SoC RTL代碼和平臺(tái)的設(shè)計(jì)環(huán)境(DE)[4]。CKSoC設(shè)計(jì)集成方法的整體工作流程如圖6所示。

圖6 CKSoC設(shè)計(jì)集成方法的流程

4.1 子系統(tǒng)的IP-XACT XML文件

IP-XACT標(biāo)準(zhǔn)采用XML文件來(lái)有效存儲(chǔ)IP/子系統(tǒng)的信息,XML中包含的信息主要有端口信號(hào)、總線接口、存儲(chǔ)空間(可訪問(wèn)的寄存器,包括地址及讀寫(xiě)屬性)和元件信息(代碼及測(cè)試case等)。所以,加解密子系統(tǒng)的集成,也需要描述子系統(tǒng)信息的XML文件以及生成相應(yīng)代碼、測(cè)試激勵(lì)的生成器腳本。

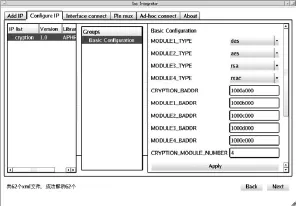

子系統(tǒng)的XML文件除了包含上述的信息外,還包括子系統(tǒng)的配置參數(shù)。配置參數(shù)主要有子系統(tǒng)在總系統(tǒng)中的基地址、子系統(tǒng)中加解密模塊的個(gè)數(shù)、每個(gè)加解密模塊的類(lèi)型(DES,AES,RSA和RXAC)、每個(gè)加解密模塊的寄存器基地址。開(kāi)發(fā)好子系統(tǒng)的XML文件后,便可在SoC集成平臺(tái)中方便的根據(jù)需要配置子系統(tǒng)的參數(shù)并生成對(duì)應(yīng)參數(shù)的子系統(tǒng)。圖7顯示了在SoC集成平臺(tái)中子系統(tǒng)參數(shù)的配置。

圖7 子系統(tǒng)的參數(shù)配置

4.2 子系統(tǒng)的生成器腳本

在SoC集成工具平臺(tái)中完成了子系統(tǒng)的配置后,平臺(tái)會(huì)通過(guò)調(diào)用Perl語(yǔ)言描述的子系統(tǒng)生成器腳本,生成子系統(tǒng)的代碼、測(cè)試文件等,具體的工作流程如圖8所示。

(1)解析參數(shù):解析Cryption.xml中用戶(hù)配置的參數(shù),給對(duì)應(yīng)變量賦值,生成包含參數(shù)宏定義;

(2)加解密IP的RTL代碼生成:根據(jù)所添加的加解密IP,生成對(duì)應(yīng)的RTL代碼,包括DES,AES, RSA和RXAC中的各部分代碼和頂層文件;

(3)生成加解密核心代碼:生成加解密核心部分中地址譯碼器、SYS_CTL寄存器及門(mén)控單元等的代碼,并生成實(shí)例化連接核心中所有模塊的頂層文件;

(4)生成內(nèi)部處理器和互聯(lián)矩陣代碼:包括CK803、AHB、門(mén)控單元和互聯(lián)矩陣的代碼;

(5)生成頂層文件:實(shí)例化子系統(tǒng)各個(gè)部分的RTL代碼,連接各模塊的接口,生成最頂層文件;

(6)生成測(cè)試文件:生成各個(gè)加解密IP的測(cè)試case及SYS_CTL寄存器讀寫(xiě)的測(cè)試case,方便測(cè)試和驗(yàn)證;

(7)生成新的XML文件:根據(jù)最終生成的.v和.h文件更新XML文件中相關(guān)文件列表,更新接口信號(hào);根據(jù)最終生成的頂層文件的輸入輸出信號(hào)更新XML文件的端口信號(hào)列表。

圖8 子系統(tǒng)生成器腳本工作流程

5 實(shí)驗(yàn)結(jié)果與分析

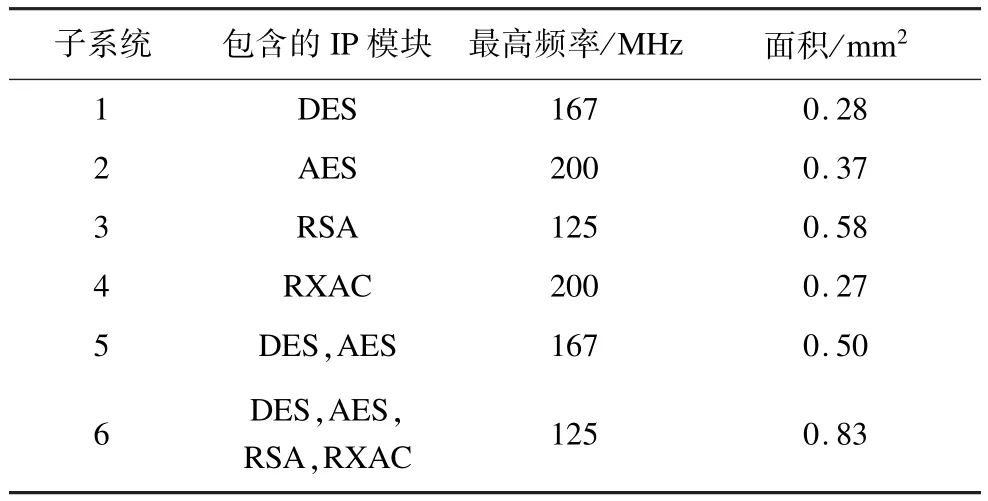

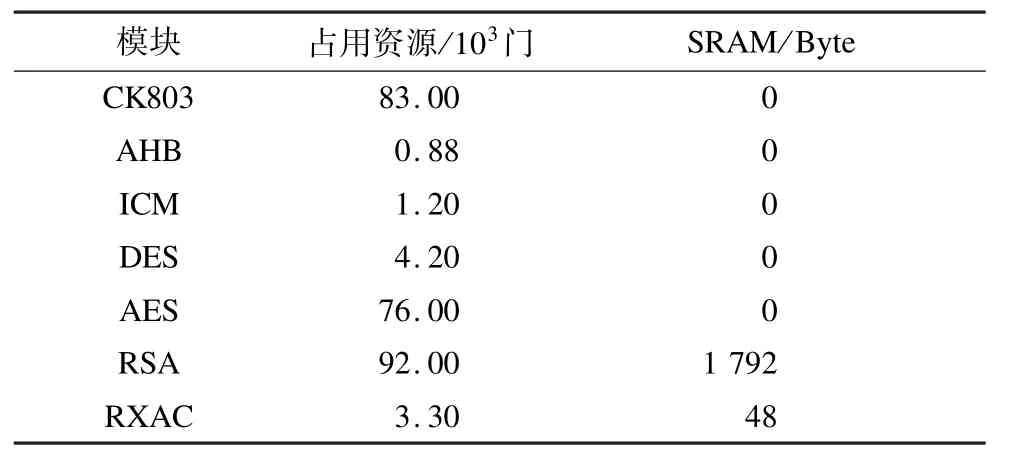

在SoC集成工具平臺(tái)上,按照不同的需求配置子系統(tǒng)的參數(shù),將子系統(tǒng)集成在一個(gè)SoC系統(tǒng)中。SoC系統(tǒng)基于SMIC 0.13 μm標(biāo)準(zhǔn)單元庫(kù)工藝,采用Synopsys Design Compiler綜合實(shí)現(xiàn)門(mén)級(jí)網(wǎng)表,得到子系統(tǒng)在不同配置下的最高工作頻率和面積,如表1所示,以及子系統(tǒng)中各模塊占用的硬件資源,如表2所示。

表1 不同配置下子系統(tǒng)的頻率與面積

表2 子系統(tǒng)各模塊占用資源

實(shí)驗(yàn)結(jié)果表明各加解密模塊的性能如下:

(1)AES:在加解密128 bit數(shù)據(jù)、密鑰長(zhǎng)度為128 bit時(shí),AES需要運(yùn)算10個(gè)周期,加上4個(gè)周期寫(xiě)未加密的數(shù)據(jù),4個(gè)周期讀加密好的數(shù)據(jù),所以,可以得到 AES在 128 bit密鑰時(shí)的最大帶寬: 200 MHz×128 bit/(10+4+4)=1.42 Gb/s;同理, 192 bit密鑰時(shí)最大帶寬為200 MHz×128 bit/(12+ 4+4)1.28 Gb/s,256 bit密鑰時(shí)最大帶寬為200 MHz×128 bit/(14+4+4)1.16 Gb/s。

(2)DES:DES算法運(yùn)算需16個(gè)周期,加上2個(gè)周期寫(xiě)數(shù)據(jù),2個(gè)周期讀數(shù)據(jù),共需20個(gè)周期來(lái)加解密64 bit的數(shù)據(jù),所以,DES的最大帶寬為167 MHz× 64 bit/(16+2+2)=534 Mb/s,3DES的最大帶寬為167 MHz×64 bit/(48+2+2)=205 Mb/s。

(3)RSA:在125 MHz、公鑰為0x10 001的條件下: 1)2 048 bit:加密4 600次,解密28次。2)1 024 bit:加密14 020次,解密180次。3)512 bit:加密41 550次,解密1 025次。

如圖9所示,在配置有RSA和AES的子系統(tǒng)中,在連線工作量上,構(gòu)造子系統(tǒng)前比構(gòu)造后多了很多內(nèi)部連接,而且這些內(nèi)部連接會(huì)隨著配置的變化而有所變化,使得每次都得重新連接。另外,由于構(gòu)造前是以IP為單元的,因此內(nèi)部連接是否正確也屬于驗(yàn)證的內(nèi)容,這在構(gòu)造子系統(tǒng)后不存在,只需驗(yàn)證子系統(tǒng)與外部的接口是否正確,大大地降低了驗(yàn)證難度,提高了效率。

圖9 子系統(tǒng)構(gòu)造前后工作量對(duì)比

6 結(jié)束語(yǔ)

本文提出了一種完整且預(yù)驗(yàn)證過(guò)的基于嵌入式CPU的加解密子系統(tǒng),該子系統(tǒng)由嵌入式CPU和多種加解密功能模塊組成,內(nèi)部CPU作為控制單元可控制子系統(tǒng)正常工作以減少對(duì)主CPU的訪問(wèn)。子系統(tǒng)在最初設(shè)計(jì)時(shí)進(jìn)行一次性投入,在以后的SoC設(shè)計(jì)和集成時(shí)可作為整體進(jìn)行復(fù)用,減少內(nèi)部功能模塊的互聯(lián)及驗(yàn)證時(shí)間,復(fù)用時(shí)通過(guò)硬件配置滿足各種需求,從而提高SoC的設(shè)計(jì)和驗(yàn)證效率。實(shí)驗(yàn)結(jié)果表明,構(gòu)造子系統(tǒng)后的SoC設(shè)計(jì)和驗(yàn)證工作量明顯小于構(gòu)造前,工作效率明顯提高。本文集成了最常用的加解密模塊,其他的如IDEA,ECC等加解密模塊,還需要開(kāi)發(fā)并集成到子系統(tǒng)中,使得子系統(tǒng)功能更強(qiáng),應(yīng)用面更廣。另外,子系統(tǒng)還需做進(jìn)一步的優(yōu)化,如內(nèi)部的加解密模塊目前是獨(dú)立的,盡可能實(shí)現(xiàn)加解密模塊間的硬件共享以減少面積是下一步需要研究的內(nèi)容。

[1] Open SystemC Initiative.SystemC Standard 2.2[EB/ OL].[2013-09-18].http://www.osci.org.

[2] OCP-IP.Open Core Protocol[EB/OL].[2013-09-18]. http://www.ocpip.org.

[3] The SPRIRIT Consortium.SPIRIT 1.4 Specification [EBOL].[2013-09-18].http://www.spiritconsortium. org/home/.

[4] Ma De,Huang Kai,Xiu Siwen,et al.An Automatic Soc Design Methodology for Integration and Verification [C]//Proc.of ICEEAC'10.Zibo,China:[s.n.], 2010:214-219.

[5] Hong Jin-Hua,Yao Tun-Kai,Lue Liang-Jia.Design and Implementation of a Low-power Cryptosystem SoC [C]//Proc.of Circuits Systems Conference.Cancun, Mexico:[s.n.],2009:321-329.

[6] 肖秋林.RSA加密子系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)[D].西安:西安電子科技大學(xué),2009.

[7] Young Chung-Ping,Lin Yen-Bor,Chia Chung-Chu.Software and Hardware Design of a Multi-cipher Cryptosystem[C]//Proc.of TENCON'09.Singapore:[s.n.], 2009:231-240.

[8] Glaser S T,Franzon A.Chip-package Co-implementation of a Triple DES Processor[J].IEEE Transactions on Advance Packaging,2004,27(1):194-202.

[9] C-SKY CK803 User Guide[EB/OL].[2013-09-18]. http://www.c-sky.com.

[10] Data Encryption Standard(DES),FIPS PUBS 46[EB/ OL].[2013-09-18].http://csrc.nist.gov/publications/ PubsFIPS.html.

[11] Advanced Encryption Standard(AES),FIPS PUBS 197 [EB/OL].[2013-09-18].http://csrc.nist.gov/ publications/PubsFIPS.html.

[12] Rivest R L,Shamir A,Adleman L.Method for Obtaining Digital Signatures and Public Key Cryptosystems[J]. Communications of the ACM,1978,21(2):20-26.

編輯 索書(shū)志

Encryption and Decryption Subsystem Based on Embedded CPU

WANG Jian-fei1,MA De2,XIONG Dong-liang3,CHEN Liang3,HUANG Kai3,GE Hai-tong4

(1.The First Research Institute of the Ministry of Public Security,Beijing 100048,China;

2.Institute of Microelectronics CAD,Hangzhou Dianzi University,Hangzhou 310018,China;

3.Institute of VLSI Design,Zhejiang University,Hangzhou 310027,China;

4.C-Sky Microsystems Co.,Ltd.,Hangzhou 310012,China)

To improve the efficiency of System-on-Chip(SoC)integration and verification for different applications of information security,a complete and pre-verified encryption and decryption subsystem based on embedded CPU is proposed.The subsystem includes cryptography modules such as RSA,DES,AES and so on.It can satisfy applications of different requirements on security levels.The embedded CPU in subsystem is a low-power and high-performance CPU,as a coprocessor for main CPU in SoC.It is responsible for controlling the operation of cryptography modules, reducing both the computation load of the main CPU and the power of SoC greatly.Integrating the pre-verified encryption and decryption subsystem as a whole to SoC,significantly reduces SoC design and integration effort and lowers the difficulty of SoC verification.Using gated clock technology,which manages the clock of cryptography modules based on their states,reduces the power of subsystem effectively.According to the CKSoC Integration method, the subsystem based on embedded CPU in different hardware configuration can be implemented quickly in the SoC integrator.Experimental results show that SoC design and verification work of constructing subsystem are reduced,and it improves work efficiency.

encryption and decryption subsystem;system reuse;System-on-Chip(SoC) integration;Advanced Encryption Standard(AES);Data Encryption Standard(DES)

1000-3428(2014)09-0183-07

A

TP309

10.3969/j.issn.1000-3428.2014.09.037

國(guó)家科技重大專(zhuān)項(xiàng)基金資助項(xiàng)目“寬帶多媒體集群系統(tǒng)技術(shù)驗(yàn)證(中速模式)”(2011ZX03004-004)。

王劍非(1979-),男,工程師、碩士,主研方向:移動(dòng)互聯(lián)網(wǎng)通信安全;馬 德,博士;熊東亮,碩士研究生;陳 亮,碩士;黃 凱,副教授、博士;葛海通,教授級(jí)高級(jí)工程師、博士。

2013-07-23

2013-09-23E-mail:jfwang@sonicom.com