基于AMBA總線的IIC協議IP核設計與驗證

王建雄,肖 明,余 龍

(1.江蘇科技大學計算機學院,鎮江212003;2.東莞市泰斗微電子有限公司,東莞523808)

基于AMBA總線的IIC協議IP核設計與驗證

王建雄1,肖 明2,余 龍1

(1.江蘇科技大學計算機學院,鎮江212003;2.東莞市泰斗微電子有限公司,東莞523808)

介紹了一種基于AMBA總線verilog HDL實現的IIC主機模式的IP核設計。該模塊能夠在標準和快速模式下運行,能夠靈活配置為十位地址尋址或七位地址尋址模式。詳細說明了該IP核的架構,各部分設計及狀態轉換過程。最后該模塊通過了系統驗證,并在xilinx FPGA上轉化為硬件電路實現了所有功能。

AMBA總線;Verilog HDL語言;IIC協議;IP核

1 引 言

現如今,電子類產品向著小型化、智能化、低功耗、低成本、高可靠性的方向發展。IIC僅有兩根線就實現了器件之間的雙工通信,它有著接口簡單、可擴展性好、功耗低等特點,已經被廣泛應用于各類數字系統中。而片上系統(System on Chip,SoC)已逐漸成為超大規模集成電路的發展趨勢,由于系統與外部電路的通信是通過外圍接口實現的,因此設計一個穩定可靠的外圍通信接口的IP就變得非常重要。正是在此形勢下設計了基于AMBA總線的IIC協議IP核,并通過系統仿真和FPGA上以硬件方式實現和驗證了設計的正確性和可靠性。

2 IIC協議簡介

IIC(Inter IC)總線是Philips公司于1992年推出的用于芯片間連接的雙向串口總線協議。它已經被廣泛應用于視/音頻領域、IC卡行業、家用電器、通訊設備及各類電子產品中,在智能儀器、儀表和工業測控領域也得到了廣泛應用。

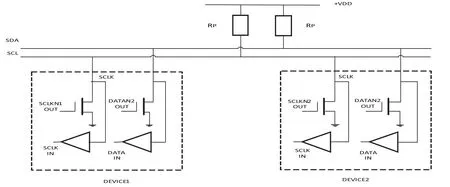

其電氣連接如圖1所示。

該協議使用一根數據線SDA和一根時鐘線SCL進行通信。時鐘由主機產生從機接收,主機在SCL低電平時發送數據到SDA上,從機在SCL為高電平時采樣SDA。在時鐘信號為高電平期間,數據線上的數據必須保持穩定,只有在時鐘線上的信號為低電平期間,數據線上信號才允許變化。

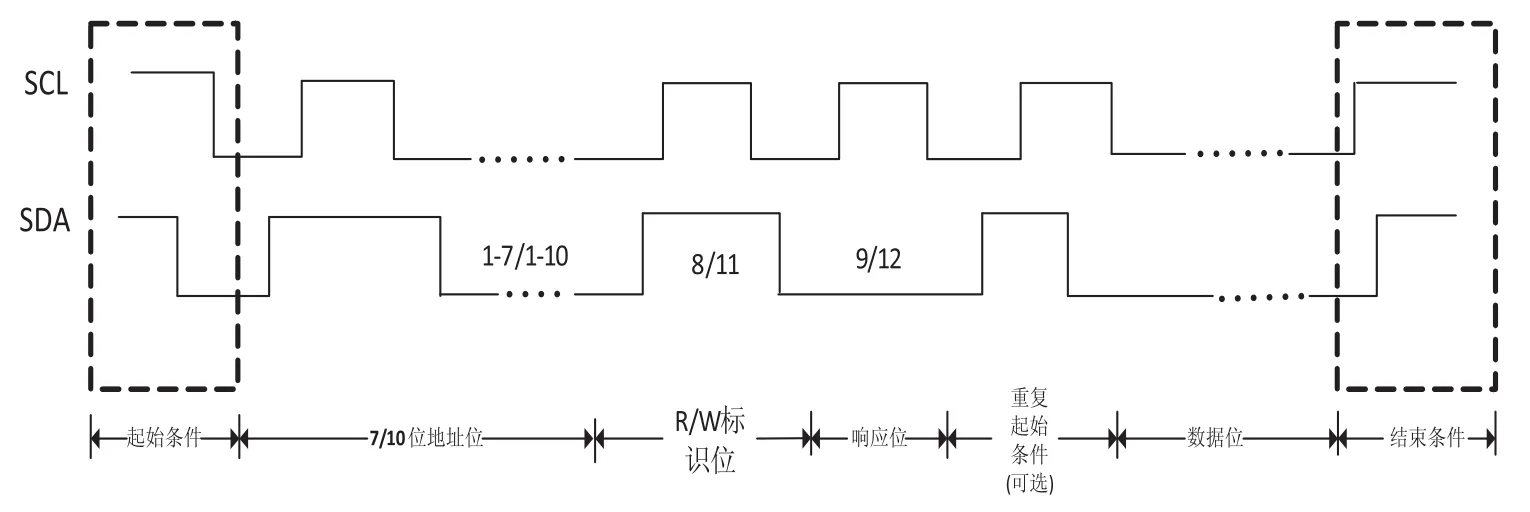

SDA上的數據格式分為起始條件、結束條件、重復起始條件、響應位和數據位。總線上每一個從器件都有一個唯一的標識地址。主機以一個起始條件加上從機地址尋址相應從機。當一次尋址失敗時,主機可以發送重復起始條件后繼續發送目標地址尋址從機。從機接收到自己的地址或者接收完一個字節的數據時必須將SDA拉低以給主機一個應答信號。主機接收完一個字節的從機數據時也必須給出應答信號。當傳輸完成時,由主機發送結束條件完成本次傳輸。一次完整的傳輸,其SDA和SCL上的電平如圖2所示。

圖1 SCL和SDA的電氣連接方式圖

圖2 一次完整的傳輸過程

在一次傳輸中,主機可以選擇七位或者十位尋址模式進行尋址,也可以選擇重復起始條件重新開始一次傳輸。當從機或主機處于忙狀態時可以選擇將SDA信號線拉低使IIC主機或從機處于等待狀態。

3 IIC協議IP核設計

該IP核實現了IIC協議的主機功能,可以靈活配置為標準和快速模式,支持7位和10位尋址模式,支持主、從機等待功能和重復起始條件尋址模式。

3.1 系統結構圖

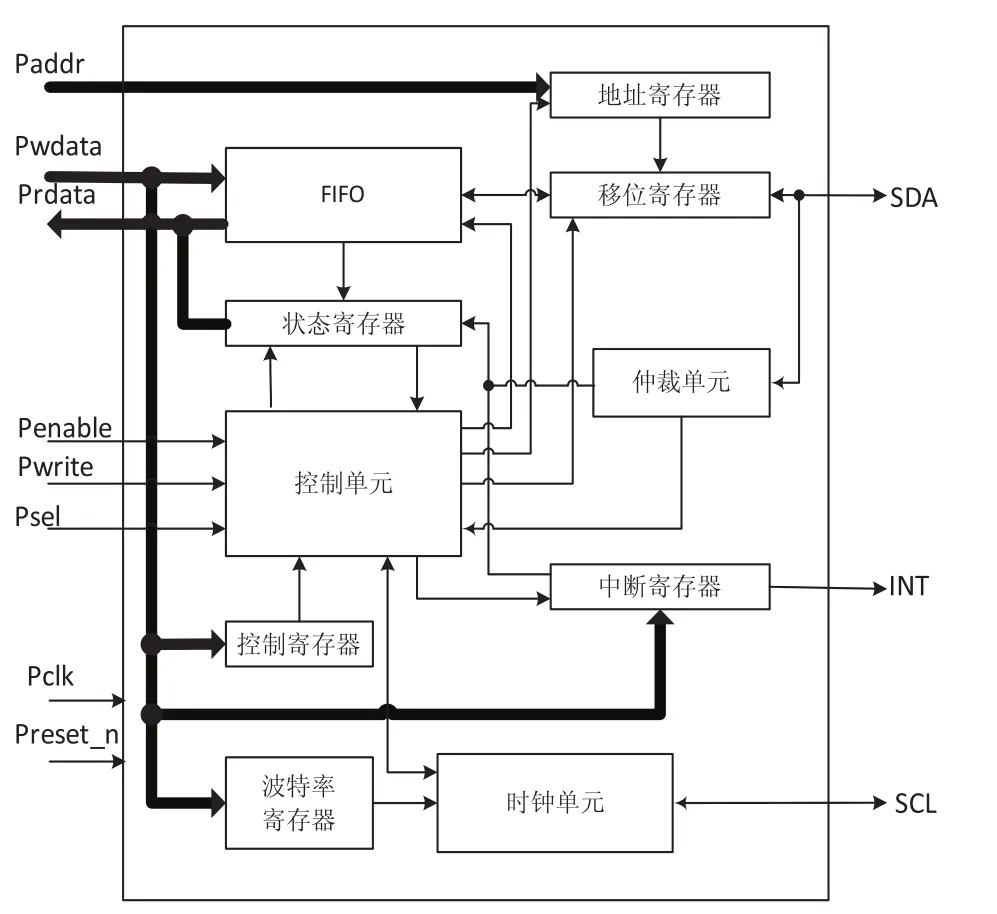

系統結構如圖3所示。由圖3可以看出,其結構可以分為控制部分和數據通道部分及時鐘部分。控制部分分為控制單位、仲裁單元、中斷寄存器和控制寄存器,由于控制寄存器僅僅起到存儲控制命令的作用,故在此將其劃分為控制部分。數據通道部分分為FIFO、地址寄存器、移位寄存器、狀態寄存器。時鐘部分分為時鐘單元和波特率寄存器。

3.2 各部分設計

3.2.1 控制部分設計

控制部分主要通過判斷控制寄存器、狀態寄存器的值和仲裁單元的狀態完成對數據通道部分的控制。控制部分的核心實現為狀態機,通過判斷各個條件實現狀態機的跳轉,從而產生相應控制信號控制數據通道部分中數據流的流動。控制部分控制地址寄存器中地址的裝載,移位寄存器中數據的移出,狀態寄存器的讀取和FIFO的讀寫控制。

圖3 系統結構圖

3.2.2 數據通道部分設計

數據通道部分主要實現數據的暫存和轉換。其中FIFO實現數據緩存,它能協調高速APB協議和低速IIC協議之間的通信。移位寄存器能實現數據的串并轉換。地址寄存器能實現地址的存儲和發送。狀態寄存器主要存儲IIC工作時的各狀態,用于控制部分狀態機的跳轉和傳送給CPU調試使用。

3.2.3 時鐘部分設計

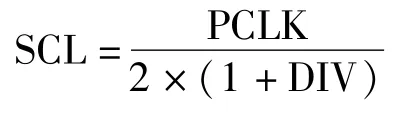

時鐘模塊工作時,首先需要配置波特率寄存器。通過波特率寄存器中的值計算出SCL分頻出的時鐘頻率,其計算公式如下,DIV值由波特率寄存器中的值確定。

時鐘單元產生SCL時鐘并且采樣SCL線上信號。當SCL時鐘線被從機拉低時主機需要啟動等待功能。

3.3 IP核的狀態機設計

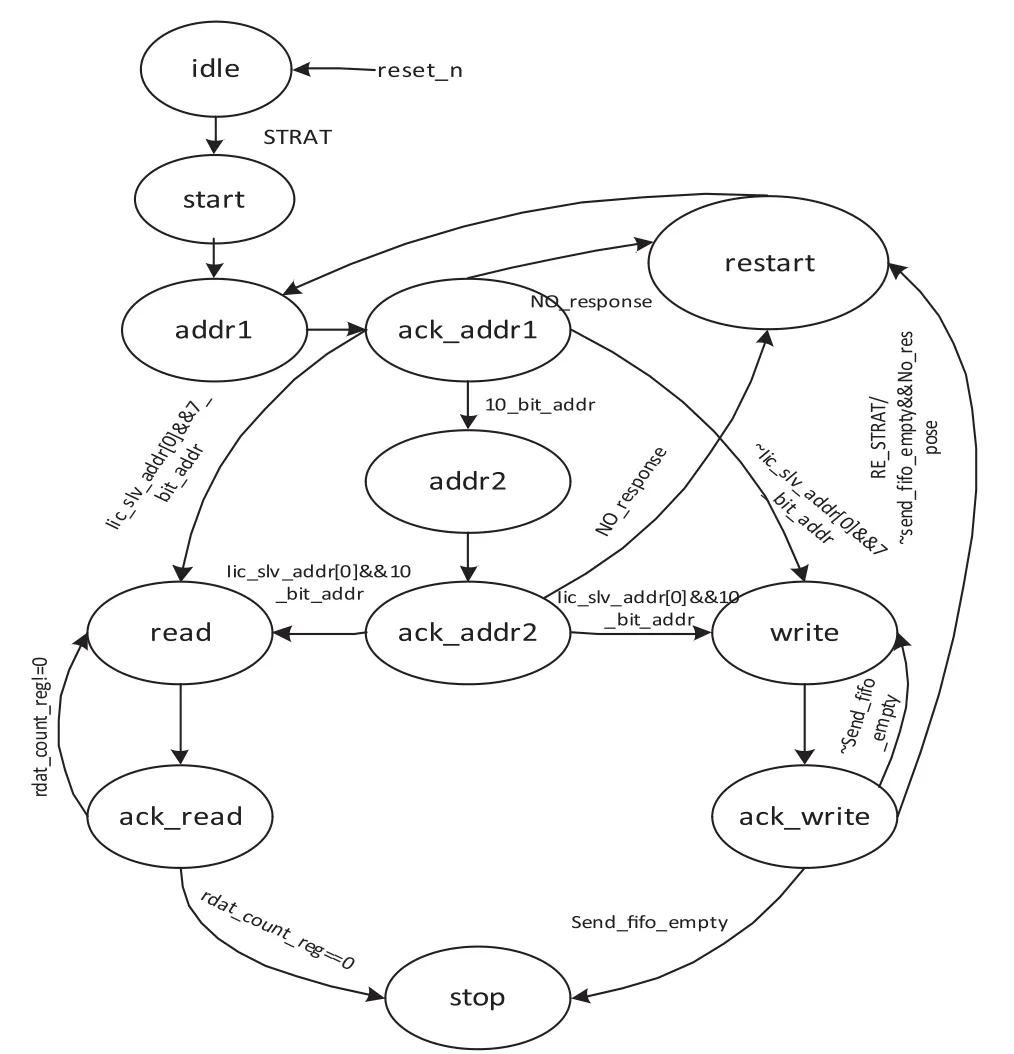

該IP核的邏輯狀態轉換如圖4所示,各個狀態的詳細說明如下。

圖4 邏輯狀態轉換圖

Idle狀態:當IIC沒有得到運行指令或程序被復位時,程序就處于idle狀態。在這個狀態時SDA和SCL對外輸出高電平。

start狀態:當控制寄存器的START位被置位時,程序由idle狀態跳轉到start狀態。程序位于該狀態時SCL輸出高電平,同時SDA產生一個由高到低的跳轉。

addr1狀態:在該狀態時會將地址寄存器中的七位地址或者十位地址的高位地址發送給從機,并且采樣SDA信號線判斷主機是否丟失仲裁。當地址均發送完并且沒有丟失仲裁時程序跳轉到ack_addr1狀態中。

ack_addr1狀態:程序在該狀態時會檢查是否有從機應答信號。如果SDA被拉低則表明從機接收地址正確。若從機地址為7位,則程序根據最低的位進行相應跳轉;若從機地址為10位,則程序跳轉到addr2狀態。如果SDA未被拉低,表明從機接收第一個字節有誤,程序跳到restart狀態。

addr2狀態:當從機地址是10位地址時,程序把10位地址的低八位發送出去并自動跳轉到ack_addr2狀態。

ack_addr2狀態:程序檢查SDA是否被拉低,若被拉低則根據跳轉,否則程序跳回restart狀態。

restart狀態:當控制寄存器的RESTRART位被置位或者發送FIFO非空而從機無應答或者程序處于ack_addr無應答時,程序都會跳轉到該狀態。程序處于此狀態時會向從機發送一個重復起始條件并自動跳轉到addr1狀態。

read狀態:主機在每個SCL的上升沿采樣SDA,并將采樣值存在移位寄存器中,當完成一個byte的接收時將移位寄存器中的值存入FIFO,并且程序跳到ack_read狀態。

ack_read狀態:當完成一個byte的接收并且主機還要繼續接收數據時,主機需要發送一個響應給從機并且跳入read狀態,否則程序跳轉到stop狀態。

write狀態:主機將FIFO中的數據以byte為單位發給從機,發送完后自動跳轉到ack_write狀態。

ack_write狀態:當FIFO非空,并且檢測到從機的應答時程序跳回write狀態,當FIFO為空時程序跳轉到stop狀態。

stop狀態:SCL為低電平并且SDA從低電平翻轉到高電平,完成一個結束狀態的傳輸。

4 IP驗證

4.1 驗證平臺介紹

驗證該模塊,需要搭建一個testbench平臺,該平臺由激勵模塊、APB主機模型、DUT、輸出響應模型、監視器、比較器等組成,各模塊介紹如下。

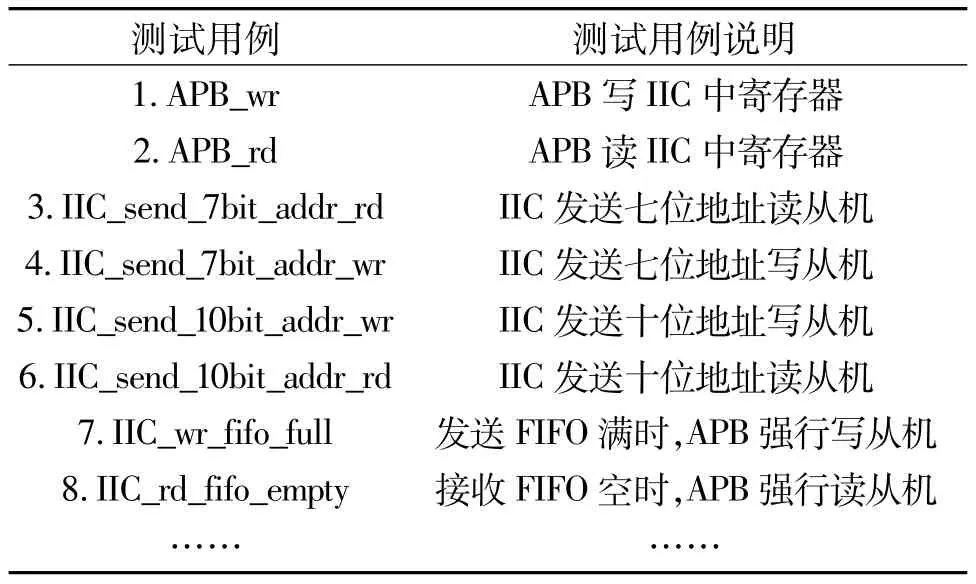

激勵模塊:激勵模塊的主要功能是提供給測試平臺各種case以使IP運行于不同的狀態。在驗證該模塊中使用的測試用例如表1所示。

表1 驗證測試用例表

APB主機模型:APB主機模型主要模擬APB的總線時序,使激勵數據能按APB的協議要求傳輸給被測設計。

DUT(Design Under Test):即被測的IP設計。

輸出響應模型:其主要功能是對被測設計輸出的數據按照協議做出應答,在該設計中選擇的輸出響應模型有IIC從機模型和EEPROM。

監視器:監視器監視輸入和輸出協議中的位傳輸,以及起始、結束、復位等條件的正確性。如果檢測到數據與期望數據不一致,那么測試平臺就給出錯誤報告信息。

比較器:比較器的主要功能是檢測輸入和輸出各數據,并比較其是否正確。如果發送數據和測試數據不正確,那么測試平臺將生成測試錯誤報告。

4.2 測試用例介紹

以上測試用例主要測試了該IP模塊在正常和異常情況下對發送的命令是否能做出正確響應和處理。在使用測試用例對DUT進行測試的時候要根據設計的功能點全面考慮需要測試的功能,并加入一些極端情況下的測試激勵。

4.3 驗證結果

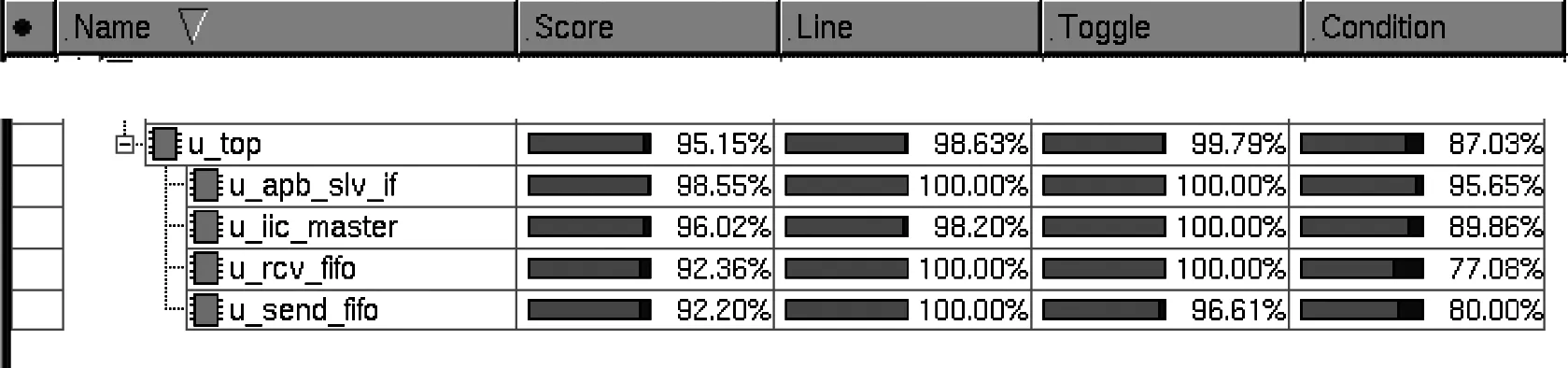

當驗證完成后,該設計在synopsis公司的VCS上進行覆蓋率統計。其覆蓋率統計如圖5所示。

圖5 IP的驗證統計覆蓋率

上圖中各覆蓋率沒有達到100%的原因分析如下:

(1)由于case語句中各條件已完備,導致default分支不能被覆蓋到,所以行覆蓋率沒有達到100%。

(2)由于設計中增加的一些保護性代碼,在一般驗證中難以滿足該情景,故導致條件覆蓋率不能到達100%。

(3)由于該設計中某些位的值按功能不會變化,故翻轉覆蓋率不能實現100%的覆蓋。

(4)FIFO模塊的讀寫使能不能同時有效。

5 仿真與實現

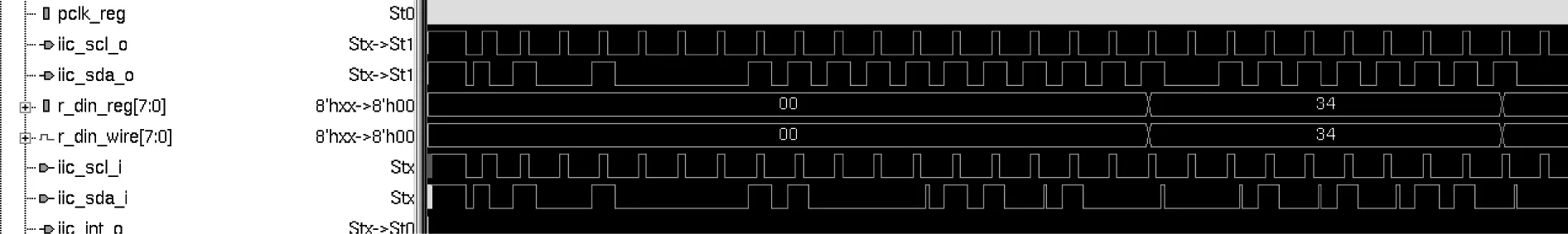

該設計通過測試平臺的驗證后并在VCS上進行了仿真,其仿真結果完全滿足預期設計,如圖6所示。

圖6 IIC仿真波形圖

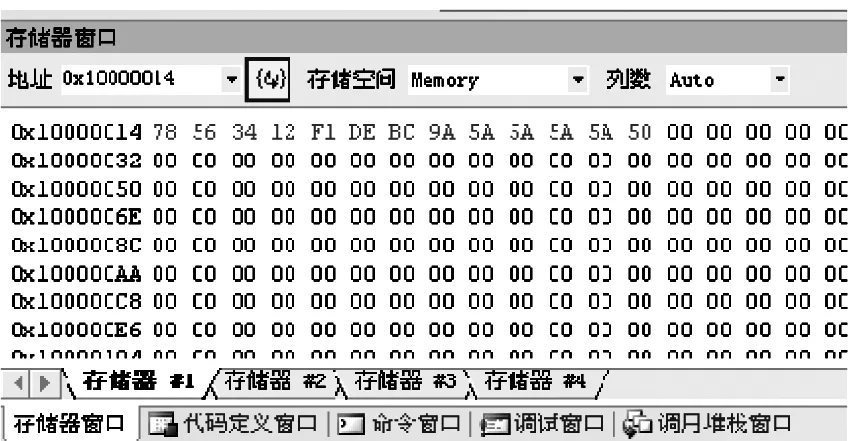

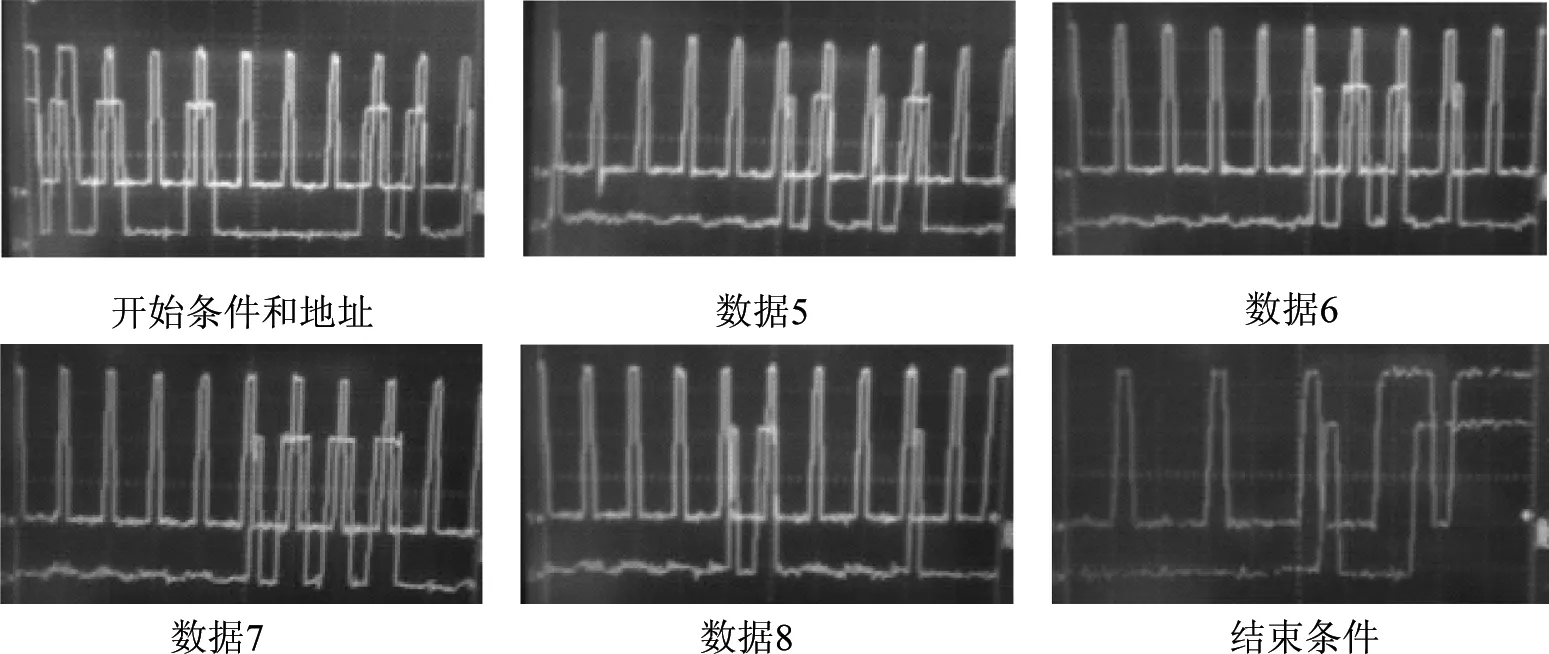

然后該設計在XILINX公司的ISE軟件上進行了編譯、映射和綜合生成最終的bit文件下載到FPGA板上。下載好了的FPGA與單片機模擬的IIC從機進行通信,FPGA寫單片機數據12345678 9ABCDEF1 5A5A5A5A 00000005,其結果如圖7所示。單片機接收FPGA的數據,用示波器觀察其波形如圖8所示。

6 結束語

基于IP的SOC模塊化設計能讓產品以更快的速度推向市場,而且一個精心設計并經過多次驗證過的IP其可靠性和資源利用率都會很高。該設計采用可重用的Verilog HDL代碼編碼風格,并最終通過Xilinx FPGA驗證。經驗證其性能完全滿足預期要求,其實現不依賴具體的FPGA和AISC工藝。

圖7 IIC從機接收到數據圖

圖8 示波器觀察波形圖

[1]wayne wolf著,現代VLSI設計:基于IP核的設計(第4版)[M].李東生等譯,北京:電子工業出版社,2011-07.

[2]ciletti,M.D著.Verilog HDL高級數字設計[M].張雅倚等譯,北京:電子工業出版社,2005-01.

[3]ARM Limited.AMBA Specification Rev2.0[S].1999.05.

[4]Philips semiconductors.THE I2C-BUSSPECIFICATION VERSION 2.1[S].2000.01.

[5]俞偉,徐寧儀,羅飛,等.IIC總線控制器IP核設計[J].世界科技研究與發展,2005(1):18-21.

[6]王前,屋淑泉,劉喜英.基于FPGA的IIC總線接口實現方法[J].微電子技術,2002(2):22-24.

[7]田耘,徐文波,著.Xilinx FPGA開發實用教程[M].北京:清華大學出版社,2008-11.

Design and Verification of IP Core of IIC Protocol Based on AMBA Bus

WANG Jian-xiong1,XIAO Ming2,YU Long1

(1.School of Computer Science,Jiangsu University of Science and Technology,Zhenjiang 212003,China;2.Techtotop Micro-electronics Company of Dongguan City,Dongguan 523808,China)

This article describes an IP core design of IIC master,base on AMBA bus,which implements by verilog HDL.The module can runs in standard mode and quick mode,and it can be flexibly configured to be ten bit or seven bit addressing mode.This article describes the structure of IP core,and its design and status conversion process.Finally,the module has passed the system-level verification and all functions have been implemented in Xilinx FPGA hardware.

AMBA Bus;Verilog HDL;IIC protocol;IP core

10.3969/j.issn.1002-2279.2014.01.002

TN492

:B

:1002-2279(2014)01-0004-05

王建雄(1988-),男,四川巴中人,碩士研究生,主研方向:數字集成電路設計。

2013-09-30