深亞微米并行CRC32編碼芯片的設計和實現

郭寶增,吳鵬飛

(河北大學 電子信息工程學院,河北 保定 071002)

CRC的全稱是循環冗余校驗(cyclic redundancy check),是一種非常著名的檢錯手段,在通信和數據存儲領域得到廣泛應用.其特點是檢錯能力極強,開銷小,易于編碼器及檢測電路實現.從檢錯能力來看,其不能發現的錯誤的幾率在0.004 7%以下.著名的通訊協議X.25的FCS(幀檢錯序列)采用的是CRC-CCITT;ARJ,LH等壓縮工具軟件采用的是CRC32;磁盤驅動器的讀寫采用了CRC16;通用的圖像存儲格式GIF,TIFF等都使用CRC作為檢錯手段[1].

1 CRC32算法研究

1.1 LSFR串行編碼算法

CRC32屬于線性分組碼的分支,同時還具有循環特性,符合一般循環碼的編碼方法[2],其過程可以采用LSFR實現編碼電路,這種電路主要由移位寄存器和異或門組成[3-4].對于CRC32校驗碼,生成多項式為

g(x) =x32+x26+x23+x22+x16+x12+x11+x10+x8+x7+x5+x4+x2+x+1.

(1)

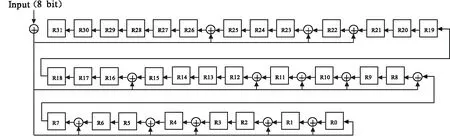

以8 bit的數據輸入為例,其硬件實現框圖如圖1所示.

圖1 LSFR串行編碼電路Fig.1 LSFR serial encoder circuit

圖1中,32位移位寄存器用于存儲CRC32校驗碼,稱其為CRC寄存器.編碼前將寄存器各位置1,每個時鐘周期1 bit數據輸入,通過移位和異或運算,CRC寄存器中的數據進行隨之更新,8個時鐘周期后,數據輸入完畢,此時CRC寄存器的值即為CRC32的碼序列,該算法原理簡單,便于硬件實現,但效率不高,主要應用于串行通信.

1.2 并行CRC32算法

從本質上說,LSFR算法是一種串行算法,針對LSFR電路效率低的問題,本文從LSFR電路的結構入手,通過相應的邏輯運算推導出高效并行的CRC32編碼算法.

(2)

(3)

(4)

(5)

(6)

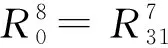

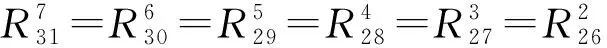

將(3),(4),(5),(6)式代入(2)式,可以求得

(7)

即移位寄存器R0經過8個時鐘后的狀態值可以表示為移位寄存器R30,R24的初始值與輸入數據D7,D1的異或運算,這樣就可以將LSFR中8 bit的串行輸入數據轉換為等效的并行輸入,將其記做CRC0.按照上述的推導原則,可以求得其他31個寄存器經過8個時鐘后的狀態值.

8 bit并行輸入,經過并行運算單元運算之后,將運算結果存儲到移位寄存器R0-R31,移位寄存中的值有2個用途:當前時鐘周期下,直接以運算結果的形式作為輸出;下一時鐘周期作為保護數據反饋到并行運算單元,共同作用到下一時鐘周期.

2 并行CRC32算法的FPGA驗證

在算法研究的基礎上,鑒于ASIC(application specific integrated circuit)流片成本高,風險大,因此大規模量產之前需要事先對芯片的設計進行FPGA驗證.通過驗證,一方面可以確保系統邏輯功能的正確;另一方面可以說明系統的時序基本可以滿足設計要求[3].

依據推導出的邏輯關系,編寫并行CRC32算法的verilog代碼[5]

module crc(

input[7:0] data_in,

input crc_en,

output [31:0] crc_out,

input rst,

input clk);

reg[31:0] lfsr_q,lfsr_c;

assign crc_out = lfsr_q;

always @(*) begin

lfsr_c[0] = lfsr_q[30] ^ data_in[7] ^ lfsr_q[24] ^ data_in[1];

?

lfsr_c[31] = lfsr_q[23] ^ lfsr_q[29] ^ data_in[2];

end

always @(posedge clk, posedge rst) begin

if(rst) begin

lfsr_q <= {32{1’b1}};

end

else begin

lfsr_q <= crc_en ? lfsr_c : lfsr_q;

end

end

endmodule

生成的并行CRC32編碼模塊如圖2所示.

圖2中data_in為8位數據輸入端;crc_en為使能端,只有當crc_en為高電平時,編碼器才進行編碼工作;rst為復位信號(高電平有效),當電平為高時,進行初始化;clk為時鐘信號;crc_out為32位CRC編碼輸出端.

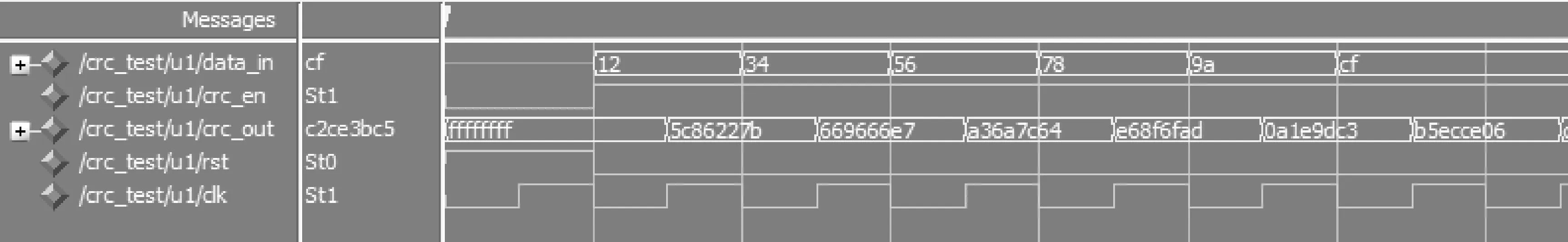

通過編寫testbench,利用Modelsim軟件對生成的編碼模塊進行功能仿真,其仿真結果如圖3所示.

圖3 并行CRC32編碼電路功能仿真結果Fig.3 Function simulation result of Parallel CRC32 encoder circuit

仿真輸入數據為8’h12,8’h34,8’h56,8’h78,8’h9a,8’hcf;得到的CRC32校驗碼為16’h5c86227b,16’h669666e7,16’ha36a7c64,16’he68f6fad,16’h0a1e9dc3,16’hb5ecce06,通過觀察仿真結果,其編碼結果與理論計算的結果一致.

將編譯后的工程文件下載到DE2-70開發板,通過實驗檢測,可以得到一致的輸出結果,至此芯片代碼的FPGA驗證工作結束.

3 并行CRC32編碼芯片的實現

FPGA的使用費用太高,資源利用率較低;在功耗、設計密度以及產品的運算速度方面相對ASIC來說存在相當程度的劣勢,因此,為了實現產品的大規模生產,必須進行系統邏輯的版圖GDS II設計.設計過程采用中芯國際180 nm的數字工藝庫,主要使用Synopsys公司的Design Compiler邏輯綜合軟件,和Cadence公司的Soc Encounter自動布局、布線軟件實現版圖的GDS II文件設計.

3.1 編碼電路的邏輯綜合

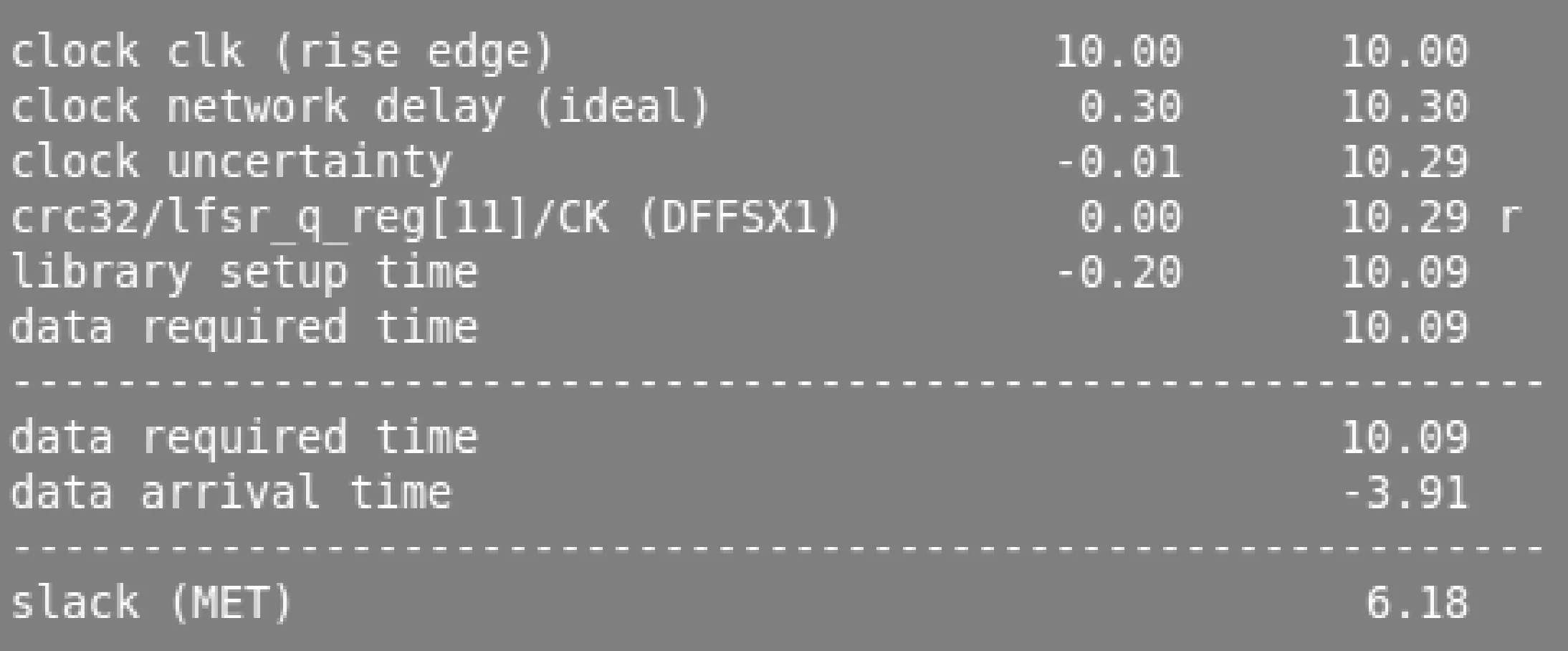

使用Design Compiler軟件,對編碼電路的verilog代碼進行邏輯綜合,其主要工作包括:一方面將硬件語言描述的行為級電路、RTL級電路轉換到基于工藝庫的門級網表[6];另一方面要根據綜合產生的時序報告,對綜合過程中的各項參數進行修改,以保證時間余量(slack)為給定時鐘的30%以上,這是由于綜合過程中設置的連線負載只是工藝庫提供的延時參數,并不是實際延時,必須以足夠的slack為后續的實際布局、布線提供充足的延時空間,圖4為綜合后的時序報告.

圖4 邏輯綜合時序報告Fig.4 Logic synthesis timing report

從圖中可以看出給定的時鐘clk為10 ns,而綜合后的slack為6.18 ns,超過要求的最少時間余量3 ns,說明綜合過程可以提供充足的時間余量用于布局、布線.

將滿足上述要求綜合后的verilog文件(門級網表文件)和sdf文件(時序約束文件)進行導出,采用Formality形式驗證工具對綜合后的網表進行邏能的驗證,形式驗證相對于時序仿真的優勢在于,能夠以較短的時間消耗比較綜合前、后電路邏輯功能是否一致.

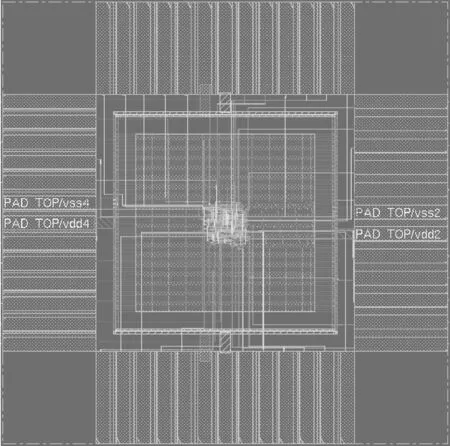

3.2 編碼電路的布局、布線

使用Soc Encounter軟件,導入邏輯綜合后的verilog文件和sdf文件,完成版圖GDS II的設計,設計過程需要針對版圖的面積、時序進行分析,采取面積約束、優化布局布線、時鐘數綜合等方法達到合理的版圖設計,隨后完成版圖的LVS比較和DRC規則檢查,得到的版圖文件如圖5所示.

圖5 并行CRC32編碼芯片版圖Fig.5 Parallel CRC32 encoder chip layout

3.3 編碼電路的時序仿真

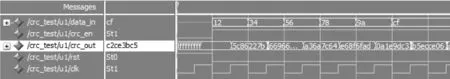

上面提到過對于驗證電路功能是否與原始代碼一致可以采用形式驗證工具Formality.而本設計是優化的并行電路結構,其結構簡單,使用的邏輯單元較小,時序仿真的耗時可以接受,因此可以采用Modelsim對編碼電路進行時序仿真加以驗證,時序仿真的結果如圖6所示.

圖6 并行CRC32編碼芯片時序仿真結果Fig.6 Timing simulation result of Parallel CRC32 encoder chip

通過比較功能仿真和時序仿真結果,可以證明所設計芯片完全能夠實現CRC32的并行編碼功能.

4 結語

在研究CRC算法及編碼原理的基礎上,從代碼編寫到GDS II版圖生成,完成了數字集成電路前端到后端的整個設計流程;所實現的編碼芯片能夠以高效的速率完成編碼工作.此外,本文介紹的芯片設計方法對了解和掌握數字芯片設計思想起到一定的指導作用.

參 考 文 獻:

[1] 張樹剛,張遂南,黃士坦.CRC校驗碼并行計算的FPGA實現[J].計算機技術與發展,2007,17(2):56-62.

ZHANG Shugang,ZHANG Suinan,HUANG Shitan.CRC Parallel Computation Implementation on FPGA[J].Computer Technology and Development,2007,17(2):56-62.

[2] 樊昌信,張甫翊,徐炳祥,等.通信原理[M].北京:國防工業出版社,2001.

[3] SHIEH M D,SHEU M H,CHEN C H,et al.A systematic approach for parallel CRC computations [J].Journal of Information Science and Engineering,2001,17:445-461.

[4] RAMABADRAN T V,GAITONDE S S.A tutorial on CRC computations[J].IEEE Micro,1988(8):62-75.

[5] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2003.

[6] 韓雁,洪慧,馬紹宇,等.集成電路設計制造中EDA工具實用教程[M].杭州:浙江大學出版社,2007.