基于FPGA的多路光纖數據同步技術

牛戴楠,史俊宏,黃 鏐,方振發

(1. 中國船舶重工集團公司第七二四研究所,南京 211153;2. 78020部隊,云南 昆明 650000)

基于FPGA的多路光纖數據同步技術

牛戴楠1,史俊宏2,黃 鏐1,方振發1

(1. 中國船舶重工集團公司第七二四研究所,南京 211153;2. 78020部隊,云南 昆明 650000)

針對當前相控陣雷達數字TR組件的設計,提出了一種基于光纖信號的同步方法,使得數據傳輸和雷達主觸發同步集成在同一根光纖中,從而省去了傳統采用專用觸發進行同步控制的大量觸發線,簡化了相控陣系統有源面陣設計。經在實驗板FPGA驗證,該光纖同步技術能有效實現多板多片FPGA間的信號同步控制及處理,為后續的數字相控陣有源面陣的同步設計提供了更多的選擇空間。

光纖數據同步;COMMA字符對齊;高速數據傳輸

0 引 言

數字相控陣雷達大量的數字TR組件在工作時必須同步產生或接收信號。任何一個組件的不同步都會造成數字TR組件間的幅相不一致,造成數字波束合成錯誤,降低空間合成效率、從而影響有源面陣的指標,嚴重時會導致整個雷達威力下降、測向誤差精度降低[1]。

傳統相控陣雷達使用等長屏蔽同軸電纜來傳輸同步觸發信號,但在強電磁環境中屏蔽層和接頭處的微小瑕疵將降低屏蔽性能,影響觸發信號的傳輸,造成觸發信號的不同步;繼而通過改進,使用等長差分電纜作為同步觸發信號的傳輸介質,差分電纜能有效抵抗電磁干擾,但增加了設備的連接電纜數量,增大了設備生產和調試難度,并且隨電纜長度增加將導致觸發沿的變化變緩,從而影響觸發信號的同步性。同時考慮到,現代相控陣雷達每個數字TR組件與后端的信號處理或數據處理分機均有光纖連接作為上行或下行數字信號的傳輸通道。因此,本文提出了一種利用光纖在傳輸數據的同時提供同步觸發的方式,實現各組件同步控制,從而避免觸發線受到的各種電磁干擾,同時又能減少設備間的連接線纜,提高有源面陣的集成度[2-3]。

1 光纖信號同步

1.1 光纖同步原理

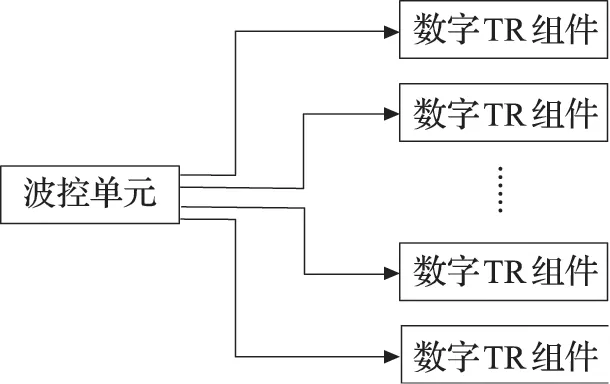

光纖同步是數據發送端將特殊字符用作同步頭,接收端在接收到包含有特殊字符的數據包后解出特殊字符的時刻作為同步觸發信號沿。原理框圖見圖1。

圖1 光纖同步原理框圖

本文中,作為控制命令和信息交互的中樞,波控單元根據資源調度模塊發送的控制命令產生數字TR組件的布相控制、通道處理流程控制、頻率點控制等命令。相控陣雷達資源調度器發送控制命令給波控單元后,波控單元產生TR組件的控制命令,將作為雷達主觸發的特殊字符作為信息包頭,與控制命令一起打包后通過光纖發送到每個TR組件。TR組件收到信息包后,從包頭中解出該特殊字符作為系統的統一觸發信號。在該觸發下,TR組件再根據接收到的控制命令同步打開發射或接收通道,進行對空輻射或接收回波信號。由于每個TR組件的工作時鐘頻率及相位一致,所以只要確保每個TR組件在同一時刻收到波控單元發送的數據包,則通過數據包解碼得到特殊字符后就能確保所有TR組件的同步。

1.2 光纖數據同步

光纖數據同步首先要確定FPGA發送端從并行數據產生到數據以串行方式從FPGA的RocketIO的輸出整條通路上的延時,接收端串行數據從FPGA的RocketIO接口輸入到轉換成并行數據后的整條通路上的延時。只有當這兩個延時是固定值時,光纖同步才具有可行性。在本系統中,采用的是Xilinx公司的FPGA,因此在設計時充分針對了該FPGA內的高速收發器RocketIO的收發延遲特性。

1.2.1 發送端同步

發送端延時的不確定主要由RocketIO的發送數據緩沖器導致,所以發送端的同步首先要旁路發送數據緩沖器。發送端的數據緩沖器主要用于解決RocketIO發送時鐘和FPGA用戶時鐘兩個時鐘域之間時鐘的相位不一致。當數據緩沖器被旁路后,需要由發送端的相位對齊電路來替代數據緩沖器的功能。相比數據緩沖器的延時不確定性,相位對齊電路的延時是固定的,這樣就確保了發送端多路光纖之間數據是同時發送的。發送端相位對齊控制流程如圖2所示。

圖2 發送端相位對齊控制流程圖

當發送端檢測到系統復位信號后,對所有發送通道進行復位,同時對發送端的相位對齊電路進行復位,然后檢測發送端復位是否完成,如果復位完成則檢測相位是否對齊;如果復位沒有完成,則繼續對相位對齊電路保持復位狀態;若發送端復位完成,但相位對齊電路一直沒有準備好,則延時一段時間后再次對相位對齊電路進行復位,直到發送端復位完成并且兩個時鐘域的時鐘相位對齊。

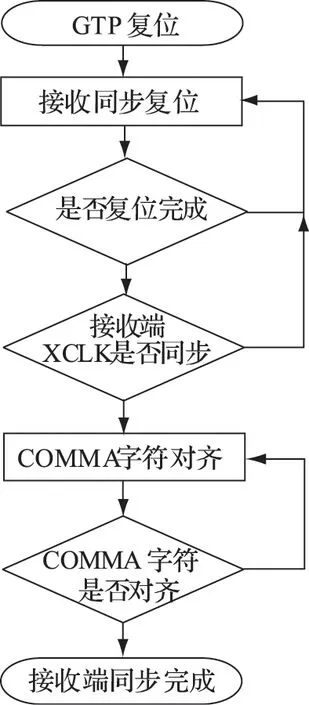

1.2.2 接收端同步

接收端延時的不確定性主要源于接收端RocketIO數據緩沖器和COMMA字符對齊電路。與發送端類似,接收端的數據緩沖器主要用于解決RocketIO接收時鐘和FPGA用戶時鐘兩個時鐘域之間時鐘的相位不一致。當數據緩沖器被旁路后,需要由接收端的相位對齊電路來替代數據緩沖器的功能。

串行數據在轉換為正確的并行數據前需要與特征邊界對齊,對齊后的串行數據才能正確地轉換為并行數據。這個特征邊界被稱為COMMA字符。在Xilinx的RocketIO中可用選擇COMMA字符的自動對齊。但是,COMMA字符的自動對齊導致了接收通路上延時的不確定,所以接收端的同步不僅僅是旁路接收數據緩沖器并控制接收相位對齊電路,還必須控制COMMA字符的對齊,已確保接收通路的延時是固定的。圖3展示了接收端同步的流程。

系統復位時,同時對接收通道進行復位。若復位完成后則判斷接收端兩個時鐘域的時鐘相位是否對齊;若復位沒有完成則繼續等待復位完成信號,同時繼續保持對接收端相位對齊電路的復位狀態。當接收端的兩個時鐘域的時鐘相位對齊后,進行COMMA字符對齊,若COMMA字符對齊,則表示接收端同步完成;若COMMA字符沒有對齊,則對輸入的串行數據進行移位,再次進行COMMA字符的對齊操作。

圖3 接收端同步流程圖

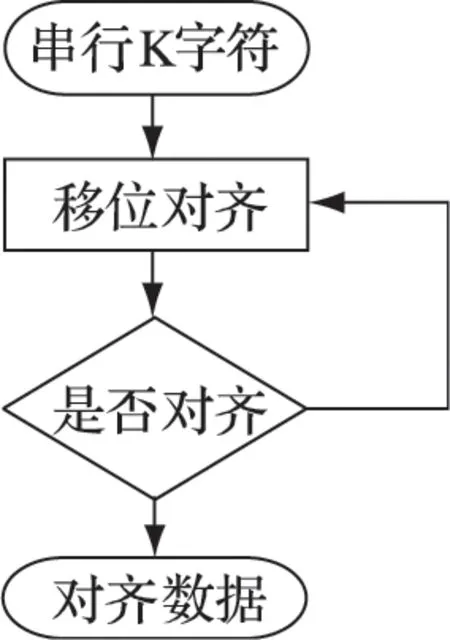

1.2.3 COMMA字符對齊

COMMA字符通常選用控制字符(K字符)表示。接收端需要連續接收一定數量的COMMA字符才能對齊。這就要求發送端在每次同步時先發送一定數量的COMMA字符,使得接收端有足夠的數據量完成接收端對齊。COMMA字符對齊控制流程圖如圖4所示。

圖4 COMMA字符對齊控制流程圖

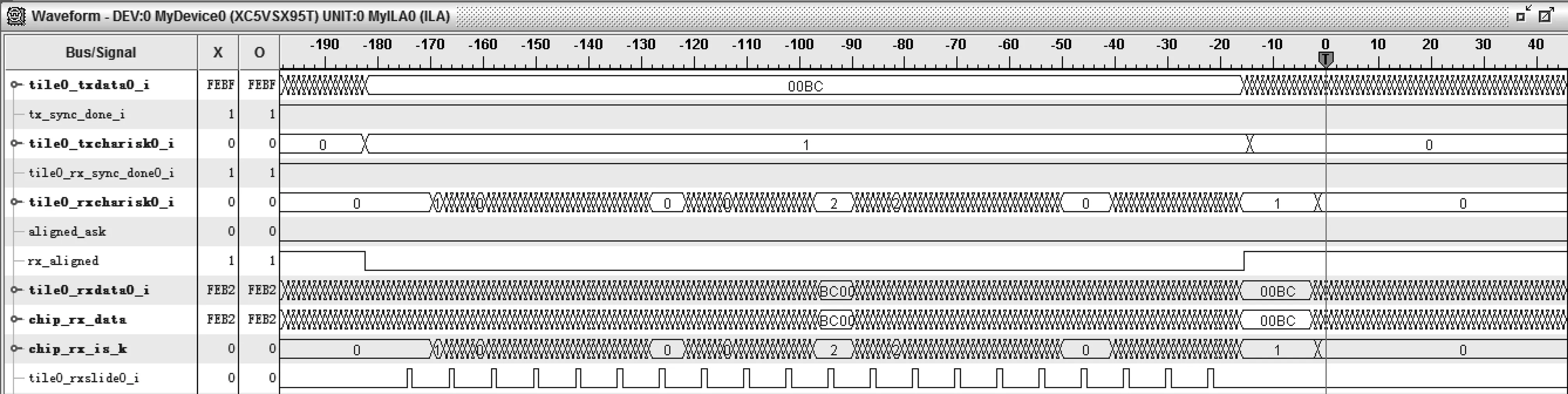

光模塊將光信號轉換為電信號以串行方式通過RocketIO接口進入FPGA接收邏輯電路,接收端收到連續的串行數據后首先以滑窗的方式將窗口內的數據與作為對齊特征邊界的K字符比較,如果相同則表示串行數據已經對齊;如果不同則表示串行數據還沒有對齊,將滑窗移動一位,再次進行比較,直到窗內的串行字符為特定K字符。只有串行數據對齊后,后續的串行數據才能轉換為正確的并行數據。圖5為COMMA字符對齊控制的chipscope數據抓取圖。

圖5 COMMA字符對齊控制

從圖5中可以看出,在每次重新對齊時,發送端連續發送167個COMMA字符,接收端通過20次移位后完成COMMA字符的對齊,每次對齊發送端和接收端的延時都是固定的。至此,光纖同步的必要條件已經具備。串行數據一旦對齊后,后續數據即可轉換為正確的并行數據。COMMA字符不作為接收端產生觸發信號的特殊字符,可以使用其他K字符作為觸發產生的特殊字符。發送端先發送200個時鐘周期的COMMA字符,作為產生觸發的K字符緊跟在COMMA字符后,作為數據包頭;接收端采用狀態機的形式先在200個時鐘周期內進行接收數據對齊,對齊后開始檢測產生觸發信號的控制(K)字符。當檢測到這個特殊的控制(K)字符后,產生同步觸發信號。

2 結束語

對相控陣雷達的數字TR組件而言,光纖是必不可少的傳輸數據方式。光纖同步技術的實現大量減少了相控陣有源面陣與后端信號預處理分系統線纜連接,增強了系統的可靠性,降低了調試難度和故障排查難度。本文提出的這種光纖同步技術,經在實驗板FPGA上驗證,能有效實現多片FPGA間同步處理,程序采用VHDL語言編寫,經過后期移植也可以應用到數字有源相控陣中的數字TR組件中。

[1] Virtex-5 FPGA RocketIO GTP Transceiver User Guide,www.xilinx.com,2009

[2] Virtex-5 FPGA User Cuide,www.xilin.com,2010

[3] M.I斯科尼克.雷達手冊[M].王軍,等譯.3版.北京:電子工業出版社,2010.

Multiplex optical fiber data synchronization technology based on FPGA

NIU Dai-nan1, SHI Jun-hong2, HUANG Liu,FANG Zhen-fa1

(1. No. 724 Research Institute of CSIC, Nanjing 211153; 2. Unit 78020 of the PLA,Kunming 650000)

In view of the design of digital TR modules in current phased array radars, a new synchronization method based on the optical fiber signal is proposed, in which the data transmission and radar main trigger are integrated into the same optical fiber. Therefore, a mass of special trigger lines used for the synchronization control conventionally are not required to simplify the design of active planar arrays of phased array systems. Through the verification of the test board FPGA, this optical fiber synchronization technology can effectively implement the signal synchronization control and processing between multiple FPGAs, providing more space to choose from for the synchronization design of active planar arrays of the following digital phased array radars.

optical fiber data synchronization; COMMA character alignment; high-speed data transmission

2014-09-08;

2014-10-12

牛戴楠(1982-),男,工程師,碩士,研究方向:高速電路設計及信號處理;史俊宏(1988-),男,助理工程師,研究方向:陣列信號處理;黃鏐(1986-),男,工程師,碩士,研究方向:通信信號處理;方振發(1989-),男,助理工程師,碩士,研究方向:寬帶無線通信。

TN958.92

A

1009-0401(2014)04-0039-03