基于眾核處理器的AVS并行解碼器的設計與實現

吳 杰,張文軍,高志勇,張小云

(上海交通大學 圖像通信與網絡工程研究所,上海 200240)

1 AVS并行解碼器

AVS是我國具備自主知識產權的第二代信源編碼標準,其第二部分為視頻部分,在2006年經信息產業部批準正式成為國家標準[1]。AVS目前正處于大規模產業化的推廣期,因此研究AVS在眾核平臺下的并行解碼有著重要的意義。

AVS標準的視頻部分與MPEG-2以及H.264類似,也采用了基于塊匹配的編碼框架[2]。相對于MPEG-2標準,AVS同H.264都采用了更加復雜的運動估計等技術,使得復雜度大幅增加,經過優化在主頻有限的單核處理器上也難以實現高清視頻(1 080p)的實時(25 f/s或更高)解碼[3]。

多核以及眾核處理器的發展以及并行計算為高清視頻碼流的實時解碼提供了一種可行的解決方案,設計良好的并行解碼器能達到接近線性的并行加速比。本文提出并實現了一種采用功能與數據混合并行的高清實時AVS并行解碼器,并在Tilera公司的Tile-Gx36平臺[4]上開發實現,可用6個核實現1路高清AVS碼流的解碼。

2 AVS解碼器結構

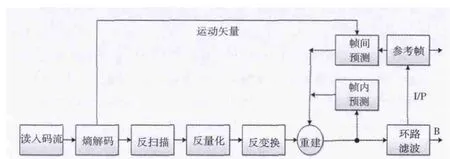

AVS的視頻標準也采用了基于塊匹配的混合編碼框架,AVS解碼器的實現流程如圖1所示。

圖1 AVS解碼器流程圖

解碼器先對讀入的AVS碼流進行碼流解析和熵解碼,得到殘差系數等信息,再經過一系列運算可以到殘差值,然后再根據編碼模式的不同選擇不同的預測方式進行預測運算,再經過重建即可得到重建圖像。解碼得到的I幀、P幀可以作為參考幀。

3 AVS并行解碼器設計方案

3.1 并行策略

利用多核處理器實現任務的并行,一般有兩種常見的方法,一種是功能并行,一種是數據并行[5]。功能并行的基礎是流水線模型,可以將要實現的功能拆分成多個功能模塊,通過流水線并行就可以實現功能上的并行。功能并行本質上是利用時間上的并行性來實現并行加速的作用。AVS解碼器可以分為VLD和IQ/IDCT,幀內預測、MV預測以及濾波等。可以對這些功能模塊進行劃分,然后再利用多核處理器的并行性來并行處理這些功能模塊。

數據并行是將要處理的數據進行劃分,將劃分的數據交給不同的核處理,由此實現數據處理上的并行。對于AVS碼流,每一幀的數據可以劃分為多個Slice,每一個Slice可以由多個宏塊行組成,本文AVS并行解碼器的設計采用基于宏塊行的并行。

功能并行時,多個核之間需要進行數據通信,因此會引入通信負載。而且功能并行時只有各個功能模塊耗時接近時才能有更好的并行加速比。數據并行時數據之間存在依賴性關系,如果數據依賴性差,則CPU將會有很多的時間處于空閑等待狀態,并行效率就會下降,所以進行數據并行時必須考慮劃分數據模塊的依賴性。

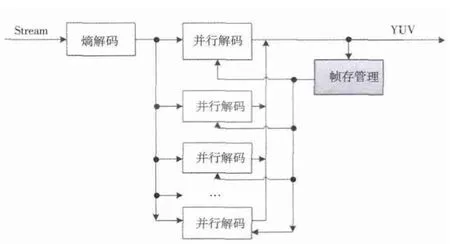

本文提出的是一種數據并行和功能并行相結合的混合模型來實現AVS并行解碼器的設計。AVS解碼器中熵解碼與其他功能模塊是串行執行的,按照這個思路可以將AVS解碼器劃分為兩大模塊,即VLD模塊以及并行解碼模塊。VLD模塊和功能解碼模塊之間符合流水線并行的方式,通過這種機制可以實現功能上的并行。在并行解碼模塊中多個核處理劃分后的數據,由此實現數據上的并行。

AVS并行解碼器框圖如圖2所示,主線程負責熵解碼創建解碼任務,多個線程進行并行解碼。

圖2 AVS并行解碼混合模型框圖

3.2 調度策略

本文采用任務池模型實現子任務的調度,任務池模型通常都是由主線程和工作線程組組成。主線程負責創建任務添加到任務池中,工作線程組從任務池中獲取任務并執行,當工作線程執行完當前任務后,立即去任務池中獲取任務再執行,直到任務池為空。采用任務池模型的動態分配方案能夠減少核處于等待的時間,提高并行處理的效率。

3.3 AVS并行解碼器設計

本文采用任務池模型的調度機制實現AVS并行解碼器。在任務池模型中,為了高效率地實現并行,需要滿足以下兩個條件:1)任務池中有足夠多的任務;2)任務池中的任務具備弱依賴性[6]。如果任務池中沒有足夠的任務,工作線程組中將會有線程處于等待狀態;如果任務池中的任務依賴性過強,則這些任務只能按順序執行。所以進行任務劃分時顆粒度必須合理。在AVS并行解碼器的實現過程中,采用了幀間并行和幀內宏塊行并行,以保證并行解碼器的效率。

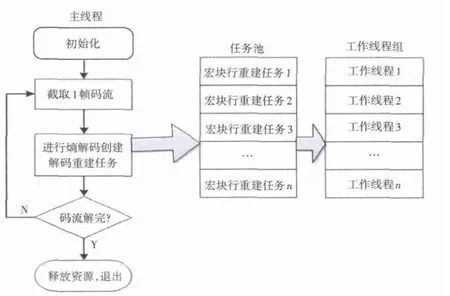

3.3.1 AVS并行解碼器實現架構

整個AVS并行解碼器的實現架構由主線程和工作線程組兩個部分組成。并行AVS解碼器的實現架構如圖3所示,主線程負責解析輸入碼流,熵解碼,創建宏塊行為單位的解碼重建任務并添加到任務池中。工作線程從任務池中取出一個任務做解碼重建,工作流程如下:1)幀間預測亮度宏塊重建;2)幀內預測亮度宏塊重建;3)亮度宏塊BS值計算及環路濾波;4)幀間預測色度宏塊重建;5)幀內預測色度宏塊重建;6)色度宏塊環路濾波。

圖3 并行AVS解碼器實現架構

3.3.2 幀間并行和宏塊行并行

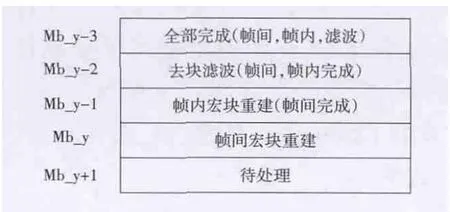

如圖2所示,本文設計的AVS并行解碼器采用了功能并行和數據并行混合的模型,如果只用1個主線程進行熵解碼,隨著工作線程的增加,解碼任務不足,處于休閑等待的線程數增加,并行加速比就會降低。為了解決上述問題,引入幀間并行機制來創建更多的解碼任務提供給工作線程組執行。在并行解碼模塊的設計中,如果一個線程完成一幀所有后續數據的解碼,任務顆粒度仍然較大,隨著工作線程的增加,容易出現線程等待任務的情況,為此需要進行更小的顆粒度劃分,本文設計的AVS解碼器采用了宏塊行并行的機制。根據解碼的工作流程,采用了3行宏塊并行的任務劃分機制,考慮亮度和色度宏塊,則一共可以同時處理6行宏塊,如圖4所示。Mb_y行宏塊進行幀間宏塊的重建時,其上一行Mb_y-1行宏塊已經完成幀間宏塊的重建,正在進行幀內宏塊的重建,而Mb_y-2行則已經完成幀間宏塊重建和幀內宏塊重建,正在進行去塊濾波。

圖4 宏塊行并行框圖

4 解碼器優化

對于AVS-P2視頻解碼器而言,反量化、反變換以及插值模塊消耗的大多數時間,為了實現高清實時解碼,除了充分利用多核的并行性外,還需要利用處理器提供的單指令多數據(SIMD)指令集進行計算的優化。

4.1 開發平臺介紹

Tile-Gx36是美國Tilera公司2012年發布的眾核處理器,它是由36個核組成的,每個核的頻率是1.2 GHz。核間的通信主要是通過核間互聯網絡imesh完成。Tilera提供的SIMD指令集能完成16位和8位的SIMD操作。Tilera的寄存器寬度為64位,所以可以同時處理4個16位的運算或者8個8位的運算。

4.2 反量化/反變換SIMD優化

AVS反量化表64個整數均大于32 768,只可用無符號16位表達,最高位均為1。而Tilera公司提供的SIMD指令集僅支持有符號16位的乘法運算,為了使用Tilera公司提供的乘法指令,將反量化表中的每個數減去32 768,用有符號位表示。對反量化公式做如下修正

1個像素塊的殘差一般是用8位表示的,AVS變換矩陣的系數值較大,如果用8位來表示,變換計算的中間結果可能會發生溢出,所以在進行中間運算的時候需要進行數據擴展,第一次運算將數據由8位擴展到16位,第二次運算將數據由16位擴展到32位,最后將輸出結果壓縮為16位的整型數據。Tilera提供的SIMD指令集提供了相應的數據位擴展和壓縮指令。

4.3 插值SIMD優化

AVS解碼器與H.264的樣本插值不同,采用的是4抽頭濾波器進行樣本插值。從AVS的插值流程能夠看出,對于類似同位置的像素點,進行的運算相同,因此可以利用SIMD指令并行處理。考慮到并行處理過程中會發生數據位溢出,需要將8位擴展為16位整型數據進行計算。AVS參考軟件采用了大量的循環來計算每個分像素的值,執行這些循環會引來額外的負載。利用SIMD指令除了可以并行處理數據提高速度外,還很大程度地減少了循環次數,極大地提高了運行速度。

5 實驗結果和分析

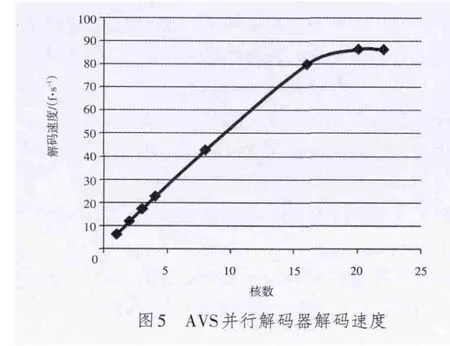

實驗采用的測試碼流為用AVS參考軟件rm52j編碼的1 080p碼流,編碼方式為IBBP,碼率為10 Mbit/s。未做任何優化前,單核解碼速度為2.9 f/s,經過優化后單核解碼速度為6.1 f/s。采用5幀并行以及宏塊行并行,解碼速度與核數之間的關系如圖5所示。采用幀級并行和宏塊行并行的情況下6個核可以實現30 f/s的解碼速度,達到高清實時的解碼。

從圖5中可以看出,當核數小于15時,有著接近線性的并行加速比,核數再增加,解碼速度不會繼續增加。這是由于主線程創建的解碼任務有限,隨著核數的增加,核間通信的負載增加,處理器實際解碼的時間減少。

6 總結

本文設計并在Tile-Gx36平臺上實現了AVS高清實時并行解碼器,并行機制采用了幀級并行和宏塊行并行的二級混合并行機制,調度方式采用了基于任務池的調度策略。實驗表明,本設計有著良好的并行加速比,對于10 Mbit/s的1 080p的AVS碼流,6個核可以實現實時解碼。因此,1片Tile-Gx36可以實現6路AVS高清碼流的實時解碼。

:

[1]GB/T20090.2—2006,信息技術先進音視頻編碼第2部分:視頻[S].2006.

[2]黃鐵軍,高文.AVS標準制定背景與知識產權狀況[J].電視技術,2005,29(14):4-7.

[3]牛旭寧,張遠,馬思偉,等.AVS解碼器復雜度分析[J].計算機應用與軟件,2010,27(5):67-70.

[4]Tilera[EB/OL].[2013-10-20].http://www.tilera.com.

[5]葉朝敏,陳穎琪,高志勇.基于多核處理器的高清實時MPEG-2—H.264轉碼器設計[J].電視技術,2012,36(21):15-19.

[6]田韜,李鵬,張悠慧.H.264并行解碼的設計與實現[J].微計算機信息,2008(14):114-115.

作者簡介:吳 杰(1990—),碩士生,主研視頻編解碼;

張文軍(1963—),博士生導師,主要研究方向為圖象通信與多媒體技術、高清晰度電視等;

高志勇(1957—),博士生導師,主要研究方向為高速視頻圖像處理、數字電視等;

張小云(1977—),碩士生導師,主要研究方向為視頻編解碼、高速視頻處理等。

責任編輯:時 雯 收稿日期:2013-11-14