一種模數混合結構的延遲鎖相環設計

唐 寧,張蓮蓮,張 可

(1.中國電子科技集團公司第四十七研究所,沈陽110032;2.東北大學理學院物理系,沈陽110004)

一種模數混合結構的延遲鎖相環設計

唐 寧1,張蓮蓮2,張 可1

(1.中國電子科技集團公司第四十七研究所,沈陽110032;2.東北大學理學院物理系,沈陽110004)

數字系統通信的不斷發展,多種延遲鎖相環結構的出現滿足了不同應用要求。提出了一種模/數混合結構的延遲鎖相環,改善了傳統模擬鎖相環和傳統數字鎖相環各自的缺點,在數字系統中作為集成電路模塊單元使用。采用TSMC的0.25μm,1P5M,CMOS混合信號工藝進行加工制備,模塊單元面積140×190μm2。

延遲鎖相環;混合結構;集成電路模塊

1 引 言

隨著集成電路工藝技術進入深亞微米時代,對微處理器和圖像處理等系統電路提出了加快時鐘頻率和降低功耗的要求。集成電路模塊之間的時鐘同步成為設計上關注的重要問題,因而,大量的設計努力集中在高性能的數字接口電路與數字系統之間的通訊上。

延遲鎖相環作為一階反饋系統,具備無條件穩定,快速鎖定時間及更好的防抖動特性,一直廣泛地應用于微處理器、存儲器及集成電路通訊中。傳統的模擬延遲鎖相環,具有更好的防抖動和偏移特性,但是受工藝、溫度等因素影響嚴重;傳統的數字延遲鎖相環,具有更快的鎖定時間,更好地抑制工藝、溫度因素的影響,但是更差的防抖動和偏移特性。提出了一種新型的模數混合結構的延遲鎖相環,能夠有效地改善上述問題,作為IC模塊嵌入在C8051F500系列微處理器系統中。

2 結構及原理

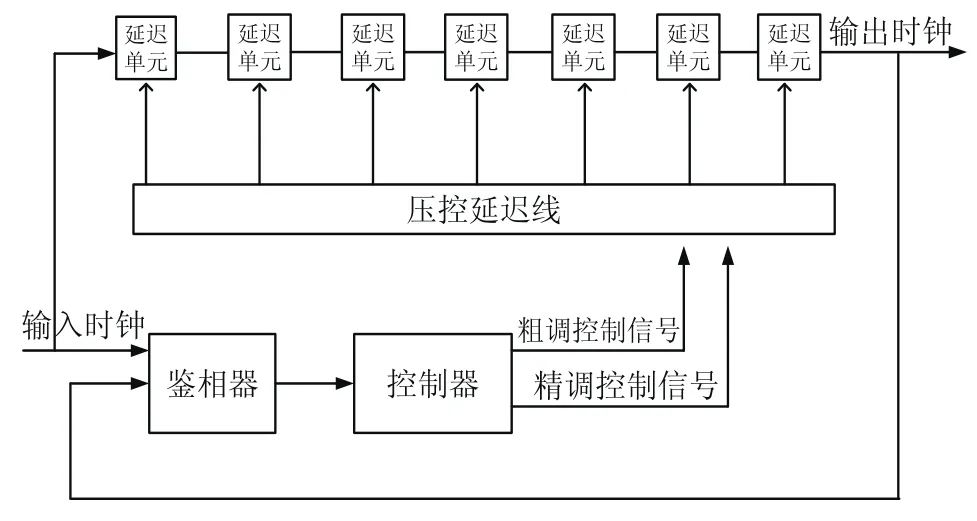

圖1給出模數混合結構延遲鎖相環的框圖,主要由鑒相器、控制器、壓控延遲線和延遲單元四部分組成。鑒相器單元捕捉輸入時鐘和輸出時鐘相位差,通過控制器轉換為N位粗調控制信號和M位精調控制信號,依次調節壓控延遲線中電荷泵結構的充放電電流路數,從而達到延遲單元延遲時間的功能,最終保證輸出時鐘和輸入時鐘相位差趨近于零,進入鎖定狀態。

精調控制信號產生的延長時間是對粗調控制信號產生的1LSB延遲時間(td)的插值,精調最小延遲分辨率可以表示為:

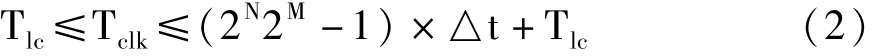

當延遲鎖相環進入鎖定狀態時,總延遲時間為一個時鐘周期,延遲鎖相環能夠處理的時鐘頻率范圍為:

式中,Tclk是輸入時鐘周期;Tlc是當所有控制信號都為低時延遲鎖相環固有的延遲時間;設定的輸入時鐘范圍越大,容納外界干擾鎖定的能力越強。由式(1)和式(2)可知,可以增大N或td來擴展輸入時鐘頻率范圍,但增大N意味著增大電路硬件的復雜度,增大td意味著降低時序的分辨率,因此,輸入時鐘頻率范圍的設計是這兩個因素的折中考慮。

圖1 混合結構延遲鎖相環功能框圖

3 主要單元模塊設計

3.1 延遲單元

如圖2所示,延遲單元通過壓控延遲線調節環路濾波電容的充電電流(Imirr)的鏡像值,設定充電電壓的上升時間,依次調節延遲單元的延遲時間。

圖2 延遲單元功能框圖

3.2 壓控延遲線單元

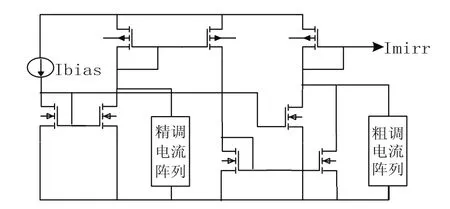

如圖3所示,壓控延遲線單元的主要功能是利用2N個粗調控制位和2M個精調控制位調節鏡像電流(Imirr)與偏置電流(Ibias)的比例關系,控制延遲單元的延遲時間。精調電流與粗調電流的權重關系由電流鏡加權實現。

圖3 壓控延遲線單元功能圖

4 仿真結果

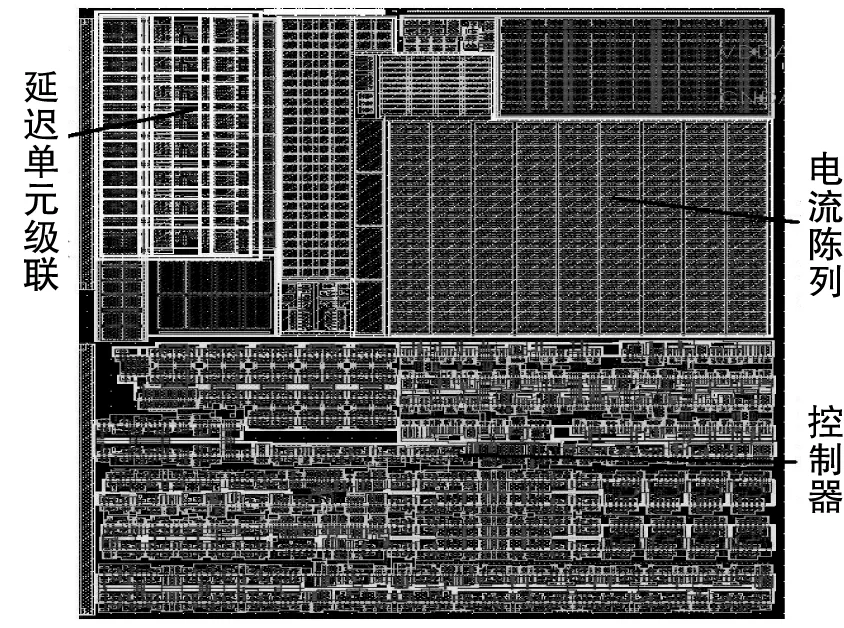

本電路基于TSMC的0.25μm,1P5M,CMOS混合信號工藝進行加工制備,版圖結構如圖4所示。

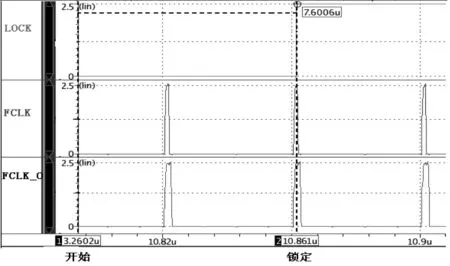

利用CALIBRE工具對版圖數據抽取進行仿真,得到圖5所示的波形。由圖可知,對于25MHz的輸入時鐘信號,電路經過192個時鐘周期,進入鎖定狀態,捕獲時間7.6μs。仿真結果證明了該混合結構延遲鎖相環性能的優良性。

圖4 延遲鎖相環版圖結構

圖5 TT,25℃下25MHz輸入頻率鎖定波形圖

5 結束語

提出了一種數模混合結構的延遲鎖相環電路,它能夠有效地改善傳統的數字DLL和模擬DLL各自的不足之處,可以作為單片電路或單元模塊應用到微處理器等數字系統通訊領域。

[1] YMoon,et al.An all-analog multiphase delay-locked loop using a replica delay line for wide-range operation and low-jitter performance[J].IEEE J.Solid-State Circuit,2000,35(3):377-384.

[2] Y Okajima,M Taguchi.Digital delay locked loop an design technique for high-speed synchronous interface[J].IEICE Trans.Electron,1996,E79-C(6):798-807.

[3] HH Chang,S J Liu.A wide-range and fast-locking all-digital cycle-controled DLL[J].IEEE J.Solid-State Circuit,2005,40(3):661-670.

Design of A Kind of Hybrid-structure Delay Locked Loop

TANG Ning1,ZHANG Lian-lian2,ZHANG Ke1

(1.The47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China 2.Physics Department,Collage of Sciences,Northeast University,Shenyang 110004,China)

With the development of digital communication system,the advent of several structures of delay locked loop can satisfy the demand of specs in different applications.An analog-digital hybridstructural delay locked loop,as an IC-modular utilized in a large scale digital system,which improved the drawbacks of traditional analog DLL and digital DLL,is described in this paper.TSMC 0.25μm,1P5M,CMOSmixed-signal process are used in the circuitwith themodular area of 140×190μm2.

Delay locked loop(DLL);Hybrid-structure;IC-modular

10.3969/j.issn.1002-2279.2014.02.004

TP492

A

1002-2279(2014)02-0011-02

唐寧(1981-),男,遼寧鞍山人,工程師,主研方向:混合信號集成電路設計研究。

2013-03-15