一種機載雷達無源探測方式的設計

何錫君,郭 巖

(1.南京電子技術研究所, 南京210039)

(2.中國人民解放軍駐沈陽飛機工業(集團)有限公司軍事代表室, 沈陽110000)

0 引言

無源探測設備是一種在不發射電磁波信號前提下,被動接收對方雷達、通信等傳感器(通常稱為輻射源)主動發射的電磁波信號,通過測量接收到的電磁波信號的具體參數提取對方輻射源目標相關特征,獲取對方輻射源目標位置和航跡等信息的被動探測系統,具有隱蔽性好、探測距離遠、抗干擾能力強及在復雜電磁干擾環境下生存能力強等優點。美軍APG-77、APG-81等機載火控雷達均具備無源探測能力。機載雷達進行無源探測時,可以利用其高增益的雷達天線,采用天線窄波束掃描、外輻射源信號接收及處理,探測目標輻射源的特征及位置。由于雷達天線的高增益特性,其探測距離通常超過有源探測距離。因此,機載雷達的無源探測方式可以作為其優先獲取戰場態勢及瞬時變化的情報信息的有效補充和重要手段之一。

1 無源探測系統構成

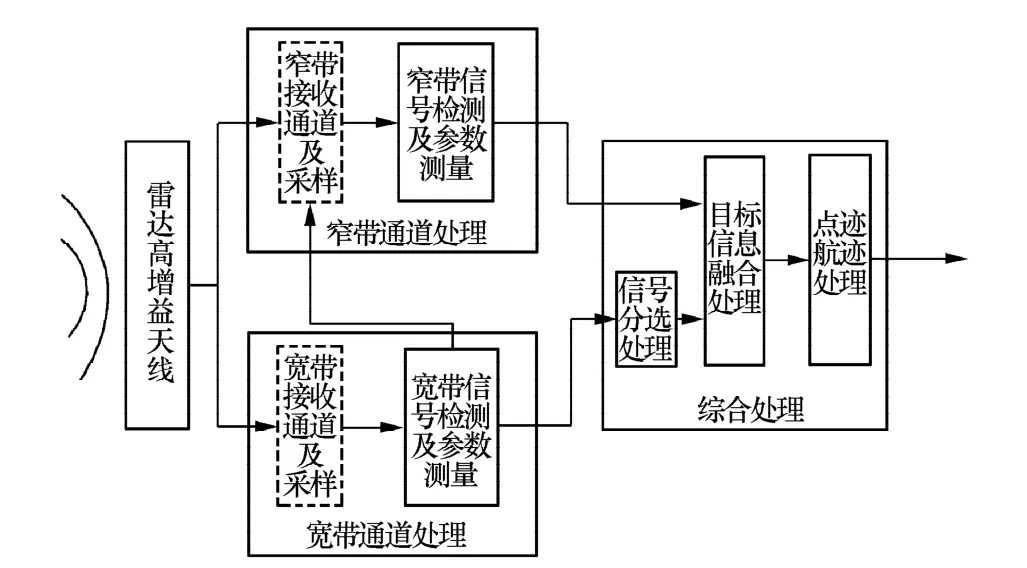

機載雷達無源探測系統的主要組成部分包括天線、寬帶、窄帶接收通道及綜合處理等,如圖1所示。

圖1 一種機載雷達無源探測方式的設計框圖

由圖1可知,機載雷達的無源探測方式的工作過程:

(1)雷達天線被動接收外部輻射的電磁波信號,經過天線和差網絡形成和、方位差、俯仰差三路通道射頻信號。其中,和通道射頻信號功分后分別輸出到寬帶通道處理機和窄帶通道處理機;和信號、方位、俯仰差射頻信號輸出到窄帶通道處理機。和通道射頻信號經寬帶通道處理機中的寬帶接收通道及采樣、寬帶信號數字信號化檢測及參數測量處理后,得到外部外輻射源的基本信息。

(2)根據相關探測策略選取重點監測的輻射源信號,控制窄帶處理通道處理機同時進行和、方位差、俯仰差三路射頻信號的窄帶接收及采樣,完成窄帶信號檢測及參數測量。

(3)在通用綜合處理機中完成對寬帶通道處理機輸出結果的信號分選處理,對信號分選結果與窄帶通道處理機輸出結果進行目標信息融合處理,對點跡信息進行點跡航跡等處理。

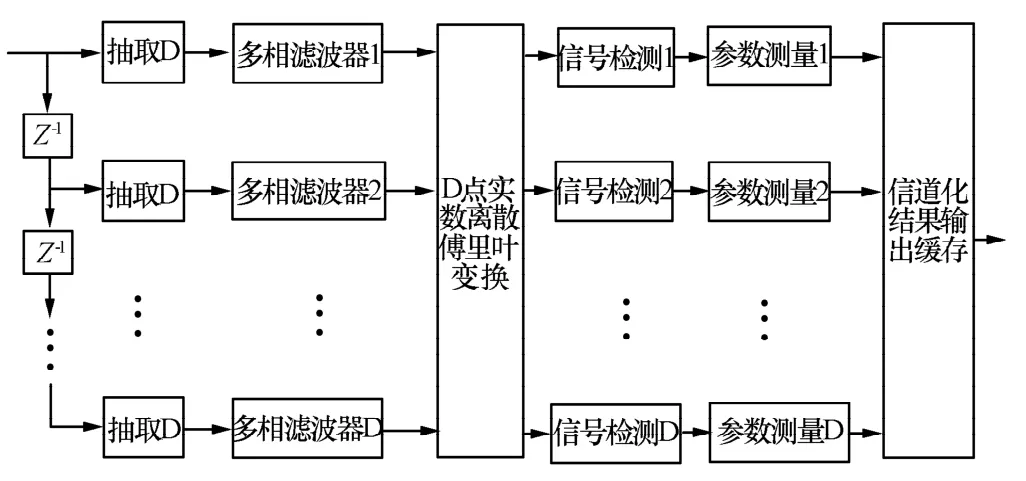

1.1 寬帶信號檢測及參數測量

機載雷達寬帶信號檢測可以通過采用數字信道化技術來實現。數字信道化接收機具有能夠處理同時到達的多個信號,較高的截獲概率、準確的參數測量能力和一定的信號分選、識別能力等優點,因而在寬帶信號檢測方面得到了較為廣泛的應用。

本文首先采用一種基于離散傅里葉變換(DFT)和多相濾波的高效信道化結構,進行寬帶輸入目標信號的數字信道化接收;其次,分別對各子信道化輸出的數據,進行信號檢測判斷,確定其中是否存在目標;然后,對檢測到目標的信道再進行信號相關參數(如目標信號類型、載頻CF、脈寬PW、脈幅PA及到達時間等)的測量等處理;最后,形成對應輻射源目標的脈沖描述字(PDW),便于后續的信號分選處理。

針對圖2中數字信道化接收的信號檢測,較為常用的一些信號檢測算法有時域能量檢測法、時域自相關法及頻域譜分析法。參數測量主要是對信號類型、CF、PW、PA、TOA等參數的測量。由于信道化接收機輸出為復信號,可以通過各信道輸出信號的實部和虛部計算得出瞬時幅度和瞬時相位,再采用常用的一階相位差分法進行信號的瞬時測頻。因此,CF的測量可以采用一種數字瞬時測頻技術[1]。

圖2 一種寬帶信號檢測及參數測量的設計框圖

1.2 窄帶信號檢測及參數測量

為減少硬件設備量,雷達僅配置一個寬帶通道,并依靠幅度比較法實現測向,其測角精度約1°~2°。在寬帶通道處理得到外輻射源部分信息后,可以使用雷達自身的窄帶通道及利用單脈沖測角法對輻射源進行角度測量以提高精度;并對重點外輻射源做進一步信息的提取或精確測量。通過對窄帶通道數據的進一步處理,可以得到目標的信息包括輻射源頻率、脈沖重復周期、脈寬、信號幅度、方位角、俯仰角、信噪比、脈沖到達時間和個數、到達時間數組等。因此,窄帶通道處理主要包含以下三點:

(1)窄帶和/方位差/俯仰差/等通道信號的下變頻及采樣;

(2)窄帶通道中信號門限檢測,主要包括時域檢測(通常為檢測通道時域信號的脈沖起始時間(相對于距離零點),脈寬計算等);

(3)和差通道脈沖中心IQ數據抽取,主要用于后續單脈沖[2]測角誤差及俯仰角誤差的提取。

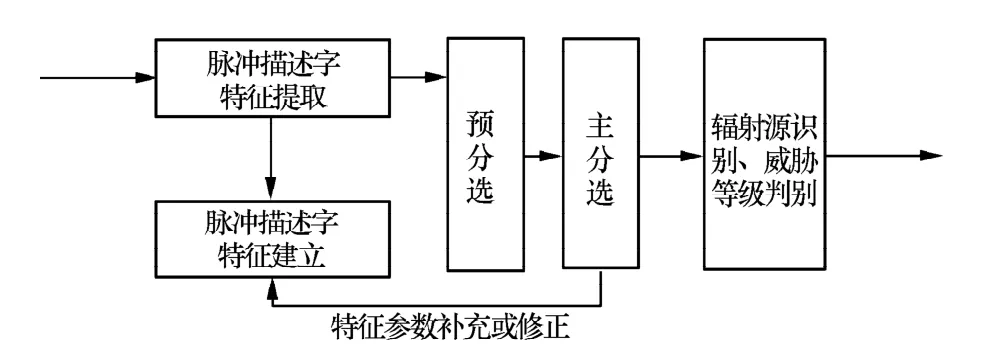

1.3 信號分選處理

信號分選是無源偵收系統中核心組成部分之一。目的是從偵察接收機接收到的隨機交錯的密集脈沖流中,根據解析出來的相關參數信息,分選出不同輻射源的信號特征信息,并通過與相關輻射源特征庫的對比分析,綜合確定所分選出輻射源對應的用途,所在平臺類型,從而進一步給出目標所配置的武器系統及威脅等級,為警戒干擾系統提供識別高威脅信號的特征參數或為相關戰略情報分析提供有利的依據。

信號分選主要是利用到達角(AOA)、載頻(CF)、脈寬(PW)、到達時間(TOA)、脈沖幅度(PA)等參數構成的脈沖描述字(PDW)進行輻射源信號的分選處理。脈沖到達時間(TOA)是對方輻射信號脈沖到達偵收系統的時間,不能反映對方信號的特征,實際分選過程中采用相鄰脈沖到達的時間差(DTOA)參數進行。一般偵收到的脈沖流密度非常大,可先利用AOA、CF、PW 等特征參數聚類進行預分選;再對DTOA參數采用自相關的主分選方法開展進一步的分選處理;最后,通過綜合判斷及對比等處理分析,給出不同輻射源目標的識別及威脅等級判別情況。針對目前各種平臺上相關常用傳感器類型,應用較多的信號主分選算法主要有序列差值直方圖法、改進的累積差值直方圖法、傳統的TOA差值直方圖[3-4]。圖3給出了一種信號分選處理過程的設計框圖,主分選算法擬采用一種改進的基于DTOA統計的信號分選算法[5]。

圖3 一種信號分選處理的設計框圖

1.4 目標信息融合處理

目標信息融合處理是進行窄帶處理結果和信號分選結果的數據融合處理,主要包括以下四點:

(1)對窄帶處理上報的各通道窄帶數據與信號分選輸出的寬帶數據進行數據融合,包括完成脈沖匹配,頻率融合。

(2)通道校正,根據融合后無源目標的頻率對和差通道窄帶數據進行通道校正處理。

(3)方位差、俯仰差提取。

(4)數據輸出,根據單脈沖測角結果完善信號分選得到的脈沖描述字輸出。

1.5 點跡航跡處理

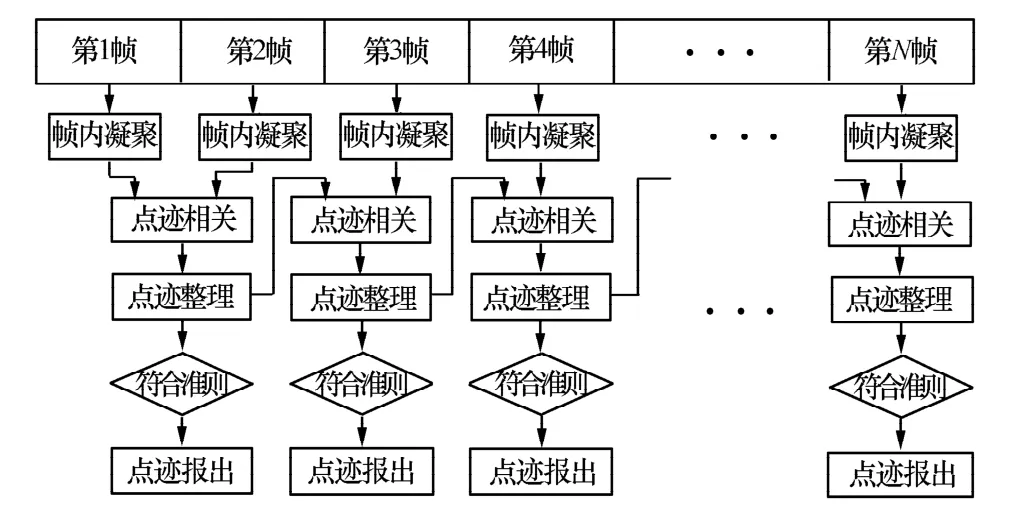

點跡航跡處理過程主要包括幀內的合批處理和幀間的聚類相關處理,目的是為了合并探測空域中的相同目標,提高目標的角度和頻率測量準確度,避免出現目標分裂并形成目標航跡。點跡航跡處理流程如圖4所示。

圖4 點跡航跡處理設計框圖

2 硬件實現設計

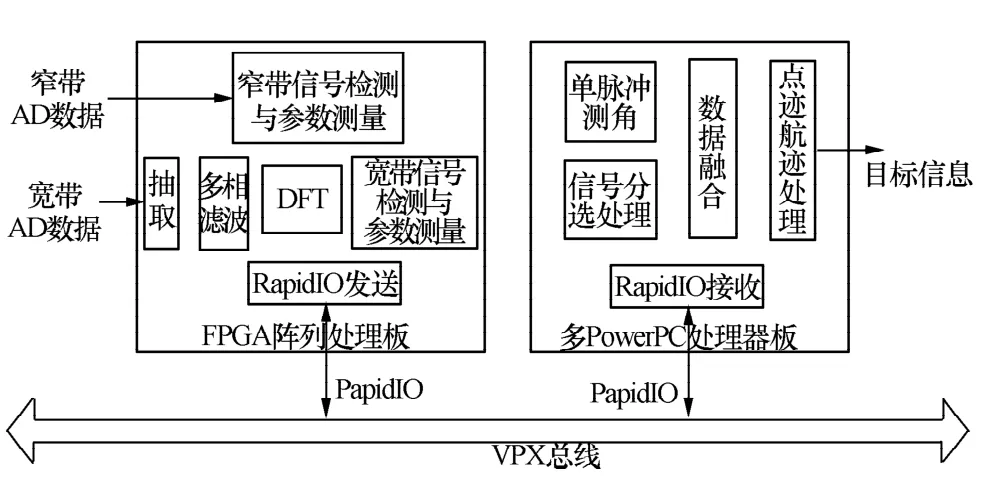

本文無源探測方式數字處理的硬件實現,采用目前流行且先進的基于VPX總線的大規模FPGA陣列通用處理板,多PowerPC處理器通用處理板,支持RapidIO[6]高速串口通信技術的VPX總線背板等硬件組成的處理架構,其硬件實現設計框圖如圖5所示。

圖5 基于FPGA+多PowerPC處理器架構的硬件實現

無源探測的數字處理主要包括寬帶采樣信號的抽取、多相濾波、DFT、信號檢測、參數測量及信號分選;窄帶信號的檢測、參數測量;數據融合、點跡航跡處理等。根據現場可編程門陣列(FPGA)芯片擅長高度并行化的數據流處理、PowerPC擅長復雜邏輯性的串行或事務處理等特點,簡單劃分了在FPGA及PowerPC中需要實現的部分。

2.1 基于FPGA的硬件實現

FPGA是一種設計靈活方便、可以通過重復調整內部邏輯設計用以實現不同處理算法或邏輯控制電路的現場可編程器件;根據FPGA芯片并行結構及開發使用的特點,通常在處理算法實現方面被用于算法結構比較簡單、速度要求較高的算法實時實現。這是由其自身的結構及所具備大量的乘法器、存儲器、硬運算單元及邏輯單元等資源所決定的。與數字信號處理(DSP)處理器相比,FPGA芯片最大的優勢在于其并行處理的實現架構,這使得其特別適合用于實現像濾波這樣重復性程度較高的實時數字信號處理任務。在高度并行、基于數據流的數字信號處理任務的實時實現方面,基于FPGA的實現其性能遠超過基于DSP處理器的軟件串行實現架構。因此,FPGA已成為一種重要的數字信號處理工具。在此采用FPGA進行抽取模塊、多相濾波、DFT、寬帶信號檢測與參數測量、窄帶信號檢測及參數測量等模塊的設計實現。

1)抽取模塊

高速抽取模塊的本質是串并轉換,在此采用先進先出(FIFO)存儲器來實現串并轉換;該方案可以利用FPGA內部的相關塊RAM資源實現,可以巧妙地解決異步時鐘域和多路問題,且節省邏輯資源,時序穩定。

2)多相濾波組模塊

多相濾波器模塊是圖5中抽取D模塊之后的處理模塊,是經過等效變換(抽取濾波先濾波、再抽取的處理過程等效為先抽取再濾波的過程)從抽取濾波轉換而來,大大降低了計算量。為FPGA實時處理的實現提供了高效的結構,對時序要求大大降低。在FPGA硬件中可以使用有限沖激響應(FIR)濾波器知識產權(IP)核實現各子濾波器。

3)DFT運算模塊

快速傅里葉變換(FFT)算法是計算離散傅里葉變換(DFT)的一種高效算法,是根據離散傅里葉變換的奇、偶、虛、實等特性,對DFT算法進行改進獲得的。FFT算法常用的實現架構是基于多相濾波組模塊算法的實現:將N點的數據序列通過逐次分解為(N-1)/2點,最終分解為基于兩點架構的DFT進行計算。FFT算法可以去掉DFT算法中大量的重復運算部分。針對FFT算法在工程實踐中的應用,為了便于FFT算法在FPGA中的實現,各大FPGA生產商(Xilinx公司、Altera公司等)都推出了具有相關功能的IP(知識產權)模塊庫。例如由Xilinx公司研發的針對其FPGA的FFT實現模塊(FFT V5.0 IP核),可以為用戶提供FFT算法的多種可選的相關計算參數、結構、數據輸入輸出流的順序方式,便于根據用戶的需求快速容易地實現FFT算法,本文DFT運算模塊的實現可以采用已有的FFT IP核模塊進行硬件實現。

4)窄帶、寬帶信號檢測模塊與參數測量

較為常用的信號檢測算法有時域能量檢測法、時域自相關法及頻域譜分析法。其中時域能量檢測法運算量小,便于硬件實現,且可以滿足系統設計的一般精度要求。本文使用FPGA實現寬、窄帶信號檢測時均采用此方法,主要過程為在時域上對其中相關信道輸出的連續N點數據進行能量累加,然后與預先設定的門限進行比較判定。如果累加值大于門限則認為該信道中存在信號,并進一步測量對應脈沖信號的信號類型,測量CF、PW、PA、TOA等參數。在FPGA硬件實現中可采取時域滑窗處理的方法,并行檢測處理所有信道中接收到的信號。

2.2 基于多PowerPC的軟件實現

采用精簡指令集(RISC)架構的PowerPC處理器,因其架構具有可伸縮性好、方便靈活,具有較低的能量損耗以及較低的散熱量,在嵌入式領域具有非常好的表現。VxWorks是一種基于優先級搶占式機制的多任務實時操作系統,同時支持同優先級任務的分時間片調度;它能通過任務間的同步機制(進程間通信機制、中斷處理、定時器和內存管理機制),較好地管理各種獨立任務的執行,使得每個任務能及時響應并及時處理外部事件。因此,良好的可靠性和卓越的實時性使其被廣泛地應用在通信、軍事、航空、航天等高精尖技術及實時性要求極高的領域中,可以為完成整個系統的實時信號處理提供很好的系統軟件支持。

針對各種嵌入式系統中的實時信號、數據處理方面,基于PowerPC和VxWorks的嵌入式板卡以其高性能、低功耗、高穩定性、高實時性的特點,已成為了近年來嵌入式系統硬件及軟件實現架構研究的熱點之一,且越來越多的相應板卡出現在各種嵌入式產品中,其中包括軍工產品、航空航天設備等。其中,應用較多的PowerPC處理器主要是Freescale公司的7448、8160D、8641D等[7]系列處理器;其特點是該處理器采用了內置AltiVec模塊(提供了支持SIMD結構的矢量浮點運算硬件加速單元)的e600內核,具有很高的運算性能。

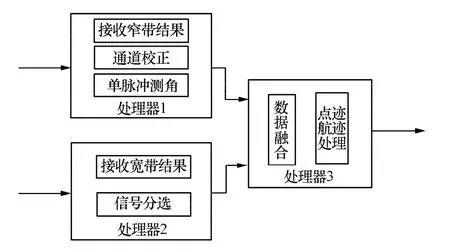

本文采用一種基于4塊8640D處理器的VPX通用處理板卡(貨架產品),在VxWorks實時操作系統的基礎上,利用8640D多處理器協同完成邏輯性較復雜的信號分選處理、單脈沖測角、數據融合、點跡航跡等模塊的實時處理任務,實現示意框圖如圖6所示。該板卡集成了4片1 GHz雙核8640D處理器,總運算能力可達64GFLOPS,支持8GB DDR2存儲器,FFT運算的實測性能約為信號處理專用處理芯片ADS-TS201的1.5倍。

圖6 基于多PowerPC處理器的實現部分

3 系統驗證

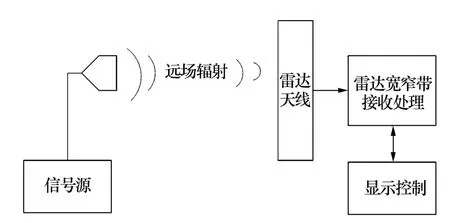

使用本文設計的機載無源探測系統,在遠場條件下,可按照圖7所示測試驗證以下內容:

(1)系統可以分選脈沖波、連續波等信號形式,并輸出輻射源的頻率、幅度、到達時間等特征參數;

(2)系統可以使用寬帶接收機發現信號源喇叭的角度位置;

(3)通過引導雷達窄帶接收機,可以實現對遠場信號源喇叭的角度定位及跟蹤處理,通過分選可以得到輻射源的重復周期、脈沖寬度等參數;

(4)系統可以在較高的靈敏度下工作,實現對小信號輻射源的探測。

圖7 系統遠場驗證

4 結束語

機載平臺上的主要傳感器雷達和電子支援措施(ESM)各自具有各的優勢,在新的戰爭形勢下,機載雷達面臨著“四抗”的威脅,雷達的探測性能了很大的制約,光靠雷達的常規功能已很難滿足現代空戰的需要。本文通過在機載雷達常規具備的和差窄帶接收及處理通道的基礎上,增加一個能夠處理對應雷達工作頻段的寬帶接收及處理通道,結合寬窄通道各自接收及處理的特點,給出了機載雷達一種無源探測方式的設計;希望能為擴展雷達相關工作方式的設計與實現方面的研究供一定參考作用。

[1] 王亞森,鮑慶龍,曹務紳,等.數字信道化IFM接收技術研究[J]. 雷達科學與技術,2012,10(5):539-543.Wang Yasen,Bao Qinglong,Cao Wushen,et al.Rearch on a digital channelized IFM receiver[J].Radar Science and Technology,2012,10(5):539-543.

[2] 丁鷺飛,耿富錄,陳建春.雷達原理[M].4版.北京:電子工業出版社,2009.Ding Lufei,Geng Fulu,Chen Jianchun.The principles of radar[M].4th ed.Beijing:Publishing House of Electronics Industry,2009.

[3] 王海濱,馬 琦.一種基于PRI變換的雷達信號分選方法[J].現代電子技術,2013,36(1):28-31.Wang Haibin,Ma Qi.Method of deintetleaving radar signal based on PRI transform algorithm[J].Modern Electronics Techique,2013,36(1):28-31.

[4] 李合生,韓 宇,蔡英武,等.雷達信號分選關鍵技術研究綜述[J].系統工程與電子技術,2005,27(12):2035-2040.Li Hesheng,Han Yu,Cai Yingwu,et al.Overview of the crucial technology research for radar signal sorting[J].Systems Engineering and Electronics,2005,27(12):2035-2040.

[5] 黃桂根,傅有光,武月婷.一種改進的基于DTOA統計的信號分選算法[J].數據采集與處理,2011,26(4):430-435.Huang Guigen,Fu Youguang,Wu Yueting.Improved radar signal deinterleaving algorithm based on DTOA histogram[J].Journal of Data Acquisition & Processing,2011,26(4):430-435.

[6] 翟彥彬,蔣志焱,張保寧.大規模RapidIO協議交換的FPGA 實現[J]. 現代雷達,2011,33(12):33-35.Zhai Yanbin,Jiang Zhiyan,Zhang Baoning.An implementation of large scale rapidIO switch on FPGA[J].Modern Radar,2011,33(12):33-35.

[7] 史鴻聲.雷達信息處理系統現狀及發展趨勢[J].雷達與對抗,2011,31(3):14-17.Shi Hongsheng.The status quo and development trend of radar information processing system[J].Radar& ECM,2011,31(3):14-17.