同步時序電路設計方法研究

余輝晴

寧波工程學院,浙江寧波 315016

同步時序電路設計是根據給定的任務設計出符合要求的邏輯電路。同步時序電路設計的一般步驟如下。

1)根據設計要求畫出狀態轉換圖。

2)根據狀態轉換圖寫出狀態方程和驅動方程。

3)根據驅動方程畫出邏輯電路圖。

1 通過狀態轉換表對同步時序電路進行設計

以同步四進制加法計數器為例。

1.1 根據設計要求畫出狀態轉換圖

(00)→(01)→(10)→(11)→(00)

1.2 根據狀態轉換圖寫出狀態轉換表

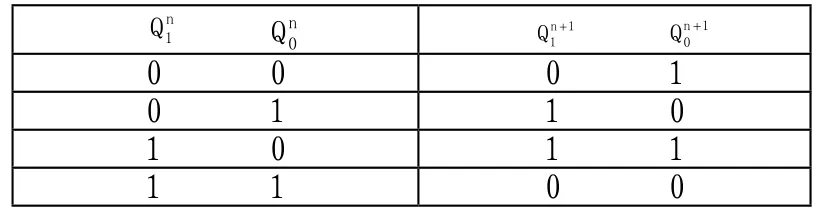

表1 同步四進制加法計數器狀態轉換表

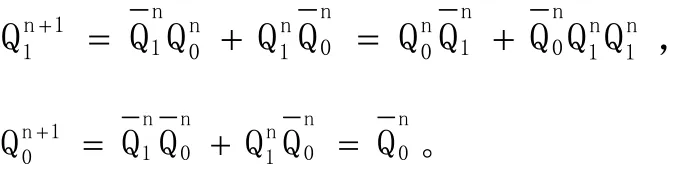

1.3 根據狀態轉換表寫出狀態方程

將表1同步四進制加法計數器狀態轉換表分解為1號觸發器和0號觸發器狀態轉換真值表,由狀態轉換真值表寫出觸發器的狀態方程,并將狀態方程改寫成標準形式。

1.4 根據狀態方程寫出驅動方程

將各觸發器標準狀態方程與JK觸發器狀態方程對比,可得各觸發器驅動方程。

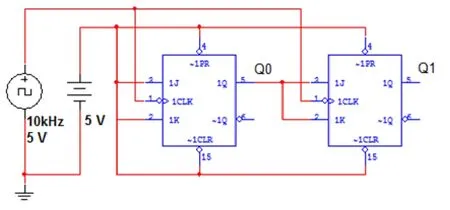

1.5 根據驅動方程畫出邏輯電路圖

根據驅動方程,采用JK觸發器設計的同步四進制加法計數器電路圖如圖1所示。

2 通過狀態轉換卡諾圖對同步時序電路進行設計

以同步六進制加法計數器為例。

2.1 根據設計要求畫出狀態轉換圖

(000)→(001)→(010)→(011)→(100)→(101)→(000)

圖1 同步四進制加法計數器電路圖

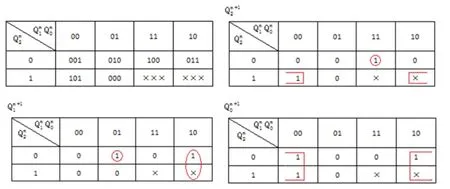

2.2 根據狀態轉換圖寫出狀態轉換卡諾圖

由狀態轉換圖可畫出總的狀態轉換卡諾圖,然后將其分解為2號觸發器、1號觸發器和0號觸發器狀態轉換卡諾圖。為了直接得到觸發器狀態方程標準形式,對各觸發器狀態轉換卡諾圖按0區和1區進行卡諾圖畫簡。

圖2 同步六進制加法計數器狀態轉換卡諾圖

2.3 根據狀態轉換卡諾圖寫出狀態方程

由各觸發器狀態轉換卡諾圖寫出其狀態方程,并將狀態方程改寫成標準形式。

2.4 根據狀態方程寫出驅動方程

將各觸發器標準狀態方程與JK觸發器狀態方程對比,可得各觸發器驅動方程。

2.5 根據驅動方程畫出邏輯電路圖

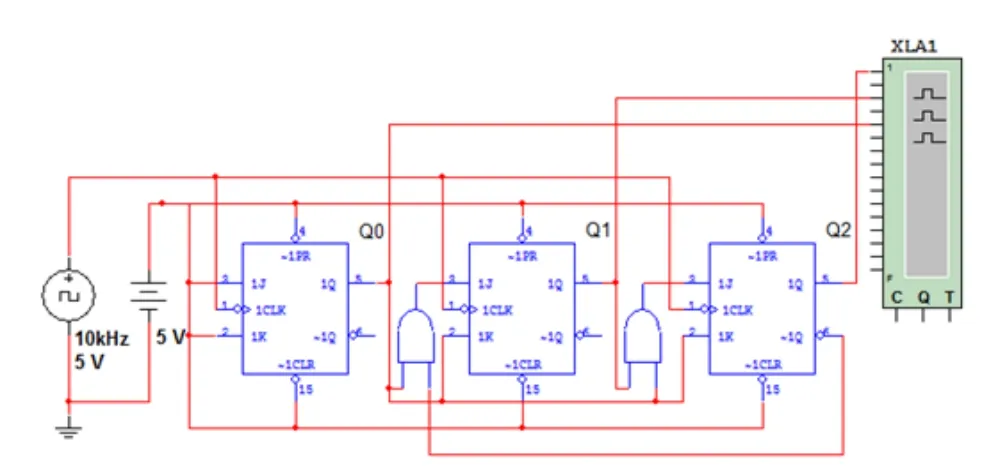

根據驅動方程,采用JK觸發器設計的同步六進制加法計數器電路圖如圖3所示。

圖3 同步六進制加法計數器電路圖

3 通過Multisim對同步時序電路進行仿真

對所設計的同步六進制加法計數器進行Multisim仿真。

3.1 創建電路

以JK觸發器作記憶元件,三個JK觸發器從左至右依次為Q1、Q2、Q3,使能端接5V電源,選方波發生器做時鐘脈沖信號,方波信號頻率設置為10kHz,創建如圖3所示同步六進制加法計數器電路。

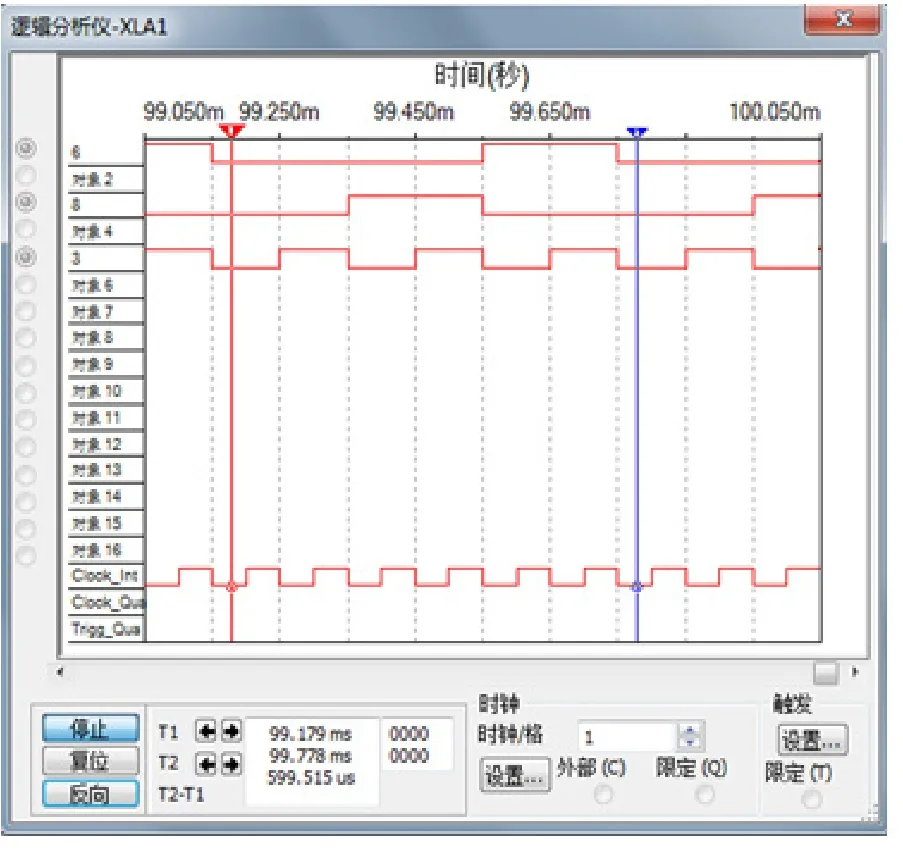

3.2 觀測計數器輸出波形

將三個JK觸發器的輸出Q接在邏輯分析儀上,以測試各觸發器的輸出。電路的輸出波形如圖4所示。由輸出波形可以看出Q3Q2Q1的狀態按000、001、010、101、110、101循環,構成的是六進制同步計數器。

通過上述分析可以看出,通過狀態轉換表對同步時序電路進行設計比較清晰,通過狀態轉換卡諾圖對同步時序電路進行設計比較方便,通過Multisim對同步時序電路進行仿真比較直觀。

圖4 同步六進制加法計數器電路仿真輸出波形

[1]賈立新.數字電路[M].北京:電子工業出版社,2011.

[2]楊志忠.數字電子技術基礎[M].北京:高等教育出版社,2009.

[3]蔣卓勤.Multisim及其在電子設計中的應用[M].西安:西安電子科技大學出版社,2011.