申威處理器硬件數據預取技術的實現*

賈 迅,胡向東,尹 飛

(上海高性能集成電路設計中心,上海201204)

1 引言

預取技術根據實現方式可分為軟件預取和硬件預取。軟件預取由程序員或編譯器在程序中插入預取指令實現預取;硬件預取則需要在處理器的微結構中增加預取引擎,引擎根據程序執行時的訪存行為,發出硬件預取請求實現預取功能。硬件預取對程序員透明,沒有兼容性問題,能利用程序的動態訪問特征。目前,國產處理器如申威、龍芯[3]等僅支持軟件預取。

硬件預取技術的實現面臨兩個方面的挑戰:一是實現復雜度與硬件開銷的降低;二是與處理器具體結構特點的結合。申威處理器硬件數據預取技術的突破不僅可以直接提升申威處理器的性能,拓寬其在高性能計算、安全平臺以及服務器領域的應用;同時也可以為硬件預取技術在其它國產處理器中的應用提供參考。

2 硬件預取機制

程序訪存行為的特征是硬件預取的基礎,預取引擎利用訪存特征生成預取請求的方法稱為預取機制。學術界在研究過程中,針對規則的存儲訪問提出了多種硬件預取機制,包括順序預取、流預取[4]和跨步預取[5],同時也研究了針對不規則存儲訪問的預取機制,例如關聯預取。

(1)順序預取是最簡單的預取機制,預取引擎總是預取當前訪問Cache行的下一個Cache行,硬件實現開銷小,但對訪存帶寬的需求較高。

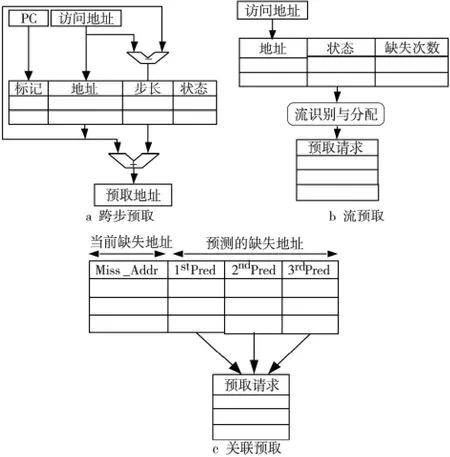

(2)跨步預取利用同一條訪存指令在不同循環迭代過程中,訪問地址中存在的固定步長進行預取,因而適用于矩陣或數組結構較為密集的高性能計算應用。硬件實現需要使用訪問預測表。如圖1a所示,記錄訪問的地址、步長以及訪存指令的PC值。預取引擎檢測到固定步長的訪問時,發出預取請求,預取的地址為當前訪問地址加步長。

(3)流預取對流訪問特征進行預取,流訪問特征是指一段時間內,程序訪問的Cache行地址呈現遞增或遞減的規律。這種訪問規律在科學計算和工程應用中廣泛存在。硬件實現時,需要使用流識別緩沖(如圖1b所示)記錄一段時間內訪存的Cache行地址。預取引擎識別到流訪問,則進行預取。

(4)關聯預取利用訪存地址之間存在的關聯性進行預取。Markov預取[6]機制屬于典型的關聯預取,它利用Markov模型對訪存缺失地址建模。硬件上使用關聯預測表(如圖1c所示)記錄與缺失地址相關聯的訪存地址。當訪問缺失時,預取與缺失地址相關聯的所有地址。指針預取[7]也是關聯預取的一種,它利用load指令和將這條訪存指令的結果作為訪問地址的load指令之間存在的“生產-消費”關系進行預取,硬件上同樣采用關聯信息表保存這種依賴關系。

Figure 1 Structures of various prefetching mechanisms圖1 不同預取機制的硬件結構

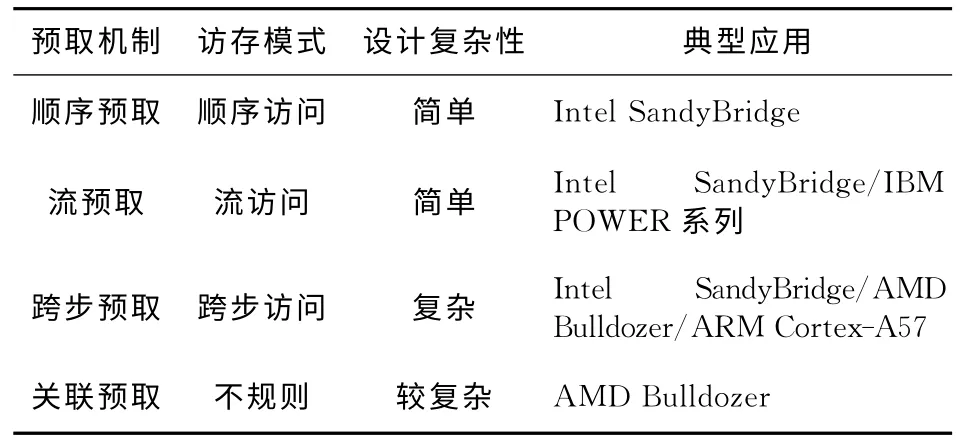

表1從“訪存模式”“設計復雜性”“典型應用”三個方面對上述介紹的不同硬件預取機制進行了總結。可以看出,為了降低硬件實現的復雜度和開銷,商用處理器大多采用了較為簡單的流預取和跨步預取。

首先將邊u11u12,um(2n-1)um(2n)染為k+2色,把邊u0(2n+2)u1(2n+1)染為k+1色,邊u(m-1)2um1染為色,其次把邊us(2n+1)us(2n+2)(s=1,3,…,m-2)染為色,把邊us1us2(s=3,5,…,m-2)染為色。

Table 1 Summary of various prefetching mechanisms表1 不同預取機制的總結

3 硬件預取的實現方法

3.1 申威處理器的訪存通路

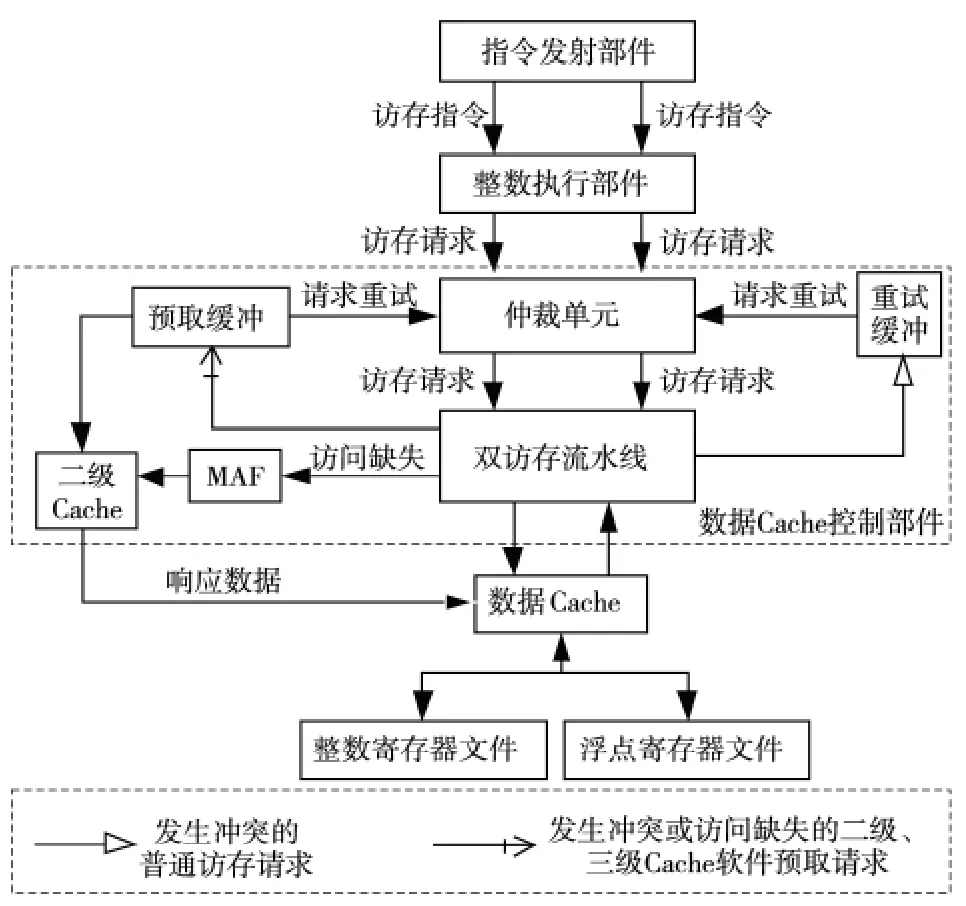

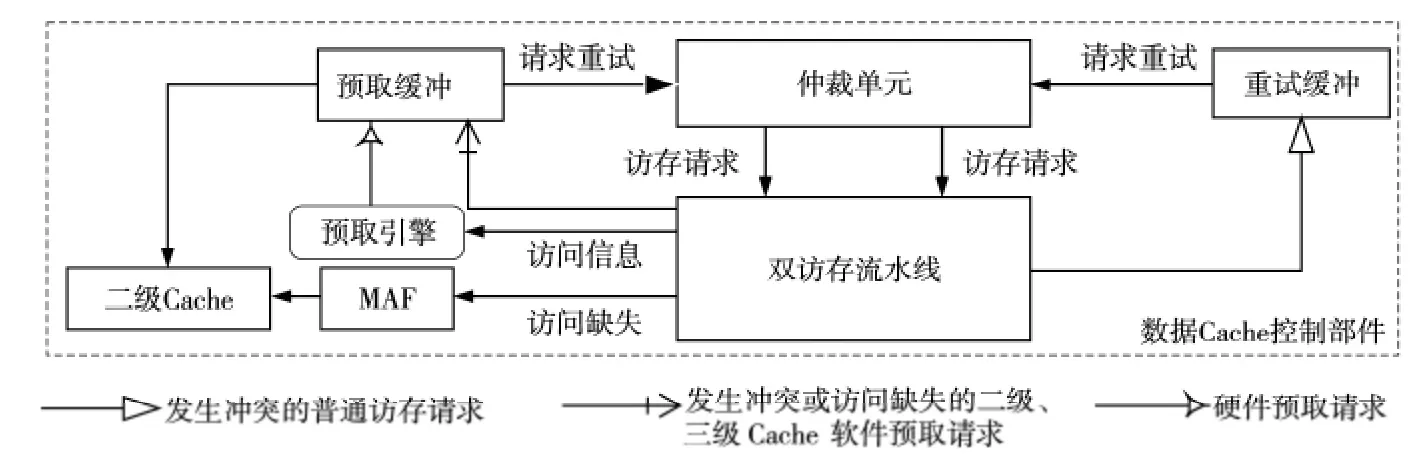

新一代申威處理器核心采用超標量架構,支持亂序發射、推測執行和雙訪存流水線技術。核心內部一級指令Cache和數據Cache分離,兩者共享二級Cache,核外配置有大容量三級Cache。由于硬件數據預取技術主要與存儲訪問相關,因而申威處理器的訪存數據通路(如圖2所示)是預取技術實現的研究重點。

訪存指令由指令發射部件發往整數執行部件執行后,首先要進入數據Cache控制部件中的仲裁單元。仲裁成功后的請求發往雙訪存流水線訪問數據Cache。若訪問命中,對于load類請求,數據從Cache裝入寄存器文件,供處理器計算使用;對于store類請求,數據從寄存器文件寫入Cache。若訪問缺失,則請求信息登記在缺失地址隊列MAF(Miss Address File)中,并發往二級Cache進行后續處理。訪存請求在執行過程中可能發生沖突,普通的訪存請求發生沖突時進入重試緩沖,軟件預取請求發生沖突則進入專門設置的預取緩沖。重試緩沖與預取緩沖中的請求會在流水線空閑時,以重試的方式仲裁上流水線執行。

Figure 2 Memory access pipeline of Shenwei microprocessor圖2 申威處理器的訪存流水線

3.2 硬件預取的實現框架

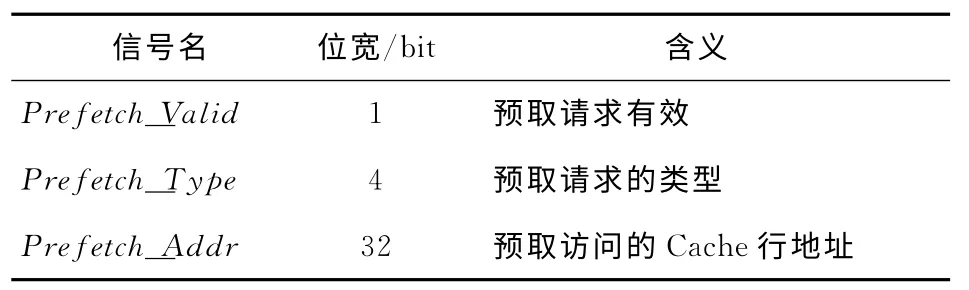

硬件預取的實現需要在數據Cache控制部件中增加預取引擎。預取引擎通過記錄雙訪存流水線上請求執行的信息,在對應預取機制的指導下生成硬件預取請求。為了降低硬件預取實現的邏輯復雜度與硬件開銷,本文將引擎生成的硬件預取請求也放入預取緩沖,從而數據Cache控制部件對硬件預取請求的處理可以復用軟件預取請求仲裁上流水線,請求訪問一級數據Cache,二級、三級Cache對訪問缺失的請求進行處理的整個數據通路,如圖3所示。

Figure 3 Implementation framework of hardware prefetching圖3 硬件預取的實現框架

為了復用流水線處理軟件預取的數據通路,硬件預取請求的格式與軟件預取請求必須完全兼容。數據Cache控制部件中,軟件預取請求的定義包括:請求的有效位、請求的類型以及請求訪問的Cache行地址,硬件預取請求的定義見表2。

Table 2 Definition of hardware prefetching requests表2 硬件預取請求的定義

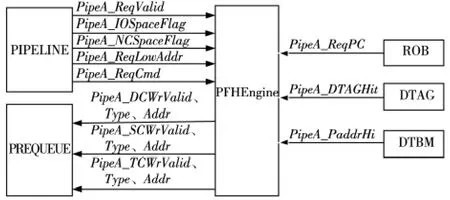

由于申威處理器采用雙訪存流水線,預取引擎在一個時鐘周期內需要同時處理兩條訪存指令的訪問信息。本文以流水線A為例介紹預取引擎(PFHEngine)與其它模塊,如請求處理流水線(PIPELINE)、預取緩沖(PREQUEUE)、指令重排序緩沖(ROB)、數據Cache標記管理單元(DTAG)和頁表管理單元(DTBM)的接口信號,如圖4 所示。

Figure 4 Interface between a prefetching engine and other modules圖4 預取引擎與其它模塊的接口

預取引擎記錄的訪問信息包括:訪存指令的PC值、請求的類型、地址、請求訪問Cache是否命中等。具體實現時,引擎內部可以靈活采用不同的硬件預取機制。下文以流預取例,驗證預取引擎實現框架的正確性。

3.3 流預取的實現

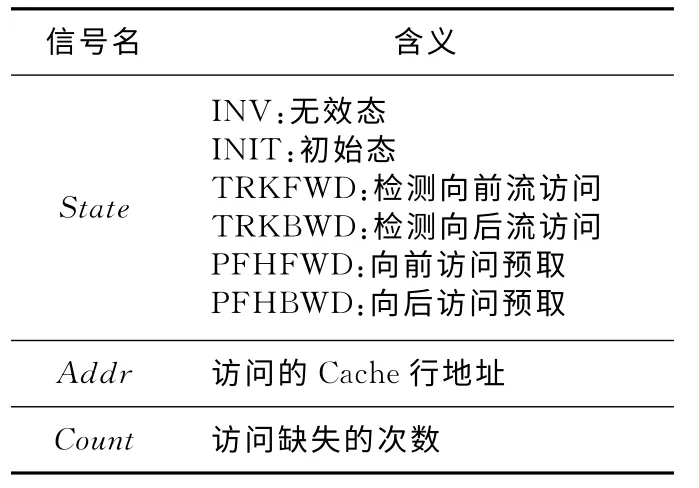

流預取機制的實現需要在硬件上設置流識別緩沖以檢測一段時間內的流訪問。流識別緩沖條目記錄的信息包括訪問的Cache行地址、條目的狀態以及訪問缺失的次數。具體的信號及含義如表3所示。

Table 3 Information recorded in the stream detection buffer表3 流識別緩沖記錄的信息

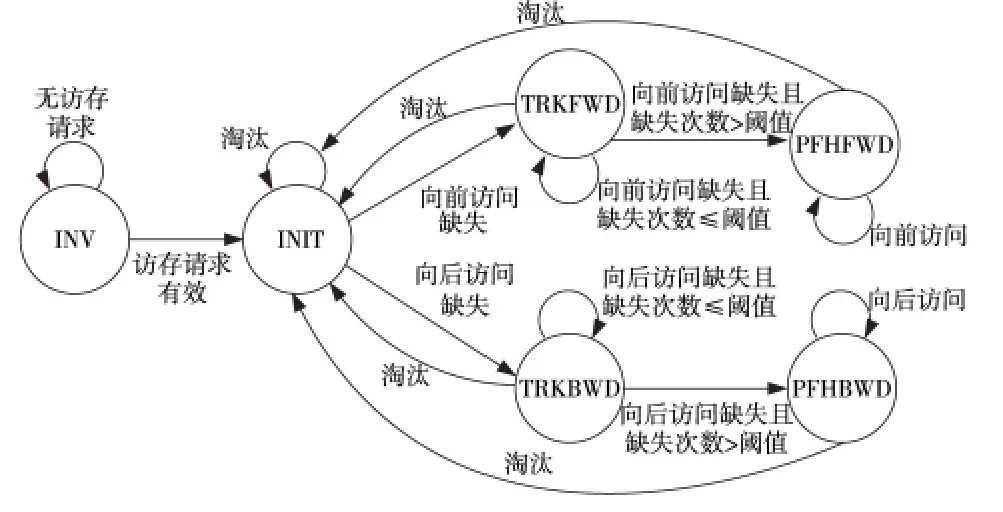

流識別緩沖中所有條目初始化時均置為無效態INV,后續的狀態轉換見圖5。其中,“淘汰”是指一段時間內,處理器未訪問條目對應的流。“向前/向后訪問缺失”是指訪問缺失的地址等于條目記錄的Cache行地址加1 或減1。當訪問缺失的次數大于流識別閾值時,條目進入預取狀態。此時,處理器訪問流中一個新的Cache行,會觸發對下一個Cache行的預取。

4 性能評測

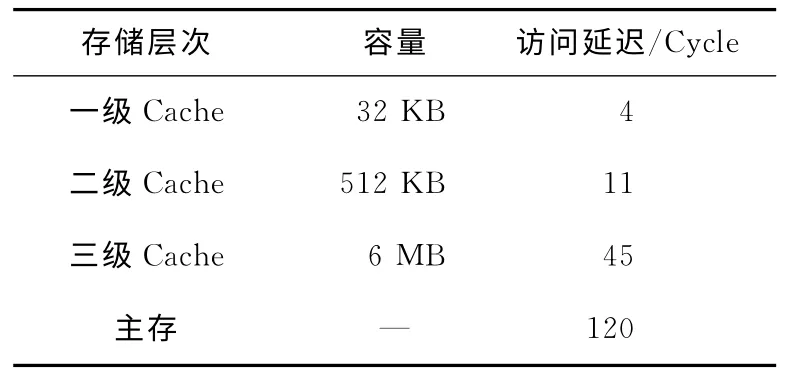

本文的實驗環境由處理器模型、基準測試程序和硬件仿真加速器三部分構成。為了真實測試硬件數據預取技術對申威處理器訪存性能的提升,本文采用申威處理器某芯片完整的邏輯設計作為處理器模型,芯片中各存儲層次的容量和訪問延遲如表4所示。本文采用Verilog硬件描述語言實現了硬件預取功能,其中流識別緩沖條目數為8,流識別閾值為2。

Figure 5 State transitions in the stream detection buffer圖5 流識別緩沖條目的狀態轉換

Table 4 Memory hierarchy parameters表4 各存儲層次的參數

本文采用SPEC CPU2000基準測試程序集,其廣泛應用于桌面系統和單處理器服務器的性能測試。SPEC CPU2000 由12 道整數測試程序和14道浮點測試程序組成,這些程序都從真實的用戶程序演變而來,因而可以真實反映不同程序的訪存特征。

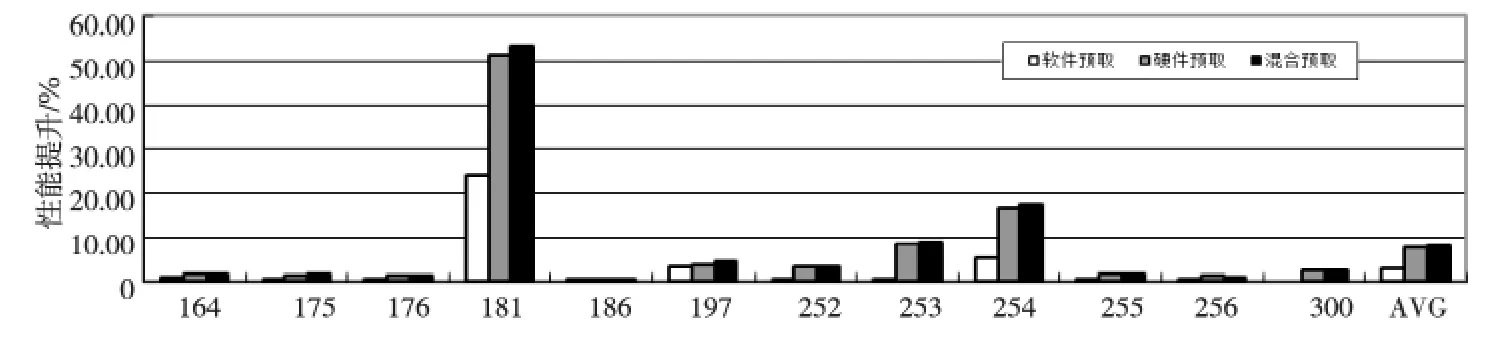

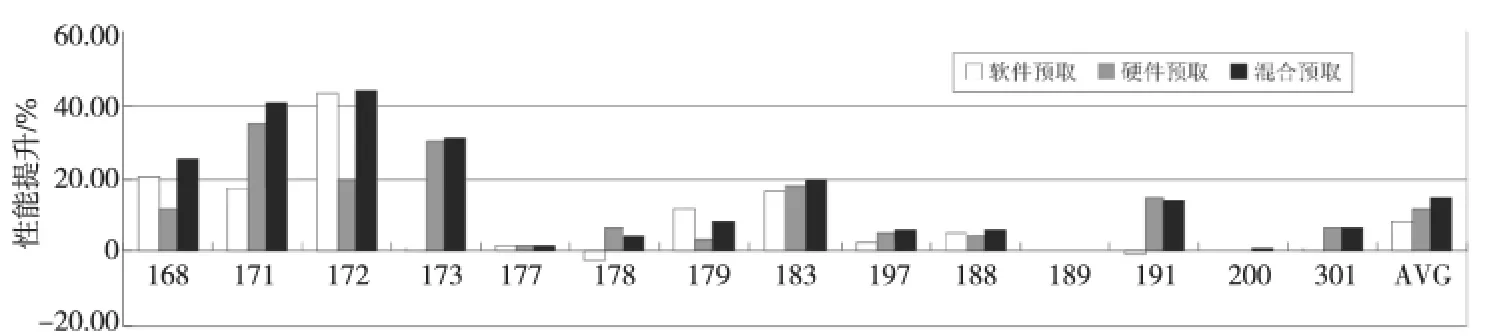

為了進一步提高實驗結果的準確性,本文以Cadence公司的Palladium XP GXL系列[8]硬件仿真加速器作為實驗平臺,其提供了微處理器模型的仿真環境,并可以準確反映處理器仿真運行過程中的相關性能參數。本文以SPEC CPU2000測試程序在硬件仿真加速器上運行完成所需周期數作為預取機制性能評價的標準。本文測試了單獨使用軟件預取、硬件預取和軟硬件混合預取的性能,整數、浮點測試程序的結果分別如圖6和圖7所示。

Figure 6 Integer performance improved by stream prefetching in Shenwei microprocessor圖6 流預取對申威處理器整數性能的提升

Figure 7 Float performance improved by stream prefetching in Shenwei microprocessor圖7 流預取對申威處理器浮點性能的提升

可以看出,對于整數程序,單獨使用軟件預取、硬件預取對申威處理器的性能提升效果分別為2.99%和7.79%,混合預取的性能提升為8.16%。對于浮點程序,單獨使用軟件預取、硬件預取對性能的提升效果分別為8.52%和11.20%,混合預取的性能提升為14.91%。硬件預取技術的使用可以將目前申威處理器的整數性能平均提升5.17%,最高提升28.88%(181.mcf);浮點性能平均提升6.39%,最高提升30.11%(173.applu)。另外,對于課題178.galgel、191.fma3d,硬件預取的使用可以有效解決編譯器插入軟件預取因預取時機不合適而導致性能下降的問題。

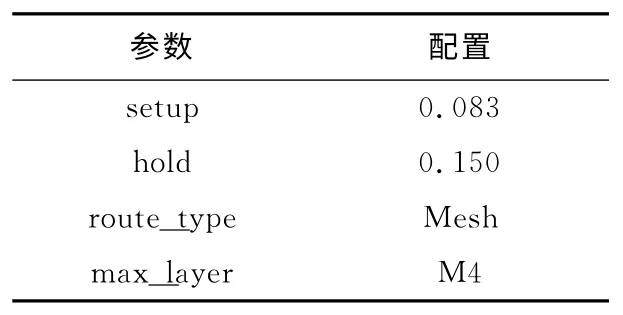

對于硬件開銷和時序的評估,本文采用Synopsys公司的Design Compiler工具在1.6GHz、40nm 工藝下對數據Cache控制部件進行邏輯綜合,以綜合的面積作為評價預取機制硬件開銷的標準,同時對時序結果進行檢查,綜合過程中的參數配置見表5。

Table 5 Parameters used for logic synthesis表5 邏輯綜合的參數設置

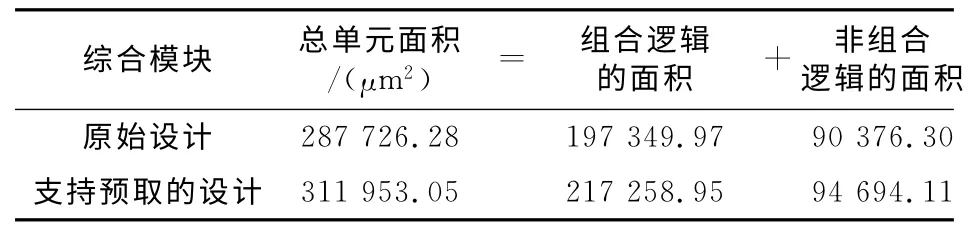

硬件開銷的評估結果如表6所示,實現流預取所需的硬件開銷僅為申威處理器核心面積的0.14%。另外,根據綜合的時序報告,本文硬件預取的設計完全滿足1.6GHz下的時序要求。

Table 6 Implementation cost of hardware prefetching表6 數據預取技術實現所需的硬件開銷

5 結束語

硬件數據預取技術是緩解“存儲墻”問題的有效手段之一,在商用處理器中廣泛應用。本文結合申威處理器“雙訪存流水線”“支持軟件預取”“集成多級Cache”的結構特點,以降低邏輯設計的復雜度和硬件開銷為目標,提出了預取引擎實現的整體框架,并通過流預取機制的實現驗證了其可行性。本文對硬件數據預取技術在國產處理器中的實現方式和應用價值進行了有益探索。

[1] Intel Corporation.Intel 64and IA-32architecture optimization reference manual[EB/OL].[2014-12-05].http://www.intel.com/content//www /us/en/documents/manuals/64-ia-32-architectures-optimization-manual.pdf.

[2] Tendler J M,Dodson J S,Fields J S,et al.POWER4system microarchitecture[J].IBM Journal of Research and Development,2002,46(1):5-25.

[3] LOONGSON Technology Corporation Limited.User mannual for Loongson 3B1500microprocessor[EB/OL].[2014-12-05].https://www.loongsin.cn.(in Chinese)

[4] Jouppi N P.Improving direct-mapped Cache performance by the addition of small fully-associative cache and prefetching buffers[C]∥Proc of the 17th Annual International Symposium on Computer Architecture,1990:364-373.

[5] Chen T F,Baer J L.Effective hardware-based data prefetching for high-performance processors[J].IEEE Transactions on Computers,1995,44(5):609-623.

[6] Joseph D,Grunwald D.Prefetching using Markov predictors[J].IEEE Transactions on Computer,1999,48(2):121-133.

[7] Roth A,Moshovos A,Sohi G S.Dependence based prefetching for linked data structures[C]∥Proc of the 8th International Conference on Architectural Support for Programming Language and Operating Systems,1998:115-126.

[8] Cadence Design Systems,Inc.Cadence Palladium XP verification computing platform[EB/OL].[2014-12-05].www.cadence.com/rl/resource/technical_briefs/palladium_xp_tb.pdf.

附中文參考文獻:

[3] 龍芯中科.龍芯3B1500處理器用戶手冊[EB/OL].[2014-12-05].https://www.loongson.cn.