TFT-LCD制程中Sand Mura的失效模式分析及改善研究

史高飛,沈奇雨,許徐飛,宋 潔,趙 娜,韓基挏,李乘揆

(合肥京東方光電科技有限公司,安徽 合肥 230011)

1 引 言

當今信息社會高速發展,液晶顯示器(TFTLCD)已經深入人們的日常生活,隨著人們對液晶顯示技術的更多了解,消費者對液晶顯示面板畫面品質的要求也在不斷提高。這些更高畫質要求促使液晶面板廠商進一步提升技術并開發高技術規格的產品,因而致使TFT-LCD面板開發生產過程中不斷產生新的不良現象[1-4]。

Mura是一種非常影響液晶顯示面板畫面品質的不良現象,主要表現為有效顯示區域內亮度或者顏色顯示不均勻。在實際TFT-LCD液晶面板設計生產中,有很多過去未曾發現或難以明確的新型Mura,其具體產生原因多種多樣,需要具體情況具體分析及改善[5-6]。

本文研究對象Sand Mura就是一種TFTLCD高分辨率產品開發過程中新出現的Mura問題。本文通過對此不良現象的測試和分析討論了其產生的原因;同時通過對不良現象發生機理的深入分析,設計一種通過變更像素電極厚度及刻蝕時間的方案來解決此問題,并通過實驗來驗證改善方案的可行性。

2 實驗及過程

2.1 Sand Mura不良現象確認

實驗測試面板為8in(1in=2.54cm)WUXGA+ORG ADS產品,Top pixel,面板尺寸為111.64mm×180.274mm。在顯示同一灰度或者單色畫面時,基板表面出現沙粒狀暗點,具體不良現象如圖1所示。

圖1 Sand Mura現象示意圖Fig.1 Schematic of Sand Mura phenomenon

2.2 Sand Mura不良原因分析

從不良現象上看,在Sand Mura不良現象發生區域的畫面比正常區域偏暗,懷疑與該不良像素區液晶分子偏轉及透光性相關。實驗首先通過顯微鏡觀察Sand Mura不良發生位置的像素分布來進行分析,顯微鏡下的像素分布圖如圖2所示。從圖中可以明顯觀察到不良區域的部分像素未能被正常點亮,導致了沙粒狀暗點不良現象的發生,也進一步證實了之前推測的正確性。

圖2 Sand Mura像素分布圖Fig.2 Schematic of Sand Mura micro

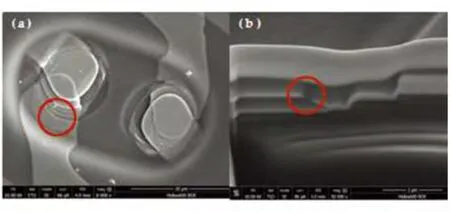

將實驗面板進行拆解(decap)處理并用乙醇去除基板表面殘留液晶,觀察彩膜(CF)基板對應暗點位置并未發現異常,可以判定不良根源存在于TFT基板。然后,將TFT基板進行切片處理,通過掃描電子顯微鏡(SEM)和聚焦離子束測試儀(FIB)觀察不良位置處的暗點,SEM和FIB結果如圖3所示。從圖中可以看出,不良處像素ITO電極發生了斷裂。分析表明,像素電極發生斷裂(Open)導致該處未能與公共電極形成偏轉電場,液晶分子不能正常偏轉,進而阻擋了光的傳播形成暗點。

圖3 像素區薄膜的表面和斷面圖.(a)表面圖;(b)斷面圖.Fig.3 Top and cross section picture of pixel films.(a)Top picture;(b)Cross section picture.

2.3 Sand Mura不良改善

通過上述的分析可知,像素ITO電極Open是導致Sand Mura不良發生的主要原因。然而導致像素電極發生Open的因素很多,可能是由于ITO薄膜沉積厚度的影響,使得有機膜(ORG)過孔和鈍化層(PVX)過孔段差位置處產生應力集中,當應力達到一定程度釋放時就會導致該處ITO薄膜發生斷裂;另外,像素電極在刻蝕過程中的過刻量(Over Etch)也是導致ITO 發生Open的重要因素。

針對上述導致ITO Open的原因,故需要從段差、ITO薄膜厚度以及過刻量3個方面進行改善,在目前量產工藝和設備條件下,通過不同的DOE實驗驗證找到最合適的各項參數。

首先,為了驗證ORG層段差對ITO Open產生的影響,實驗中設計了A和B兩組實驗條件,其中B組為ORG skip參考實驗。在A和B組中又設計了不同ITO厚度的驗證條件,具體條件(split)信息如表1所示,其中厚度(THK)T1<T2<T3;另外,沉積時加水可以使水分子占據晶格位置,使ITO結晶度降低而變得疏松,減小膜應力,容易刻蝕。

表1 ITO膜厚測試條件Tab.1 ITO Thickness test split item

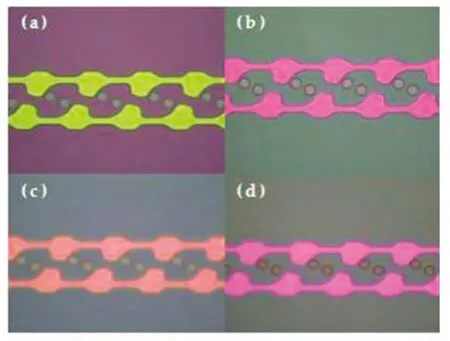

為了驗證沉積完成后ITO Open發生情況,實驗中使用宏觀微觀檢查設備Macro/Micro(M/M)對薄膜表面進行微觀檢查,檢查結果如圖4所示。

從M/M設備檢查結果圖4中可以看出,4種不同厚度的ITO薄膜沉積后膜層表面均較為平整,并未出現膜層斷裂現象,由此可以判定沉積條件并不是導致ITO Open的原因,并且A和B兩組沉積后對比均未見差異。

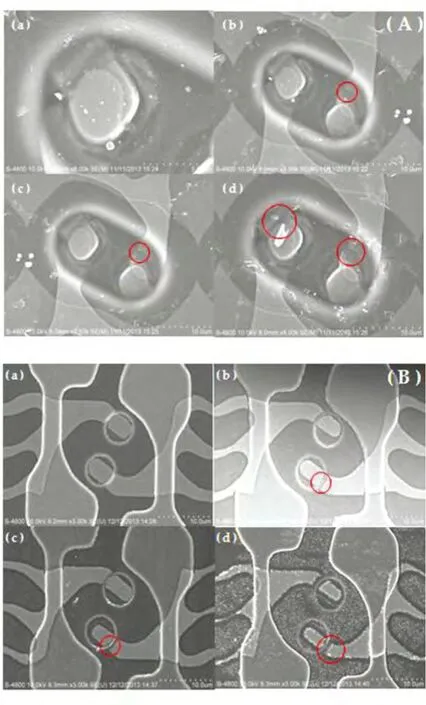

為了進一步驗證刻蝕工藝完成后不同厚度膜層對Open不良的影響,實驗中對刻蝕完成后A和B兩組中的各條件樣品分別進行了SEM分析,結果如圖5所示。

圖4 像素區 MM 圖.(a)split1MM 圖 ;(b)split2 MM 圖;(c)split3MM 圖 ;(d)split4MM 圖.Fig.4 The MM picture of pixel films.(a)MM picture of split1;(b)MM picture of split2;(c)MM pictureof split3;(d)MM picture of split4.

從SEM分析圖中可以看出,刻蝕完成后的ITO均出現了不同程度的Open現象,并且隨著膜厚的增加呈現出逐漸加重的趨勢。其中split1中除了邊緣位置發生Open,其他部分未見Open;當THK大于T1時,Open現象加重,而split2和split3并未出現明顯差異,由此可以得出,dep時加水并沒有對刻蝕產生較大的影響,而膜厚的變化才是影響刻蝕導致ITO Open的重要因素,另外,由于ORG層坡度角比較平緩,A和B兩組刻蝕后各條件也未發現明顯區別,分析表明ORG層段差并非導致Open的原因。

為了進一步驗證過刻量對Open的影響,而影響過刻量的主要因素是刻蝕時間,本文在上述實驗的基礎之上設計了不同刻蝕時間的DOE驗證實驗,具體實驗條件信息如表2所示,其中刻蝕時間t1<t2<t3,ITO厚度為T1。

表2 ITO刻蝕時間測試條件Tab.2 ITO etch time test split item

圖5 刻蝕后像素區電鏡圖.(a)split1SEM圖;(b)split2SEM 圖;(c)split3SEM 圖;(d)split4 SEM圖.Fig.5 SEM picture of pixel films after etch.(a)SEM pictureof split1;(b)SEM picture of split2;(c)SEM pictureof split3;(d)SEM picture of split4.

實驗采用相同條件制備樣品,并在同一臺設備上進行刻蝕工藝,不同點就是采用不同的刻蝕時間。刻蝕完成之后進行PR膠剝離,然后進行MM觀察,發現采用split2條件進行刻蝕時,在玻璃邊緣存在輕微的殘留現象,其他條件下未發現。對每個split進行FIB分析,分析結果圖如6所示。

由FIB圖可以看出,split1未發生Open不良,進一步驗證了dep條件不是導致斷裂的原因;split2和split3也均未出現Open現象,而split4的表面和斷面中均可以看到輕微的Open,這是因為在進行ITO刻蝕的過程中,隨著刻蝕時間的延長,過刻量增大,CD bias也逐漸增加,而導致Open;同時刻蝕的均勻性(同一塊基板上單點之間刻蝕差異,以及不同基板之間的刻蝕差異)和穩定性也隨之變差。

圖6 刻蝕后像素區表面和斷面圖.(a)split1表面和斷面圖;(b)split2表面和斷面圖;(c)split3表面和斷面圖;(d)split4表面和斷面圖.Fig.6 The top and cross section picture of pixel films.(a)thetop and cross section picture of split1;(b)the top and cross section picture of split2;(c)the top and cross section picture of split3;(d)the top and cross section picture of split4.

3 結果與討論

由以上實驗分析表明,ITO沉積條件和有機層的段差并不是導致像素電極發生Open的真正原因,而ITO膜層的厚度以及過刻量才是導致Open并最終產生Sand Mura不良的根源。當ITO厚度增大時,在PVX層過孔處應力集中將會增大,在刻蝕過程中應力釋放而導致膜層斷裂。根據現有的設備和量產條件,實驗最終確定ITO厚度T1為Main條件。當ITO膜層厚度一定時,刻蝕時間的長短將會影響刻蝕過程中的過刻量的大小。當刻蝕時間較短時,過刻量也較小,這就容易在玻璃邊緣位置存在殘留現象;而當刻蝕時間延長,過刻量增大,CD bias增加,會出現刻蝕不均而在PVX過孔段差處發生斷裂。經過實驗驗證,當刻蝕時間為t2時刻蝕效果最好,即殘留和Open現象均未發生。

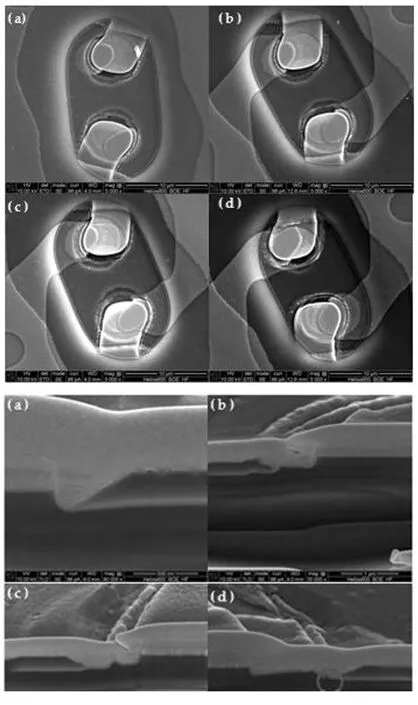

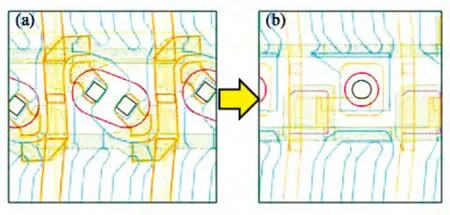

為了消除PVX過孔段差處應力集中及過刻引起的Open問題,從根本上解決Sand Mura不良,可以通過變更設計的方式,變更方案如圖7所示。

圖7 Mask設計變更示意圖.(a)變更前示意圖;(b)變更后示意圖.Fig.7 Schematic of Mask design change.(a)schematic of before change;(b)schematic of after change.

從設計變更示意圖中可以看出,Mask設計變更主要為過孔設計優化,包括以下兩點:一方面PVX過孔仍采用小孔設計的方法,而增大像素ITO面積,這樣像素ITO與PVX過孔便能充分接觸,使得像素電極與PVX過孔段差處的應力相同,以防止Open現象的發生;另一方面ORG大孔設計變更為小孔設計,這樣可以防止ORG大孔中PR膠過厚而導致PVX刻蝕不充分的問題。

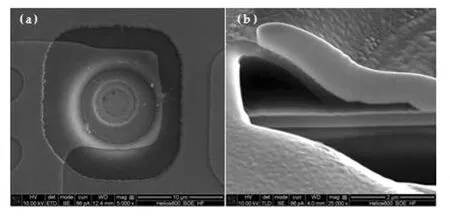

為了驗證這一設計方案的可行性,本文進行了相關的驗證實驗,實驗條件采用與表1中split2相同,以達到對比分析的效果。工藝完成后對樣品進行FIB測試分析,測試結果如圖8所示。由FIB圖中可以看出,Mask設計變更后在像素區表面和斷面圖中均未發現像素ITO電極發生Open現象,實驗結果表明,該設計方案是可行性。

圖8 Mask設計變更后像素區表面和斷面圖.(a)表面圖;(b)斷面圖.Fig.8 The top and cross section picture of pixel films after Mask design change.(a)The top picture;(b)The cross section picture.

4 結 論

研究了在TFT-LCD高分辨率產品開發過程中新出現的Sand Mura問題,通過變更像素電極ITO厚度及刻蝕時間的方案來解決此問題,并驗證了改善方案的可行性。實驗結果表明:Sand Mura發生的根本原因是由于膜厚影響,像素ITO電極在PVX過孔段差處產生應力,在刻蝕過程中由于過刻而發生Open,導致在通電時該處液晶分子偏轉發生異常,進而阻擋了光的透過而形成Mura。通過減少ITO膜層厚度并縮短過刻時間來減小過刻量可以改善Sand Mura問題,不良發生率降至0.3%;本文還研究了通過變更設計方案來防止Sand Mura的發生,實驗證明了設計方案的可行性。

[1] 徐偉,彭毅雯,雷有華,等.TFT-LCD橫向線狀未確認 Mura分析及改善研究 [J].液晶與顯示,2013,28(4):539-546.Xu W,Peng Y W,Lei Y H,et al.Analysis and improvement of TFT-LCD horizontal line unknown Mura[J].Chinese Journal of Liquid Crystals and Displays,2013,28(4):539-546.(in Chinese)

[2] 夏子棋.TFT-LCD制造工藝中 White Mura的消除[D].天津:天津大學,2010.Xia Z Q.White Mura elimination in TFT-LCD manufacture process[D].Tianjin:Tientsin University.(in Chinese)

[3] Pauluth D,Taruml K.Optimization of liquid crystal for television[J].SID,2005,13(8):693-702.

[4] Liu C T.Revolution of the TFT-LCD technology[J].Journal of Display technology,2007,3(4):342-350.

[5] 王志龍,鄭英花,馬亮,等.L0周邊 Mura分析及其改善研究 [J].液晶與顯示,2014,29(5):668-673.Wang Z L,Zheng Y H,Ma L,et al.Research and improvement of L0side Mura[J].Chinese Journal of Liquid Crystals and Displays,2014,29(5):668-673.(in Chinese)

[6] 齊鵬,施園,劉子源.TFT-LCD touch Mura不良的改善和研究 [J].液晶與顯示,2014,28(2):204-209.Qi P,Shi Y,Liu Z Y.Research and improvement of touch Mura in TFT-LCD [J].Chinese Journal of Liquid Crystals and Displays,2014,28(2):204-209.(in Chinese)