任意數值分頻器的FPGA實現

郜繼紅,荀延龍,盧旭盛

(1.內蒙古工業大學 電力學院,內蒙古 呼和浩特 010051;2.內蒙古工業大學 信息學院,內蒙古 呼和浩特 010051)

FPGA是數字系統主流控制器之一,成為目前硬件設計的研究重點[1]。工程人員在數字系統的設計過程中,總會遇到各種各樣數值的分頻要求,比如偶數分頻、奇數分頻、半整數分頻、小數分頻等等,通常一些數字系統設計中,系統不僅對信號頻率有要求嚴格,而且對占空比也有嚴格的要求。整數分頻器的實現比較簡單,可以采用標準的計數器或可編程邏輯器件得以設計實現。但0.5倍整數分頻和等占空比的奇數分頻實現起來就比較困難 ,小數分頻和分數分頻就更加困難難[2]。計數器構成的分頻器,大多只能實現整數分頻,或者只能實現半整數分頻和奇數分頻。而實現小數分頻的多數是專用分頻器,針對這一問題,本人首先設計了各種數值的分頻器,然后增加一個控制模塊,用撥碼開關選擇分頻類型,即由撥碼的二進制數確定是偶數分頻、奇數分頻、小數分頻還是分數分頻。各種數值分頻器由控制模塊決定其分頻的工作狀態,最后綜合起來成為通用分頻器。根據分頻器分頻原理,摸索出了一種簡單的設計方法,設計了任意數值分頻器。

1 偶數分頻器的設計

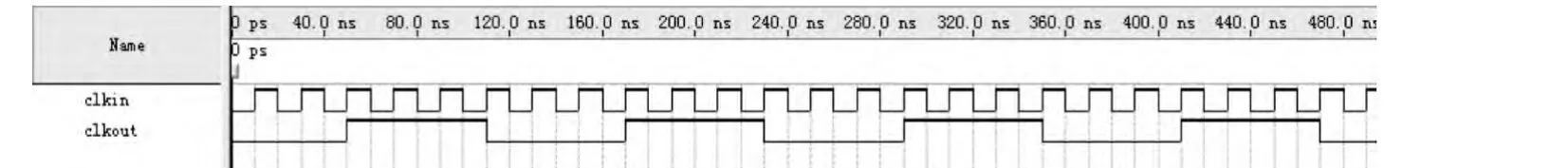

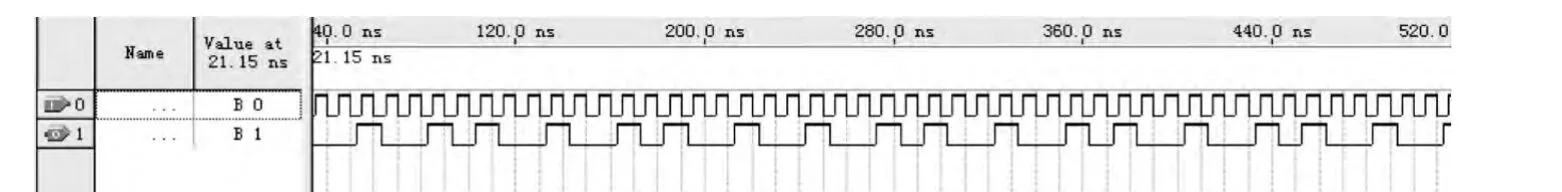

偶數分頻最易于實現,可以利用計數器實現[3-4]。假設要設計M=2N的偶數分頻,當計數值計數到0到K-1時(K用于調節占空比),輸出的電平為1,計數器的計數值K到2N-1時,輸出的狀態為0。計數器計數到2N-1時計數器復位為0。如此循環下去,便可實現占空比為K/2N偶數分頻,這里M和K都是可調整的預置數,K調整占空比,M調節分頻系數。圖1中M取值是6實現的是6分頻。即輸出時鐘頻率是輸入時鐘頻率的1/6。從圖1的仿真結果可以看出k=3=m/2,輸出時鐘占空比為50%。

圖1 CLKIN的6分頻仿真結果Fig.1 Simulation results of 6 frequency divider

2 奇數分頻器的設計

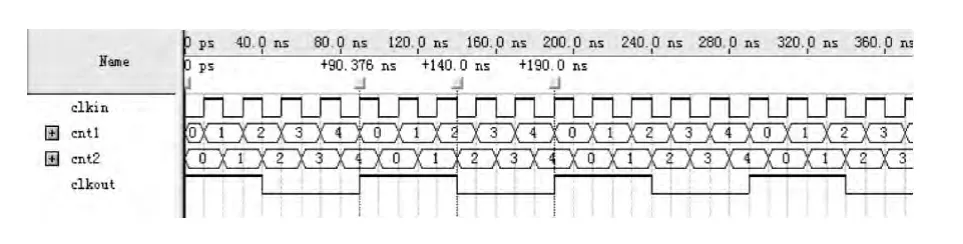

想要實現非50%占空比的奇數分頻,比如實現占空比為20%(1/5)、40%(2/5)、60%(3/5)、80%(4/5)的分頻器,我們可以采用類似于偶數分頻的方案就可以實現。但如果要實現占空比為50%的奇數分頻,就不能用偶數分頻中所采用的方案了。占空比50%奇數分頻實現起來會比較麻煩一點,這是因為計數值為奇數,前半個和后半個周期所包含的不是整數個輸入時鐘脈沖clkin的周期。實現的方法很多,這里介紹一種占用資源少的方法。例如對時鐘脈沖CLKIN進行5分頻,前半個周期包含2.5個clkin周期,后半個周期包含2.5個clkin周期。需要定義兩個計數器,CNT1和CNT2,分別對輸入時鐘的上升沿和下降沿進行計數,當計數值為0~((n/2)-1)時,輸出時鐘信號進行翻轉,同時給計數器一個時鐘復位信號,下一個時鐘的上升沿到來時,計數器重新開始計數,如此循環即可。計數器CNT1和CNT2計數方法完全一樣,只是翻轉邊沿不同。然后把這兩個計數值輸入一個組合邏輯作或運算,CLKOUT=CNT1+CNT2。圖2是CLKIN的5分頻。

圖2 CLKIN的50%占空比的5分頻仿真Fig.2 Simulation results of 5 frequency divider for duty Ratio 50%

推廣為一般方法:欲實現占空比為50%的2N+1分頻器,則需要對分頻時鐘上升和下降沿分別進行1/(2N+1)分頻,然后將兩個分頻所得的時鐘信號作或運算便可得到占空比為50%的2N+1分頻器[4]。

3 小數分頻器的設計

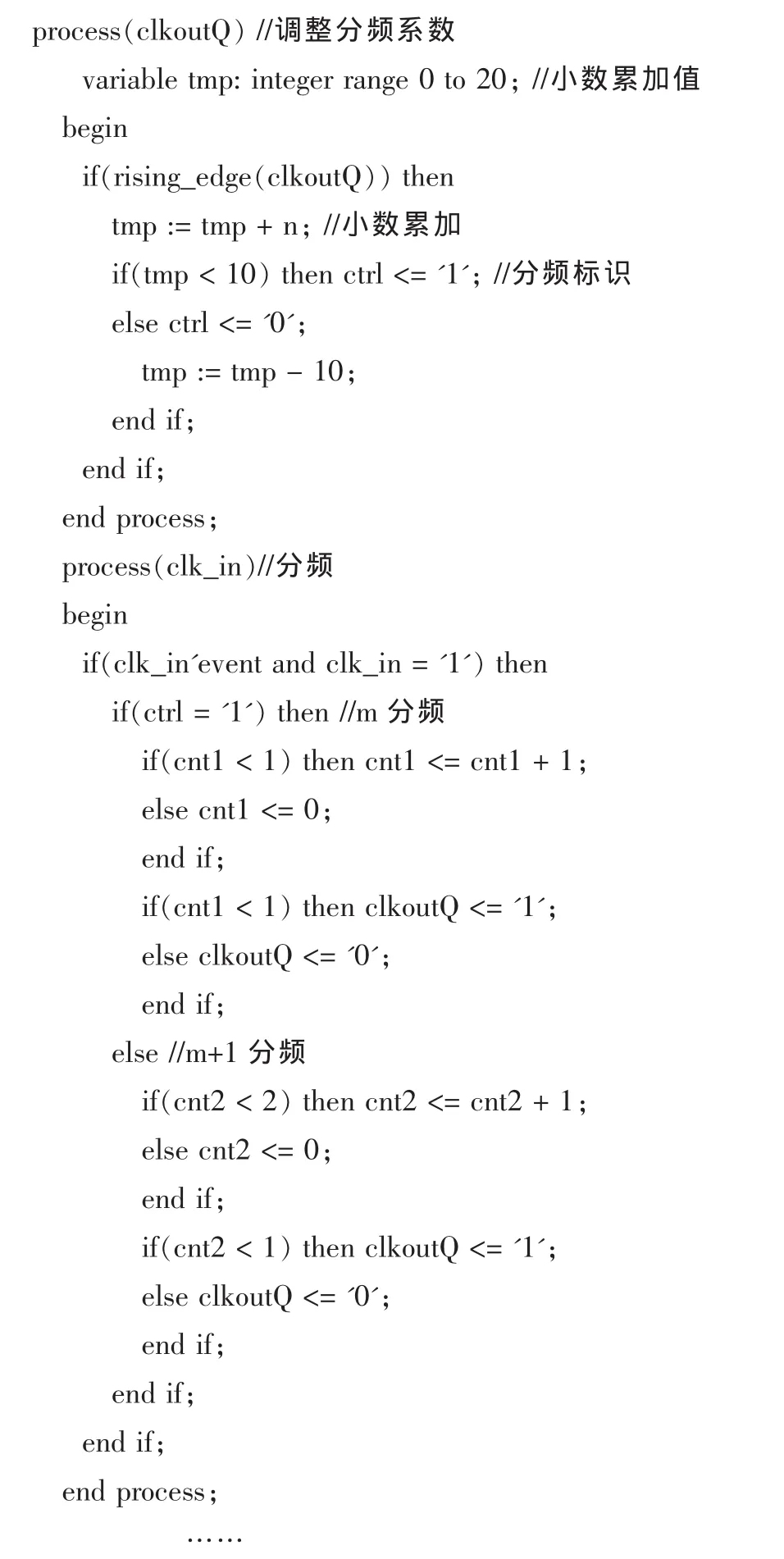

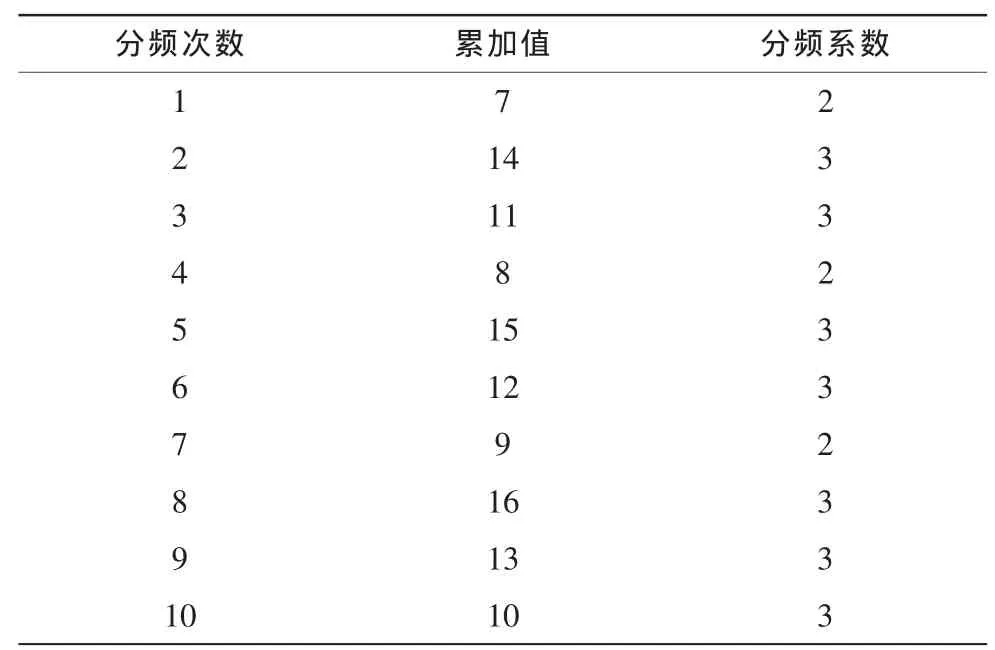

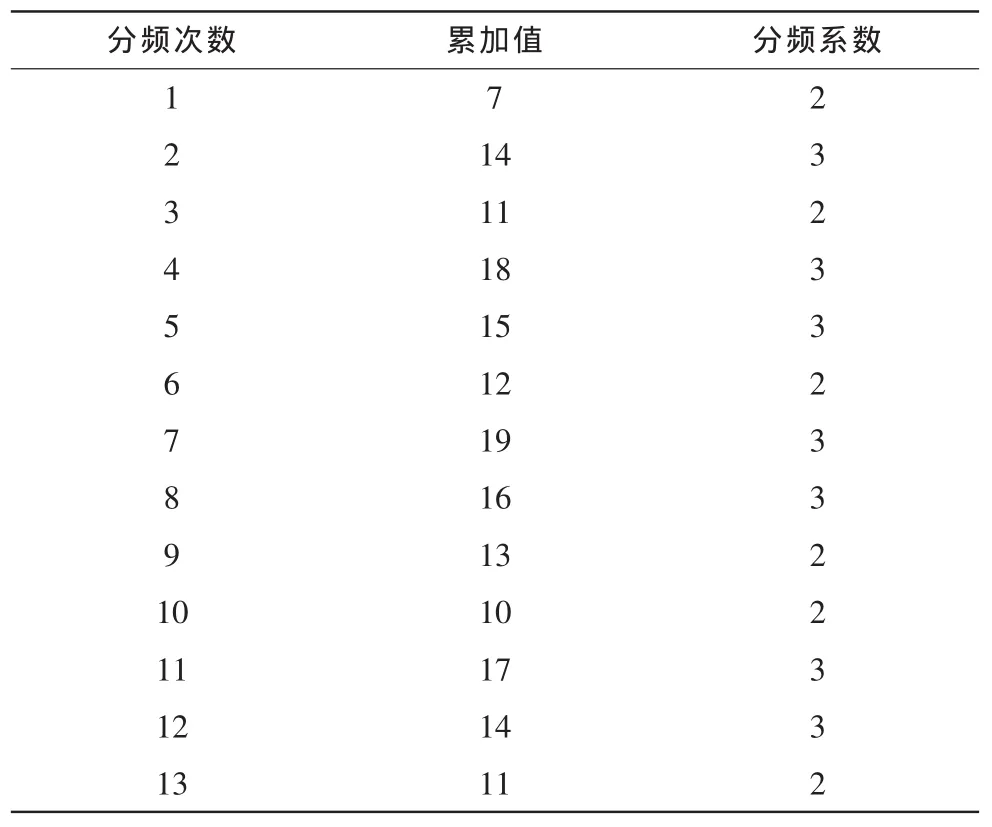

實現小數分頻器的方法很多,但其原理都基本一樣,即通過可變分頻和多次平均的方法得到[5-6]。本設計采用雙模前置小數分頻的方法設計。假設要進行m、n分頻(m、n都是整數,且n<10),因為只有一位小數,所以總共要進行 10次分頻,總的規律是進行n次m+1分頻,10-n次m分頻。假設要進行 k.mn分頻(k、m、n都是整數且 m、n<10),由于小數是 2位,所以總共要進行100次分頻,分頻的規律是進行mn次k+1分頻,100-mn次K分頻。也就是說不管是幾位小數總要進行兩種系數的分頻,兩種分頻究竟如何交叉進行,可以根據一定的規律計算出來,下面以2.7分頻為例進行講解。由上面的分析知道2.7分頻要進行7次3分頻,3次2分頻。總分頻值為:(7×3+3×2)/(7+3)=2.7,將小數部分 7 按倍累加,假設累加的值為A,如果A<10則進行2分頻,A<10的話下一次則加上7,此后,如果A≥10則進行3分頻,3分頻過后再將累加值減去3后與10比較以決定下一次分頻是7分頻還是2分頻,計算過程見表1。圖3是2.7小數分頻仿真波形。小數分頻器部分VHDL核心代碼如下:

表1 2.7分頻計算序列計算值Tab.1 The value of 2.7 dividing calculation sequence

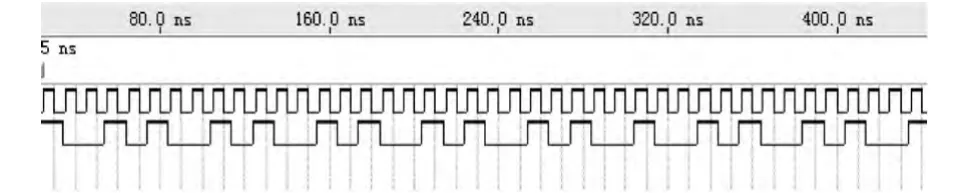

4 分數分頻器設計

圖3 2.7小數分頻仿真波形Fig.3 Simulation waveform of 2.7 frequency divider

表2 分頻規律Tab.2 The law of frequency divider

表2 分頻規律Tab.2 The law of frequency divider

分頻次數 累加值 分頻系數1 7 2 2 14 3 3 11 2 4 18 3 5 15 3 6 12 2 7 19 3 8 16 3 9 13 2 10 10 2 11 17 3 12 14 3 13 11 2

圖4 33/13分頻器仿真波形Fig.4 Simulation waveform of 33/13 frequency divider

5 多數值分頻器的實現

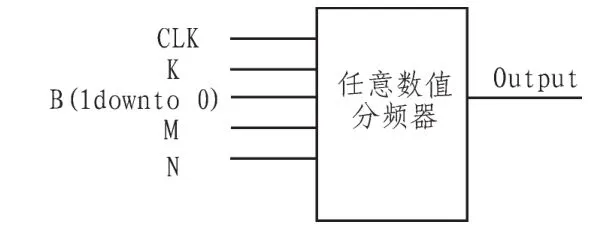

將上述各模塊整合在一起,需要增加一個控制模塊,這樣就構成了多數值分頻器。頂層原理圖見圖5。

圖5 任意分頻器原理圖Fig.5 Schematic diagram of any frequency divider

當B=00時,實現整數分頻,當B=01時實現占空比50箛的奇數分頻,B=10時實現小數分頻,B=11時實現分數分頻。其中M、K控制整數分頻的分頻系數以及占空比。小數分頻時M、N分別調整整數部分和小數部分。分數分頻時K調整整數部分,M,N調整分母和分子值,雖然預置端口較多,但可調整性很好。

6 結束語

文中給出了基于FPGA的多數值分頻器的設計方法,設計采用自頂而下的設計方法,進行功能模塊的劃分,該分頻器可以實現偶數、奇數、小數、分數的分頻,有良好的可移值性,本設計選用EP2C5Q208C型FPGA芯片實現,從綜合配置后的配置報告可以看出,本分頻器占用FPGA資源很小。仿真結果和硬件測試結果驗證了這個設計的有效性。對相關人員有一定的參考價值。

[1]張靜亞.FPGA系統設計中資源分配的分析和研究[J].信息化研究,2009,35(3):37-39.

[2]王廣義,趙衛華,趙艷秋.一種小數分頻器的設計及性能研究[J].自動化技術與應用,2007,26(9):101-102.

[3]潘松,黃繼業.EDA技術實用教程[M].3版.北京:科學出版社,2006.

[4]劉愛榮,王振成,陳揚,等.EDA技術CPLD/FPGA開發應用簡明教程[M].2版.北京:清華大學出版社,2013.

[5]李炯.一種基于FPGA的任意分頻器設計與實現[J].現代電子技術,2012,25(24):185-186

[6]黃守麟.基于FPGA的超高精度任意小數分頻器的設計[J].計算機工程與應用,2008,(33s):485-487.

[7]周鵬,和衛星,匡敏馳,等.FPGA在PC-104系統I/O設備擴展中的應用[J].工業儀表與自動化裝置,2013(2):50-53,72.

[8]程光偉,劉大偉.基于FPGA的異步FIFO的研究和設計[J].工業儀表與自動化裝置,2013(2):67-69,75.