一種基于SATA硬盤陣列的數據存儲與控制系統設計

李秦

(陜西財經職業技術學院 陜西 咸陽 712000)

隨著現代存儲技術的發展,硬盤存儲容量和速度也越來越快。當前單塊的硬盤其對數據的讀寫速度通常在100 MBytes/s,而隨著現代科學實驗對數據采集的速度的要求,200 MBytes/s、400 MBytes/s甚至更高。而要達到如此高的速度,則必須要采用多塊硬盤同時對數據進行讀寫才能完成。如果要采用多塊硬盤對數據進行讀寫,則需要通過硬盤陣列控制系統對其進行控制才能實現。對此本文采用一種基于SATA硬盤陣列的控制系統,并對其實現進行了詳細的設計。

1 系統原理

在對數據的存儲當中,之所以磁盤陣列能夠實現對多塊不同硬盤的并行操作,其主要是由磁盤當中數據傳輸特性來進行決定的。在通常狀態下,在對磁盤進行數據寫入的時候,主機通常首先會將數據寫入到磁盤的高速緩存當中。當其中的緩存寫滿了之后,主機則需要等待其緩存為空,當緩存變為空后,主機則開始進入到下一次的讀寫存儲。磁盤控制器在緩存被寫滿之后,將其中的數據通過高速緩存的方式寫入到磁盤的介質當中。數據在高速緩存寫入的過程當中其速度通常都比較快。當數據在通過高速緩存被寫入到磁盤介質的過程中,因為其中哦的磁頭其平均的尋道時間通常表現都比較長,并且受到主軸轉速不高等相關因素的影響,從而造成了磁盤介質寫入的速度變得非常的慢,并且其寫入的速度要遠遠比高速緩存的速度慢。由此兩者因為在寫入速度方面存在的差異,造成了當高速緩存在寫滿后,磁盤控制器在對高速緩存進行讀寫的過程中,可先對其他的設備進行高速的緩存,最后再來寫當前設備的緩存區。通過這樣的方式在減少了主機寫入高速緩存的時間,并可在同一個時間對多個不同的硬盤進行同時寫入操作。

2 系統整體硬件方案設計

2.1 系統整體方案

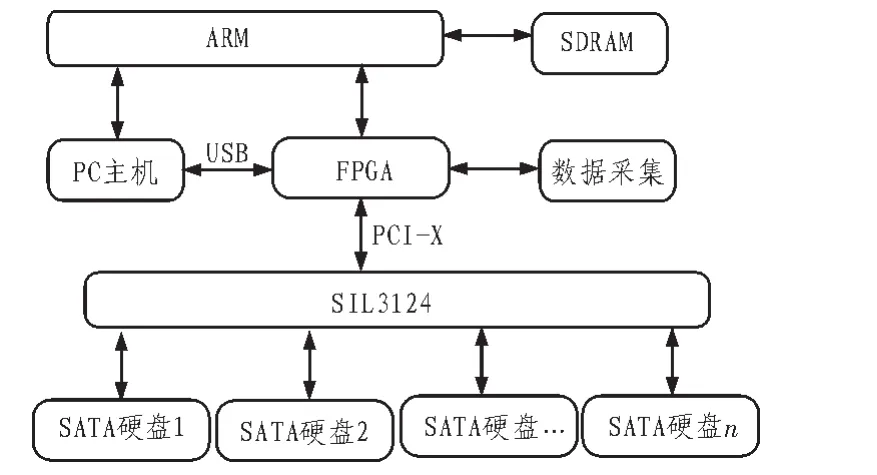

為更好的提高該系統的性能,文中將該控制系統設計為如圖1所示。

圖1 系統整體架構設計Fig.1 Overall system architecture design

該系統在初始化之后,通過相關的參數設定,從而進入到相應的工作模式,而當數據在存儲的時候,其首先是通過ARM對硬盤當中的基本分區信息進行讀取,從而借助ARM的處理功能找到在硬盤當中存在的空閑信息,并發出寫的命令。通過這樣的方式,在完成對所有空閑硬盤的搜索之后,再回到第一塊硬盤的操作當中。同時,在圖1的整體系統設計當中,通過數據采集器對你數據的采集,其首先是通過FPGA的邏輯處理功能,對ARM狀態進行檢測,在確認可以對數據進行寫入之后,將數據從FPGA中的FIFO當中讀寫,并通過FPGA當中的PCI-X總線,將命令送入到SI13124處理器當中,最后該處理器則自動按照原始設定的程序將命令發送給制定的地址。當數據存儲工作完成之后,ARM在直接對其中的FAT表進行更新,從而完成了對整個控制系統硬盤的存儲。

而在圖1中可以看出,FPGA與主機的連接是通過USB接口的方式,通過USB器件則將系統映射盤符,而主機則以移動硬盤的方式對系統進行訪問,在此時FPGA則通過該USB器件將系統的命令傳遞給SI13124,SI13124則根據命令的要求將其完成,并執行相應的操作,FPGA主要的功能則是將其中的護具進行拆包,并將其轉換為字節送入到USB器件當中。當主機通過網卡方式進行連接的時候,ARM則將該系統映射為FTP,主機則如訪問FTP的方式進行訪問。在這種訪問模式下的ARM其同樣通過FPGA的邏輯功能,向SI13124發出命令并執行。在圖1中通過ARM連接SDRAM,其主要的作用則是通過SDRAM為ARM提供足夠的空間,因為本身ARM內部的存儲空間是比較小的。當系統在遇到比較大的程序的時候,可將其直接存到SDRAM當中,而不需要存入到ARM中。

2.2 系統器件選擇

對該系統的設計,其主要的目的就是要通過磁盤陣列的方式提高對數據存儲的速度,并可脫離主機進行獨立的工作,同時還可與主機進行連接進行對數據的回收。對此,結合圖1對系統的設計,將系統分為USB接口、SATA磁盤列陣、FPGA磁盤接口控制器、ARM邏輯控制、ARM處理器等構成。其中主要對系的工作模式和文件系統進行管理;USB接口其主要的功能也是實現與主機的聯機,從而得到對數據回收的目的;SATA控制器的作用則指實現FPGA與SATA的邏輯的轉換,通過PCI-X的方式來實現,并對數據進行拆包和打包。因此,本系統中對硬件的選擇中,處理器選擇AT91 RM9200,該處理器具有性價比高、易用、功耗低等特點;對FPGA邏輯處理模塊的選擇采用CycloneⅡ系列,該系列具有低成本、高密度等優點;USB接口采用CY7V68013A芯片,該芯片其傳輸速率可達到56 Mbyres/s,同時其中智能可有效的減少開發時間,并確保USB接口的兼容性;總線傳輸則采用PCI-X傳輸協議,該傳輸協議其最高的傳輸速率可達到1 GB/S,并適用于服務器或工作站等平臺。

3 系統軟件設計

3.1 FPGA邏輯設計

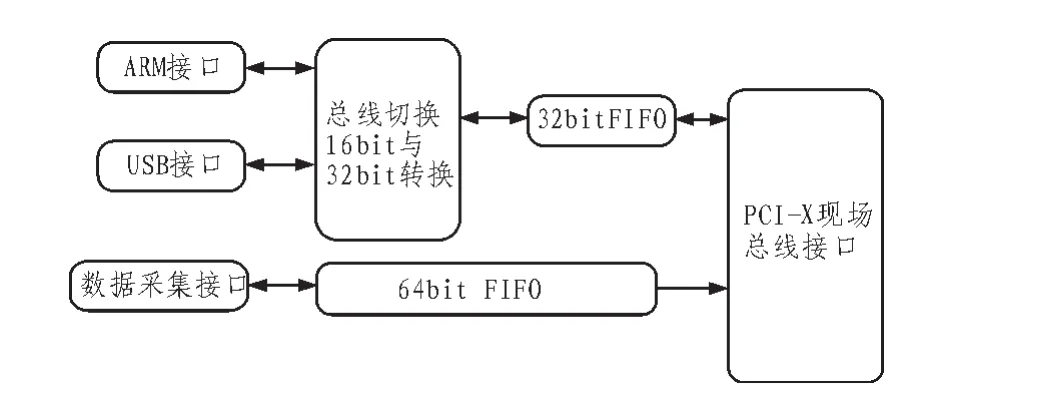

在該系統當中對的邏輯進行設計則采用語言來進行實現,其具體的邏輯框架圖則如圖2所示:

圖2 FPGA內部邏輯Fig.2 FPGA internal logic

通過圖2可以看出,該部分包括3個主要的邏輯設計,與邏輯控制設計、接口設計、與硬盤控制器等部分。同時由于該系統進行設計的時候,與的傳輸中,其總線采用的是64位,在工作方式的時候為低32位,而在當中的總線是為32位,當總線處在工作模式的時候則為16位,以此需要將其從32位轉換為16位,對此本文在對該問題進行處理的時候則采用32位的模式實現上述接口的通訊,其具體的轉換的方式則如圖3所示。

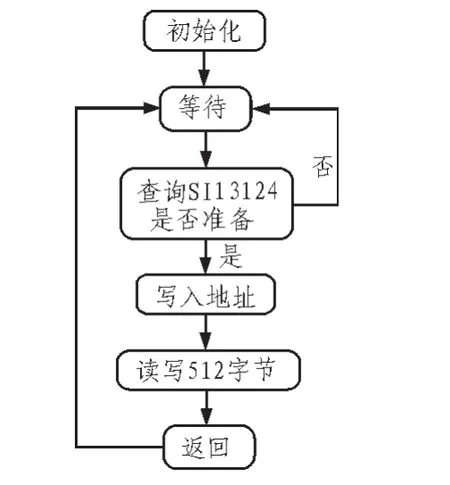

圖3 系統數據流程設計Fig.3 System data flow design

3.2 硬盤讀寫程序設計

系統在進行初始化并設定好最初的工作模式的時候,對SⅠ13124的狀態進行讀取,從而確認硬盤準備好可向硬盤的端口寫入地址/命令,通過SATA硬盤接口控制器執行相關的操作,并最后返回并進行下一次操作。

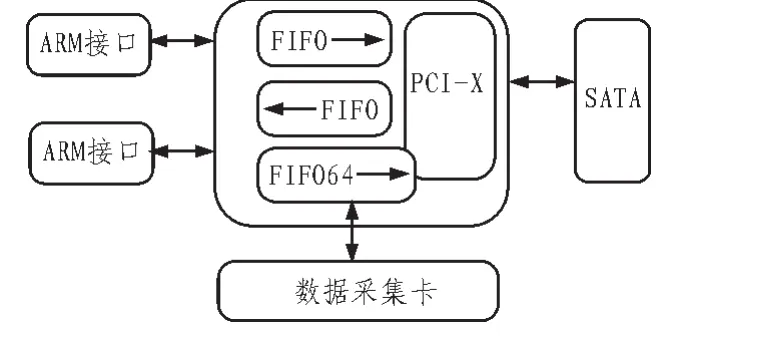

4 仿真結果

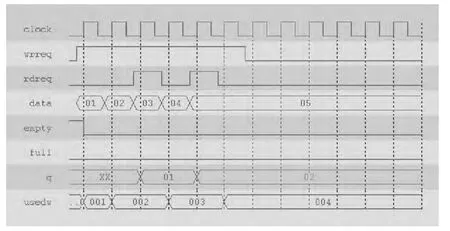

通過采用MATLAB軟件對上述的程序進行仿真,從而可以得到如圖4的讀寫時序圖。

圖4 硬盤讀寫程序設計Fig.4 Hard literacy program design

同時通過上述設計,SATA硬盤傳輸速度可達到300 MB/s,PCI-X總線帶寬可達到1 GB/s。

圖5 ARM讀寫FIFO時序圖Fig.5 Read and write timing diagram

5 結論

通過采用at91 rm9200、cYCLONEⅡ等對系統CPU進行和FPGA進行設計,從而實現SATA硬盤傳輸最大速度直接達到300 MB/s,以此最終實現對數據的高速存儲和讀寫。

[1]張志煒,呂幼新.基于SATA硬盤和FPGA的高速數據采集存儲系統[J].電子設計工程,2011(21):166-169.ZHANG Wei,LV You-xin.SATA hard drives and FPGA-based high-speed data acquisition and storage system[J].Electronic Design Engineering,2011(21):166-169.

[2]王超,劉偉,張德聰.基于SATA的嵌入式直接存儲系統[J].計算機工程,2012(12):232-235.WANG Chao,LIU Wei,ZHANG De-cong.Directly embedded SATA-based storage system[J].Computer Engineering,2012(12):232-235.

[3]吳芝路,馮陽凱,任廣輝.基于SATA接口硬盤數據存儲系統設計[J].哈爾濱商業大學學報:自然科學版,2008(5):550-552.WU Zhi-lu,FENG Yang-kai,REN Guang-hui.Design interface hard disk data storage system based on SATA[J].Harbin University of Commerce:Natural Science,2008(5):550-552.

[4]林連雷,楊英,姜守達.基于PCI總線的雷達信號采集分析系統設計[J].電子測量與儀器學報,2007(4):82-86.LIN Lian-lei,YANG Ying.Desinger and keep up to design a radar signal acquisition and analysis system based on PCI bus[J].Electronic Measurement and Instrument,2007(4):82-86.

[5]孫海波,王曉斌,李雅梅.基于SATA接口固態硬盤的高速存儲系統設計[J].遙測遙控,2014(2):48-52.SUN Hai-bo,WANG Xiao-bin,LI Ya-mei.Design high-speed SATA interface SSD-based storage system[J].Remote Telemetry,201(2):48-52.

[6]劉勇.基于USB2.0和DDR2的數據采集系統設計與FPGA實現[J].電子元器件應用,2010,12(10):48-50.LIU Yong.USB2.0 and DDR2-based data acquisition system design and FPGA[J].Electronic Component Applications,2010,12(10):48-50.