1553B總線接口模塊測試設(shè)備的設(shè)計與實現(xiàn)

樊江鋒 黃意 姚莉娟

摘 要: 1553B多路傳輸數(shù)據(jù)總線接口模塊作為一種通用模塊在我國自行研制的機(jī)載設(shè)備上大量使用,在研究1553B 總線接口模塊測試技術(shù)的理論基礎(chǔ)上,主要研究多塊1553B總線接口模塊的測試設(shè)備的設(shè)計與實現(xiàn),為1553B總線接口模塊的測試提供技術(shù)基礎(chǔ)。

關(guān)鍵詞: 1553B總線接口; LBE總線; 測試技術(shù); 80486CPU

中圖分類號: TN915.04?34 文獻(xiàn)標(biāo)識碼: A 文章編號: 1004?373X(2015)15?0022?03

Design and realization of test equipment for 1553B bus interface module

FAN Jiangfeng, HUANG Yi, YAO Lijuan

(AVIC Xian Aeronautics Computing Technique Research Institute, Xian 710119, China)

Abstract: As a general module, 1553B multiplex transmission data bus interface module has been extensively used in airborne equipments made in China. On studying theoretical basis of 1553B bus interface modules testing technology, test equipment design and implementation of multi?block1553B bus interface module are researched. It provides a technical foundation for 1553B bus interface module testing.

Keywords: 1553B bus interface; LBE bus; testing technology; 80486CPU

0 引 言

MIL?STD?1553B總線是美軍為其航空應(yīng)用定義的串行多路數(shù)據(jù)總線標(biāo)準(zhǔn),其數(shù)據(jù)傳輸率為1 Mb/s,具有實時性好、抗干擾能力強(qiáng)、冗余備份、易于擴(kuò)展等優(yōu)點,是一種確定的、可靠的、命令/響應(yīng)式數(shù)據(jù)通信標(biāo)準(zhǔn)。我國于20世紀(jì)90年代引進(jìn)和使用該標(biāo)準(zhǔn)。GJB289A?97 飛機(jī)內(nèi)部時分制指令/響應(yīng)型多路傳輸數(shù)據(jù)總線,簡稱GJB289A,是我國制定的與美國1553B相對應(yīng)的軍用航空總線標(biāo)準(zhǔn),目前該標(biāo)準(zhǔn)已廣泛應(yīng)用在國內(nèi)機(jī)載航空電子系統(tǒng)通信網(wǎng)絡(luò)中,1553B總線接口模塊(也稱MBI模塊)作為一種通用模塊在我國自行研制的機(jī)載設(shè)備上大量使用。本文在研究1553B總線接口模塊測試技術(shù)的理論基礎(chǔ)上,主要研究多塊1553B總線接口模塊的測試設(shè)備的設(shè)計與實現(xiàn)。

1 1553B總線測試設(shè)備的設(shè)計與實現(xiàn)

1.1 1553B總線概述

1553B總線系統(tǒng)主要包括終端模塊、耦合器、電纜、電纜連接器、終端匹配器等,它們通過兩根余度電纜連接,最多可掛接32個終端。在總線通信過程中一條總線(A總線)工作,另一條總線(B總線)處于熱備份狀態(tài);總線耦合有直接耦合與變壓器耦合兩種方式。

1553B總線通信系統(tǒng)聯(lián)接的終端按其作用分為總線控制器(BC)、遠(yuǎn)程終端(RT)和總線監(jiān)控器(BM或MT)。BC是在總線上惟一建立和啟動數(shù)據(jù)傳輸任務(wù)的控制終端;RT是數(shù)據(jù)總線上用戶子系統(tǒng)的終端,在BC的控制下發(fā)送或接收總線數(shù)據(jù);總線監(jiān)控器(BM或MT)監(jiān)控總線上的信息傳輸,并能對總線上的數(shù)據(jù)進(jìn)行記錄和分析,本身不參與總線通信。每個終端被分配了惟一的總線形式,各終端之間信息傳輸方式有:BC到RT、RT到BC、RT到RT、廣播方式和系統(tǒng)控制方式。

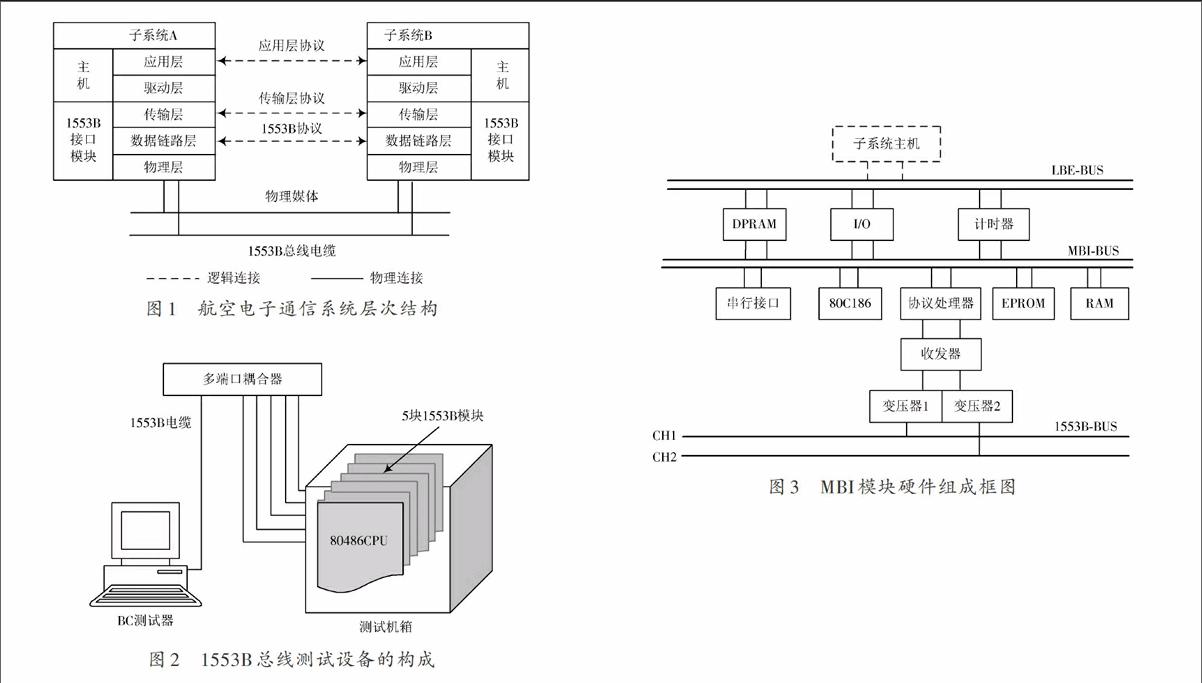

機(jī)載航電系統(tǒng)分為五層,如圖1所示, MBI模塊完成較低三層,即傳輸層、數(shù)據(jù)鏈路層和物理層的功能, 其中MBI模塊硬件完成物理層和數(shù)據(jù)鏈路層功能, MBI模塊上駐留的通信軟件完成傳輸層功能,較高兩層即驅(qū)動層和應(yīng)用層由駐留于子系統(tǒng)主處理機(jī)上的驅(qū)動軟件和應(yīng)用軟件完成。

1.2 1553B總線接口模塊測試設(shè)備的構(gòu)成

多1553B總線接口模塊測試系統(tǒng)由測試機(jī)箱、1553B測試電纜和宿主機(jī)CPU模塊、1553B測試板卡構(gòu)成,如圖2所示。宿主機(jī)CPU利用機(jī)箱母板上的1553B總線網(wǎng)絡(luò),對1553B總線接口模塊的接口實現(xiàn)全面、實時地傳輸和功能測試,在提高測試效率的同時,改善了接口測試的完整性和覆蓋率。

圖1 航空電子通信系統(tǒng)層次結(jié)構(gòu)

圖2 1553B總線測試設(shè)備的構(gòu)成

宿主機(jī)選用標(biāo)準(zhǔn)的80486CPU處理器模塊,80486CPU模塊的總線接口為LBE總線,1553B總線接口模塊的宿主機(jī)總線接口為LBE總線。整個測試設(shè)備設(shè)計為可以用1塊80486CPU處理器模塊初始化5塊1553B總線接口模塊為RT工作模式,宿主機(jī)80486CPU模塊和1553B總線接口模塊均符合LBE總線的標(biāo)準(zhǔn)。80486CPU處理器模塊提供實時操作系統(tǒng)VxWorks和軟件開發(fā)環(huán)境TORNADO,方便進(jìn)行測試軟件開發(fā)和調(diào)試。

1.3 1553B總線接口模塊工作原理

1553B總線接口模塊按其功能可分為遠(yuǎn)程終端(RT)和總線控制器(BC)。本文主要研究RT模式下1553B總線接口模塊的測試。

1.3.1 遠(yuǎn)程終端(RT)和總線控制器(BC)

當(dāng)1553B總線接口模塊作為遠(yuǎn)程終端時,一直監(jiān)測來自1553B總線上的信息,1553B總線接口模塊接收總線控制器的有效指令,并將接收數(shù)據(jù)按一定順序要求存放在共享存儲器中,供子系統(tǒng)查用。如果子系統(tǒng)有數(shù)據(jù)需要向總線發(fā)出時,系統(tǒng)主機(jī)按照規(guī)定將自己要求服務(wù)的子地址等有關(guān)信息寫入1553B總線接口模塊,當(dāng)總線控制器檢測到遠(yuǎn)程終端的請求之后,便組織相應(yīng)的消息傳輸。

當(dāng)1553B總線接口模塊作為BC時,子系統(tǒng)主機(jī)根據(jù)通信系統(tǒng)要求將指令數(shù)據(jù)組成的總線表加載到1553B總線接口模塊中,1553B總線接口模塊根據(jù)總線表組織消息傳輸,并接收來自各RT的狀態(tài)字。

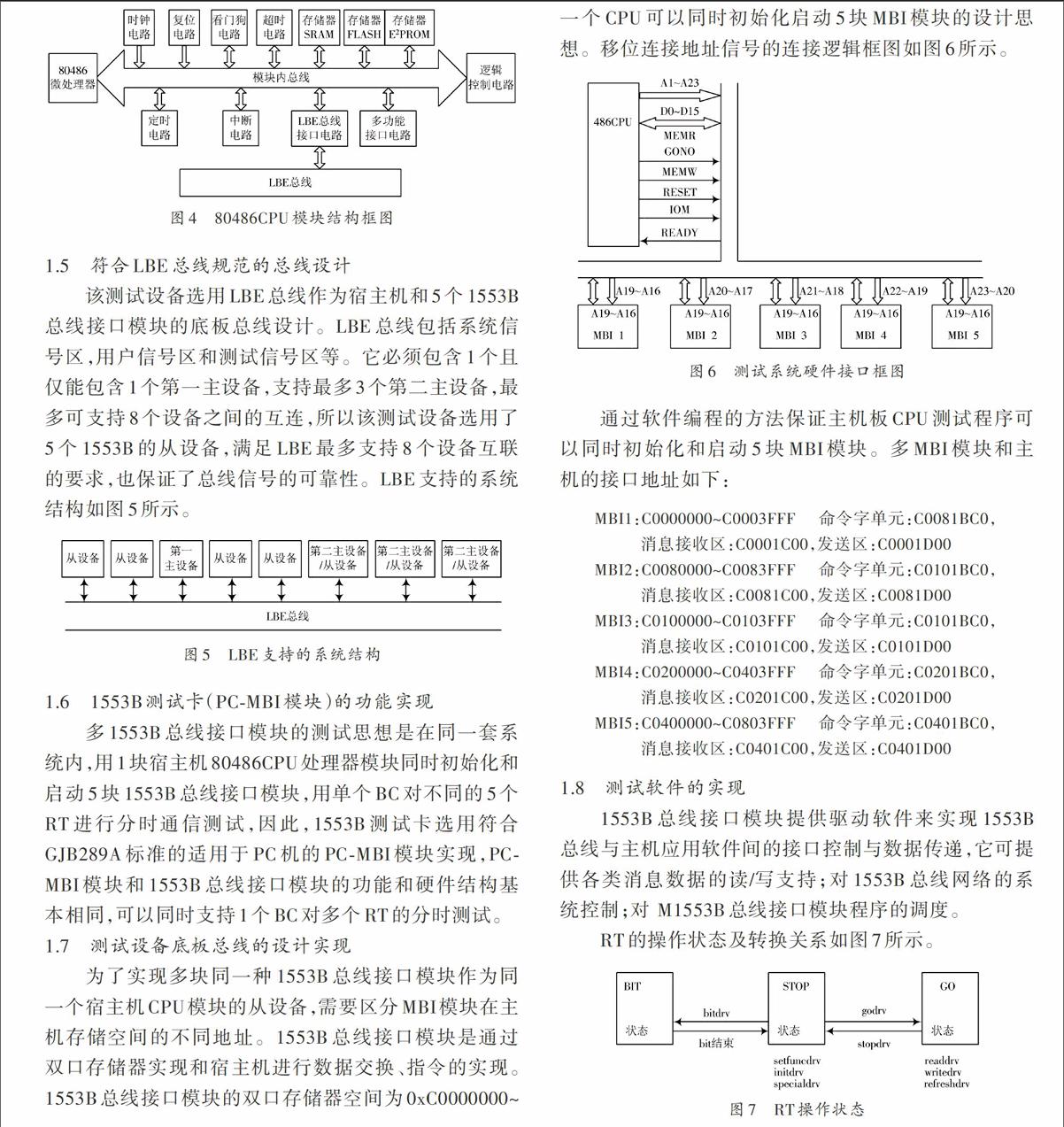

1.3.2 1553B總線接口模塊硬件結(jié)構(gòu)

1553B總線接口模塊包含1553B總線接口模塊硬件和1553B總線接口模塊通信軟件,1553B總線接口模塊硬件組成邏輯框圖如圖3所示。

圖3 MBI模塊硬件組成框圖

1553B總線接口模塊硬件主要包括通信控制器、共享存儲器、1553B協(xié)議處理器、實時時鐘、時間間隔計數(shù)器(DT)、雙通道總線收/發(fā)器和隔離變壓器、與子系統(tǒng)主機(jī)接口控制邏輯、內(nèi)部控制邏輯和串行口電路。

1.4 宿主機(jī)80486CPU模塊設(shè)計與實現(xiàn)

1553B總線測試設(shè)備宿主機(jī)設(shè)計為80486CPU處理器模塊,該模塊符合LBE總線標(biāo)準(zhǔn),滿足測試1553B總線接口模塊硬件時序邏輯。

80486處理器模塊主要實現(xiàn)程序處理、中斷響應(yīng)、數(shù)據(jù)傳輸?shù)认到y(tǒng)功能,其中80486DX?33為32位處理器,負(fù)責(zé)指令執(zhí)行、邏輯運算和整數(shù)運算等操作,浮點和函數(shù)等數(shù)值處理;時鐘電路產(chǎn)生時鐘信號實現(xiàn)系統(tǒng)同步;復(fù)位電路產(chǎn)生系統(tǒng)復(fù)位信號;看門狗電路監(jiān)控軟件運行軌跡;定時電路實現(xiàn)定時計數(shù)功能;中斷電路實現(xiàn)中斷控制功能;存儲器功能模塊主要包括FLASH,RAM和E2PROM,其中FLASH用于存放用戶程序,RAM可用于調(diào)試程序和存儲變量、工作單元或中間結(jié)果,E2PROM用于存放掉電保護(hù)的數(shù)據(jù);LBE總線接口電路主要負(fù)責(zé)與LBE總線上的其他模塊的連接;時序邏輯和控制邏輯電路主要負(fù)責(zé)產(chǎn)生模塊內(nèi)部邏輯的時序和控制信號,提供模塊內(nèi)部資源訪問就緒應(yīng)答;多功能接口電路實現(xiàn)了兩個串行接口,一個16位的定時/計數(shù)器,并且有檢測模塊內(nèi)部的某些狀態(tài)和控制模塊內(nèi)部的某些功能電路的作用,其中串行接口可用于人機(jī)對話和聯(lián)機(jī)調(diào)試;檢測電路提供CPU自檢測功能、訪問超時檢測功能、看門狗故障檢測功能和LBE總線測試信號支持等功能。模塊結(jié)構(gòu)框圖如圖4所示。

圖4 80486CPU模塊結(jié)構(gòu)框圖

1.5 符合LBE總線規(guī)范的總線設(shè)計

該測試設(shè)備選用LBE總線作為宿主機(jī)和5個1553B總線接口模塊的底板總線設(shè)計。LBE總線包括系統(tǒng)信號區(qū),用戶信號區(qū)和測試信號區(qū)等。它必須包含1個且僅能包含1個第一主設(shè)備,支持最多3個第二主設(shè)備,最多可支持8個設(shè)備之間的互連,所以該測試設(shè)備選用了5個1553B的從設(shè)備,滿足LBE最多支持8個設(shè)備互聯(lián)的要求,也保證了總線信號的可靠性。LBE支持的系統(tǒng)結(jié)構(gòu)如圖5所示。

圖5 LBE支持的系統(tǒng)結(jié)構(gòu)

1.6 1553B測試卡(PC?MBI模塊)的功能實現(xiàn)

多1553B總線接口模塊的測試思想是在同一套系統(tǒng)內(nèi),用1塊宿主機(jī)80486CPU處理器模塊同時初始化和啟動5塊1553B總線接口模塊,用單個BC對不同的5個RT進(jìn)行分時通信測試,因此,1553B測試卡選用符合GJB289A標(biāo)準(zhǔn)的適用于PC機(jī)的PC?MBI模塊實現(xiàn),PC?MBI模塊和1553B總線接口模塊的功能和硬件結(jié)構(gòu)基本相同,可以同時支持1個BC對多個RT的分時測試。

1.7 測試設(shè)備底板總線的設(shè)計實現(xiàn)

為了實現(xiàn)多塊同一種1553B總線接口模塊作為同一個宿主機(jī)CPU模塊的從設(shè)備,需要區(qū)分MBI模塊在主機(jī)存儲空間的不同地址。1553B總線接口模塊是通過雙口存儲器實現(xiàn)和宿主機(jī)進(jìn)行數(shù)據(jù)交換、指令的實現(xiàn)。1553B總線接口模塊的雙口存儲器空間為0xC0000000~0xC0003FFFH,0xC*******H的高位地址片選信號由80486CPU模塊通過SEL0給出并連接到MBI模塊的大存儲器片選CS引腳。MBI模塊的宿主機(jī)接口部分電路用來譯碼的LBE總線地址信號A19~A16和MBI模塊的大存儲器片選CS來實現(xiàn)0xC0000000~0xC0003FFFH,可以將80486CPU處理器的A23~A16與MBI模塊的A19~A16地址信號移位連接,實現(xiàn)1553B總線接口模塊占用宿主機(jī)80486CPU不同的存儲器空間設(shè)計,實現(xiàn)一個CPU可以同時初始化啟動5塊MBI模塊的設(shè)計思想。移位連接地址信號的連接邏輯框圖如圖6所示。

圖6 測試系統(tǒng)硬件接口框圖

通過軟件編程的方法保證主機(jī)板CPU測試程序可以同時初始化和啟動5塊MBI模塊。多MBI模塊和主機(jī)的接口地址如下:

MBI1:C0000000~C0003FFF 命令字單元:C0081BC0,

消息接收區(qū):C0001C00,發(fā)送區(qū):C0001D00

MBI2:C0080000~C0083FFF 命令字單元:C0101BC0,

消息接收區(qū):C0081C00,發(fā)送區(qū):C0081D00

MBI3:C0100000~C0103FFF 命令字單元:C0101BC0,

消息接收區(qū):C0101C00,發(fā)送區(qū):C0101D00

MBI4:C0200000~C0403FFF 命令字單元:C0201BC0,

消息接收區(qū):C0201C00,發(fā)送區(qū):C0201D00

MBI5:C0400000~C0803FFF 命令字單元:C0401BC0,

消息接收區(qū):C0401C00,發(fā)送區(qū):C0401D00

1.8 測試軟件的實現(xiàn)

1553B總線接口模塊提供驅(qū)動軟件來實現(xiàn)1553B總線與主機(jī)應(yīng)用軟件間的接口控制與數(shù)據(jù)傳遞,它可提供各類消息數(shù)據(jù)的讀/寫支持;對1553B總線網(wǎng)絡(luò)的系統(tǒng)控制;對 M1553B總線接口模塊程序的調(diào)度。

RT的操作狀態(tài)及轉(zhuǎn)換關(guān)系如圖7所示。

圖7 RT操作狀態(tài)

MBI驅(qū)動函數(shù)程序設(shè)計如下:

initdrv:啟動MBI板初始化,并置MBI板于停止?fàn)顟B(tài);

godrv:啟動MBI板的工作,從而開始通信;

stopdrv:停止MBI板的工作;

bitdrv:啟動MBI板進(jìn)行自測試,啟動自測試之前應(yīng)先調(diào)用stopdrv;

specialdrv:啟動MBI板的指定傳輸程序;

readdrv:從MBI雙口存貯器讀1553B總線接收的新數(shù)據(jù);

writedrv:將發(fā)送到1553B總線上的數(shù)據(jù)寫入MBI雙口存貯器;

refreshdrv:搜索MBI的數(shù)據(jù)緩沖區(qū),檢查輸入消息的更新情況;

setfuncdrv:設(shè)置MBI板的工作方式(BC或RT)。

測試設(shè)備上的測試軟件駐留在宿主機(jī)80486CPU的應(yīng)用FLASH區(qū),測試軟件主要調(diào)用驅(qū)動軟件來啟動5塊1553B總線接口模塊同時處于運行狀態(tài)下,通過PC?MBI模塊和5塊1553B總線的通信網(wǎng)絡(luò)來實現(xiàn)測試。

2 結(jié) 語

本文主要介紹了一種多1553B總線接口模塊測試設(shè)備的設(shè)計與實現(xiàn),通過對一個宿主機(jī)同時訪問多塊1553B總線接口模塊測試技術(shù)的研究和應(yīng)用,解決了傳統(tǒng)的1553B總線接口模塊接口測試方法為宿主機(jī)和1553B總線接口模塊一對一測試的問題,為1553B總線接口模塊的批量生產(chǎn)、調(diào)試、試驗提供了測試方法和技術(shù)。

參考文獻(xiàn)

[1] 于海勛,苗紫暉.基于1553B的一種測試系統(tǒng)設(shè)計[J].西安工業(yè)大學(xué)學(xué)報,2009,29(2):172?176.

[2] 楊建新,刁平.機(jī)載雙余度1553B 總線傳輸線路檢測系統(tǒng)的設(shè)計與實現(xiàn)[J].計算機(jī)測量與控制,2008,16(11):1525?1527.

[3] 國防科工委.GJB29A?97數(shù)字式時分制指令/響應(yīng)型多路傳輸數(shù)據(jù)總線[S].北京:國防科工委,1997.

[4] 吳云忠.基于PCI接口的1553B總線控制軟件實現(xiàn)[J].現(xiàn)代電子技術(shù),2013,36(24):47?49.

[5] 劉明陽,張建東,呂程.Vxworks下1553B通信系統(tǒng)的設(shè)計與實現(xiàn)[J].計算機(jī)測量與控制,2012,20(8):2303?2306.

[6] 王海鋒,梁晶晶,田苗.某型測試系統(tǒng)中1553B總線通信設(shè)計與應(yīng)用[J].現(xiàn)代電子技術(shù),2013,36(7):44?46.