TMS570處理器NHET功能的直流無刷電機測速設計

蔣文斌

(西安鐵路信號有限責任公司,西安710048)

引 言

在直流無刷電機(BLDC)控制系統中,對電機轉速的測量是一項重要且關鍵的問題。目前存在多種測速手段:利用編碼器測速、利用霍爾(HALL)信號測速、利用電機反向電動勢測速等等。其中,利用編碼器測速方法的優點可以達到高分辨率的要求,但需增加成本和體積;利用電機反向電動勢測速的優點是無需提供額外硬件接口,缺點是測速軟件算法復雜。本文介紹了一種利用HALL 信號、基于TMS570處理器NHET 功能的BLDC 測速軟件設計方案,此方案可實現速度測量精度和軟硬件復雜程度之間的平衡,同時在軟件設計過程中采用提高可靠性的算法確保速度測量的可靠和準確。

1 TMS570處理器及NHET功能簡介

TMS570系列處理器是TI公司推出的一種面向高性能交通運輸領域的安全MCU,該系列MCU 基于ARM Cortex-R4F內核架構,具有較高的性能并滿足IEC61508 SIL-3的安全要求,主要應用于汽車工業,如剎車防抱死系統(ABS)、電助力轉向(EPS)、HEV/EV 逆變器系統。

TMS570 系列處理器集成了第4 代高端定時器(NHET),NHET 使用高分辨率硬件通道并提供針對實時環境下的精確周期、脈沖測量功能、輸出比較功能、PWM 功能。NHET 采用獨立的指令結構和“時序決議循環”機制使時間分辨率達到ns級別,完全滿足各種高精度時間測量應用需要,其內部集成可編程的抑制濾波器,確保測量數據的可靠性要求。

2 BLDC測速硬件接口設計

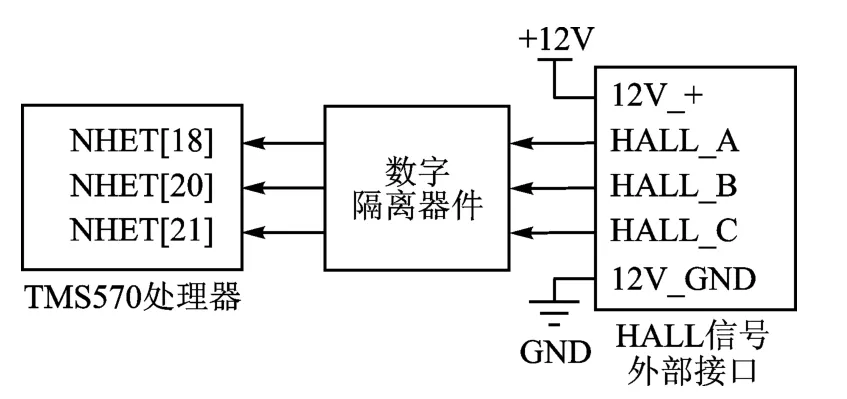

測速硬件結構示意圖如圖1 所示。BLDC 硬件測速接口設計較為簡單,將HALL信號進行數字隔離后,直接接入TMS570的NHET 引腳即可,將3個HALL信號同時引入NHET 進行測速是一種硬件冗余設計,其目的是提高BLDC 速度測量的可靠性,防止由于單通道HALL輸入信號失效導致整個測速功能無法完成的情況發生。

圖1 測速硬件結構示意圖

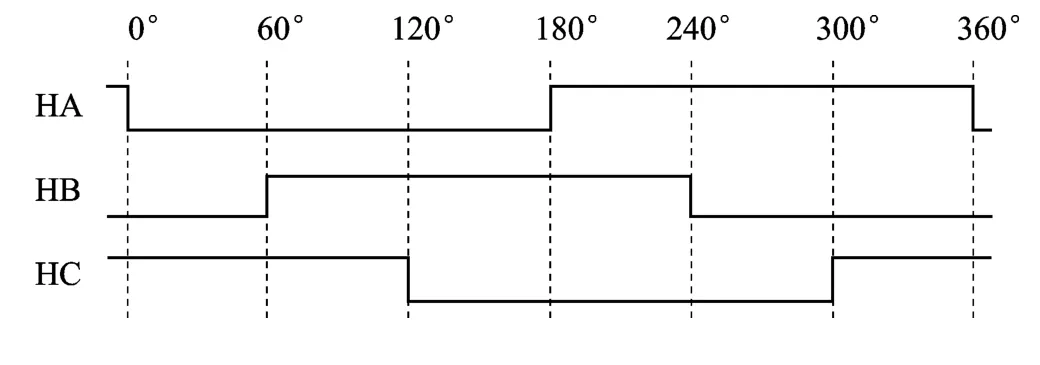

HALL信號輸入采用DC 12V 電平,經數字隔離后輸出DC 3.3V 電平,直接作為MCU 輸入。當BLDC轉動時,HALL信號的時序與相位關系如圖2所示。

圖2 BLDC順時針轉動HALL信號時序相位圖

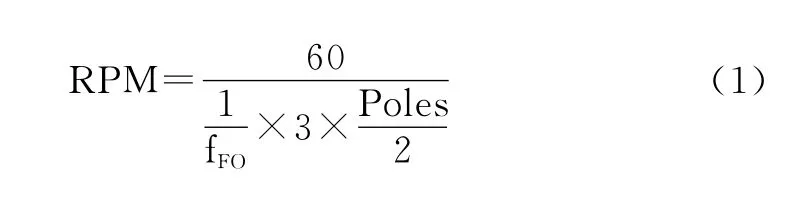

由圖2可知:BLDC轉速可通過測量單個HALL信號的頻率計算得出,BLDC 轉速(RPM,轉/分鐘)與HALL信號頻率(fFO,Hz)、BLDC 磁極對數(Poles)之間的關系式為:

3 NHET測速軟件設計

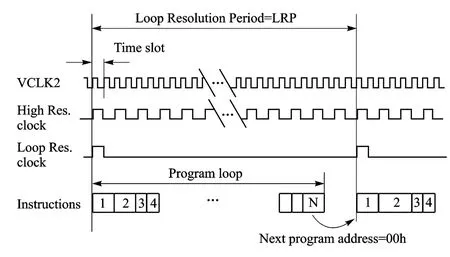

NHET 測速軟件的核心測速代碼采用獨立的指令結構和時序決議機制實現,NHET 采用精簡指令集(RISC)結構,包含22條指令,使用NHET 匯編器將指令代碼生成C語言結構的代碼,需在運行之前由應用程序拷貝到NHET RAM 中,NHET 匯編器同時生成.h文件,由應用程序對測量數據進行訪問,時序機制如圖3所示。

圖3 NHET指令執行時序圖

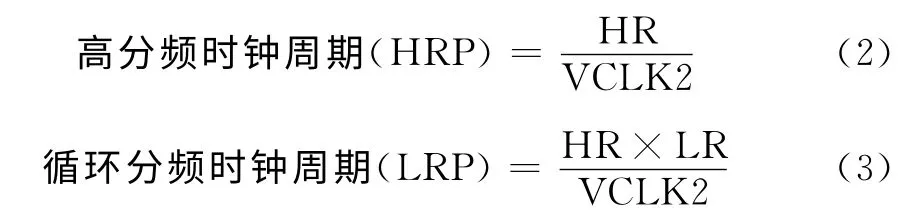

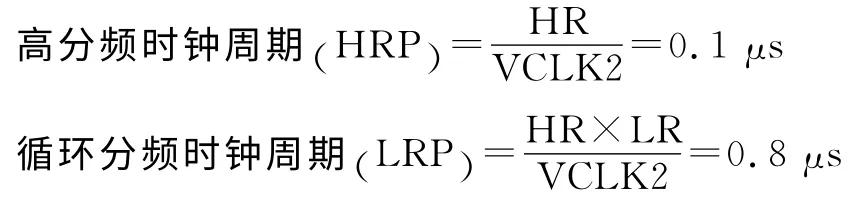

NHET 時鐘由VCLK2驅動,每個VCLK2周期稱為一個“時隙”(Time slot),將VCLK2 進行高分辨率分頻(High Res.clock)和循環分頻(Loop Res.clock)后得到高分頻時鐘、循環分頻時鐘,這兩個時鐘的周期為:

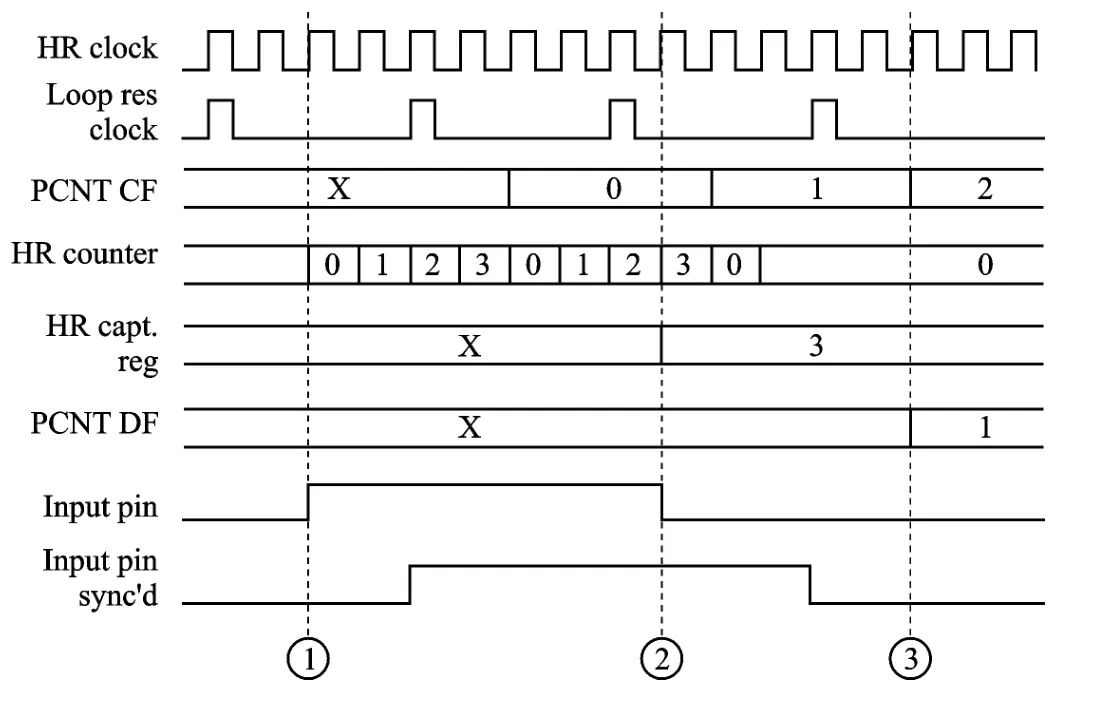

在此程序循環中包含1~N 條NHET 指令。由于不同的指令代碼執行時間不同,在設計時應注意程序循環內所有代碼執行時間的和不能超過一個循環分頻時鐘周期。由上文所述,利用BLDC的霍爾信號測量轉速,即測量霍爾信號的周期,使用NHET 指令集中的PCNT 指令實現,PCNT 指令捕捉NHET 輸入引腳信號的邊沿并使用高分辨率時鐘進行周期計數,將周期時間數據存儲在內部寄存器中供應用程序讀取,以PCNT 指令捕獲輸入脈沖信號時間為例,指令執行邏輯及時序如圖4所示。

圖4 PCNT指令邏輯及時序圖

圖4中①~③含義如下:

①當檢測到輸入引腳的上升沿后,HR 計數器開始由零進行加計數,當計數器滿后,向指令數據區加1,并從0重新開始計數;

②當檢測到輸入引腳的下降沿后,將HR 計數器內的數據存入捕獲寄存器(HR capt.reg);

③PCNT 指 令 在 同 步 輸 入 信 號(Input pin sync'd)由低變高后開始執行,在該信號由高變低后,得到數據區數據(lr_data)和捕獲寄存器內的數據(hr_data)之和即為脈沖時間。

HALL信號的周期為HALL輸入信號的上升沿到下降沿或下降沿到上升沿的時間,編寫PCNT指令參數如下:L01:PCNT{next=L02,irq=ON,type=RISE2RISE,pin=18};

L02:PCNT{next=L03,irq=ON,type=FALL2FALL,pin=20};

L03:PCNT{next=L01,irq=ON,type=RISE2RISE,pin=21};

其中每一條指令對應一個通道的HALL 輸入信號,當指定引腳(pin)測量到一個完整的HALL周期后,產生一個NHET 指令中斷(irq=ON),信號觸發的類型(type)包括上升沿到上升沿(RISE2RISE)和下降沿到下降沿(FALL2FALL)兩種,使用不同的信號觸發類型測量HALL信號周期的目的是通過簡單的軟件代碼異構保證測量結果的可靠性。

當VCLK2時鐘為70 MHz時,選取高分頻為7,循環分頻為8,可得

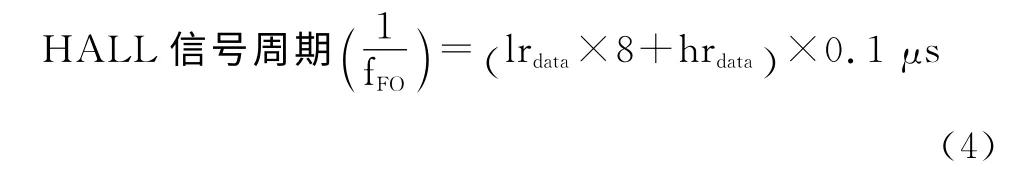

因此,經由NHET 測得的HALL信號周期為:

當選取BLDC磁極對數為10時,將(4)帶入式(1),得出BLDC轉速(RPM)與NHET 測量數據之間的關系式為:

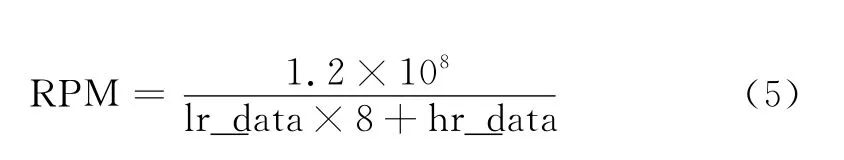

為防止HALL 信號因外界干擾產生的測量結果誤差,除了使用NHET 自身帶有的硬件抑制濾波器外,在軟件的設計過程中也應加入適當的濾波處理,保證測量結果的準確、可靠,使用一個系數為0.75的單極性I2R 低通濾波器的C語言代碼如下:

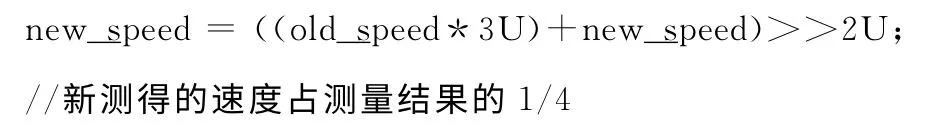

為提高測速軟件的可靠性,軟件采用結構容錯的設計思路進行設計,由于測速硬件采用3通道冗余采集HALL輸入信號,軟件采用N 版本程序設計方案。N 版本程序設計是指對于一個給定的功能,由N(N>2)個不同的設計組獨立編制出N 個不同的程序,然后通過運行N 個不同的程序得出結果并進行比較,輸出正確的數據。基于TMS570NHET 功能測速軟件N 版本程序設計基本結構如圖5所示。

圖5 測速軟件N版本程序設計基本結構

結 語

本文提出了一種基于TMS570系列處理器NHET 功能的直流無刷電機測速軟件設計方案,其中包括NHET測速原理介紹和代碼實現、對測量結果的軟件濾波算法設計、基于N 版本軟件容錯設計方法提高軟件可靠性。該測速方案已應用在采用TMS570LS20216處理器的自動門控制單元硬件之上,實際測試和應用的結果表明該方案切實可行。

[1]TI.TMS570LS Series Microcontroller Technical Reference Manual(TRM),2011.

[2]陸民燕.軟件可靠性工程[M].北京:國防工業出版社,2014.

[3]Rozanski,N.Woods.E.軟件系統架構:使用視點與視角與利益相關者合作[M].2版.侯伯微,譯.北京:機械工業出版社,2013.

[4]Len Bass,Paul Clements,Rick Kazman.軟件架構實踐[M].3版.北京:清華大學出版社,2013.

[5]EN 50126-Railway applications-The specification and demonstration of Reliability,Availability,Maintainability and Safety(RAMS),1999.

[6]EN 50218Railway applications-Communication,signalling and processing systems-Software for railway control and protection systems,2011.