嵌入式處理器基于SPI引導的RAM自檢探討

高傳發,孫振華,任華鋒(許繼電氣有限公司 技術中心,河南 許昌 461000)

嵌入式處理器基于SPI引導的RAM自檢探討

高傳發,孫振華,任華鋒

(許繼電氣有限公司 技術中心,河南 許昌 461000)

介紹了嵌入式處理器在使用基于SPI引導方式時,如何檢查DDR內存,以提高系統的可靠性。對系統的引導過程,包括片內ROM運行、片內RAM運行、DDR內存運行,進行了詳細的介紹。對各階段引導程序數據格式的處理進行細致的分析,并對生產實用化進行了實例驗證。

SPI引導;內存自檢;系統可靠性;引導過程

0 引言

隨著全球網絡進一步擴展到新終端設備和以前未連接的行業中,網絡安全對消費者、企業和其他機構變得越來越重要。人們越來越需要性能安全、價格便宜的裝置設備。為了降低成本,往往需要簡化電路設計。例如,采用SPI方式引導硬件,使用 SPI Flash作為存儲媒介,減少總線的布線,是簡化硬件電路的較好的方法[1]。但采用SPI方式引導硬件,需要將程序引導到DDR內存中,同時又需要對DDR內存進行檢查,這就出現了矛盾[2]。

1 基于SPI的硬件引導

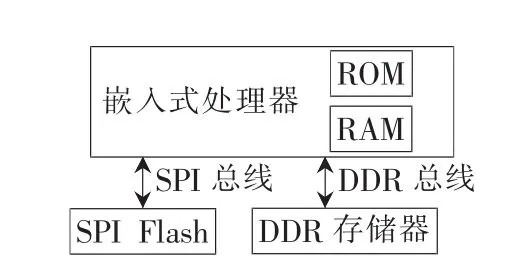

本文以一個實例,對嵌入式處理器基于SPI引導硬件時如何進行RAM檢查進行詳細的介紹。圖1是嵌入式處理器使用SPI引導的硬件框圖。在圖1中,硬件引導程序和系統程序放在 SPI Flash中,在上電引導后,系統程序會被搬移到DDR空間,在DDR空間運行起來。

圖1 使用SPI引導的硬件框圖

現在以U-Boot硬件引導程序為例,介紹以SPI引導模式引導系統硬件的情況。U-Boot是德國DENX小組的開發用于多種嵌入式CPU的 Bootloader程序,可以支持多種嵌入操作系統和多種處理器[3]。

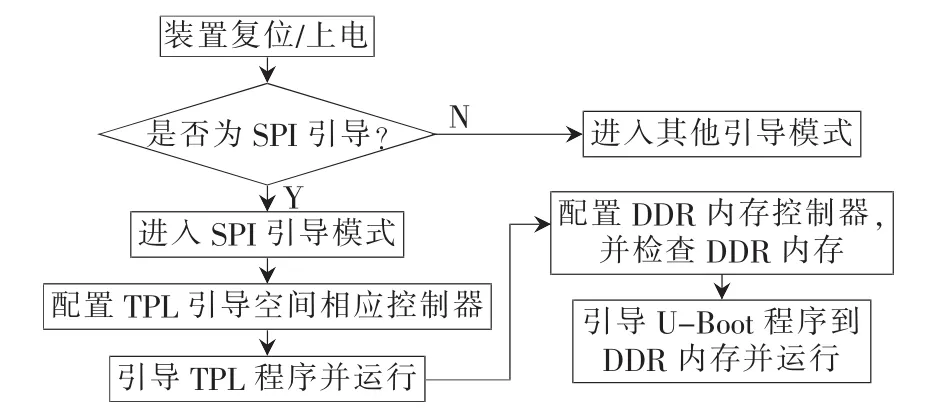

編譯的U-Boot程序,往往是運行在NOR Flash或DDR中的。但在基于SPI引導時,需要先從SPI Flash往片內RAM里運行一段程序,將DDR內存檢查一遍,然后再將U-Boot引導到DDR內存中去運行,如圖2所示。

2 SPI引導采用的數據格式

在TI公司的DSP及ARM處理器,飛思卡爾公司POWERPC及 ARM處理器,都支持基于 SPI的引導模式。在這些處理器的片內ROM都包含基本的SPI引導驅動程序。本文以飛思卡爾公司的QorIQ P1010處理器為例介紹其引導過程。P1010片內的SPI驅動程序能夠把SPI接口Flash中的程序拷貝到DDR內存或片內RAM中。不過,在拷貝之前,需要先對DDR控制器或片內RAM進行配置。這就需要定義一個特定的數據結構,完成引導程序所需要的環境配置。對于不同的處理器,生產廠家定義的引導數據結構是不同的。

圖2 SPI引導硬件程序框圖

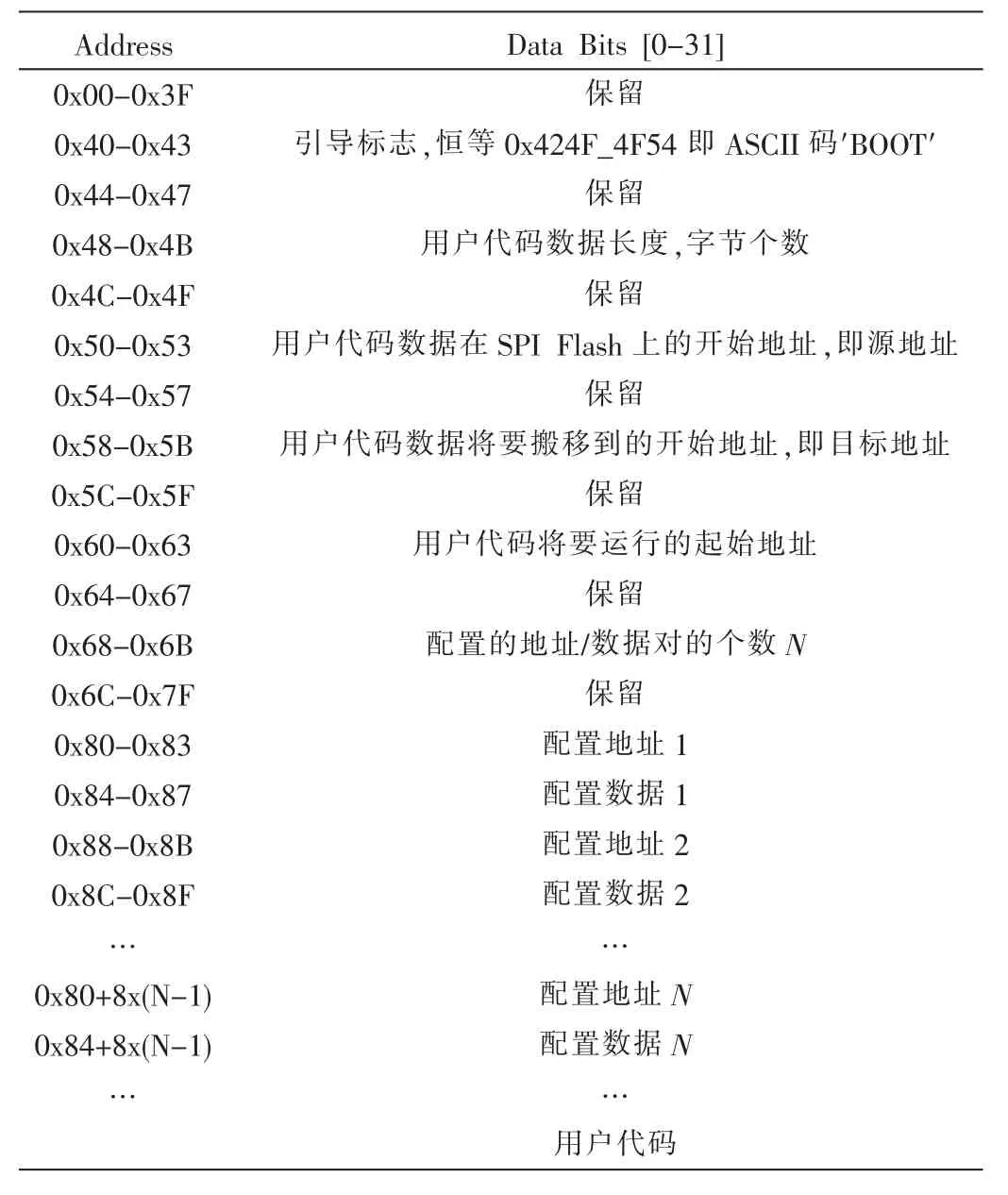

在P1010處理器完成復位序列后,通過選擇使用處理器片內ROM的SPI引導配置程序,而后處理器內核開始運行該片內ROM程序,配置SPI控制器,并與外部的SPI Flash通信,將程序拷貝出來并跳到指定的位置運行[4]。SPI引導采用的數據格式如表 1所示。

表1 SPI引導模式的數據結構

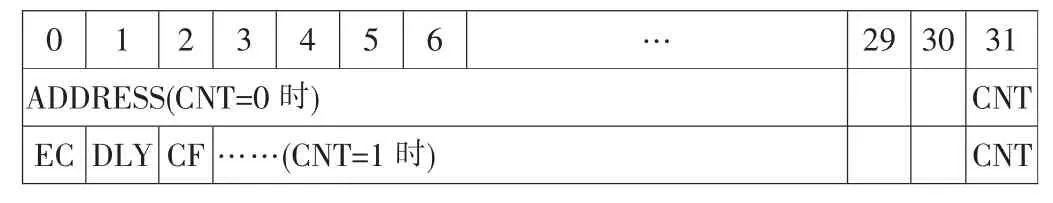

在表 1中,配置字(Control Words)由配置 32 bit地址/數據對組成,主要用在配置就地訪問窗口(LAW)和目標內存控制器的寄存器。配置地址域有兩種模式,當最低位為0時,配置地址域高30 bit代表的是地址,此時配置數據寫入此地址。當最低位為1時,配置地址域高30 bit代表的是指令,此時配置數據寫入此地址。這樣的結構讓用戶可以方便地配置4 B對齊的內存,完成控制指令操作,或定義程序配置階段的結束[5]。配置地址域的數據格式如表2所示。

表2 配置地址域的數據格式

在表 2中,當 CNT(最低位)=0時,則高 30 bit用作要寫入數據的地址,配置數據包含要寫入的數據。

當CNT=1時,則高30 bit用作控制指令。

當EC=1時,代表配置階段結束指令。

當DLY=1時,代表延時一定時間指令。

當CF=1時,代表更改SPI頻率的指令。

CNT表示地址模式與指令模式的切換。

當處理器內核開始拷貝程序時,先判斷0X40位置的標志是否正確,如果正確,先根據配置的地址/數據對的個數N來配置一些外圍寄存器,然后從0X50處指示的Flash地址搬移用戶代碼數據到0X58指示的地址。搬移完成后,從0X60指示的地址開始運行。將片內運行的這一段程序叫TPL程序。

3 片內RAM運行的TPL程序

P1010包含 256 KB的 L2CACHE,也可以當片內RAM使用。要檢查DDR內存,要先在片內RAM里運行一小段TPL程序。這一段程序是對基于DDR引導程序U-Boot的一個裁剪,主要完成內核的配置,初始化串口終端,初始化 DDR內存控制器,然后檢查 DDR內存[6]。在這里不需要設置U-Boot的環境變量,不需要配置以太網等其他的外圍器件。編譯后的TPL目標文件為uboot-tpl.bin。

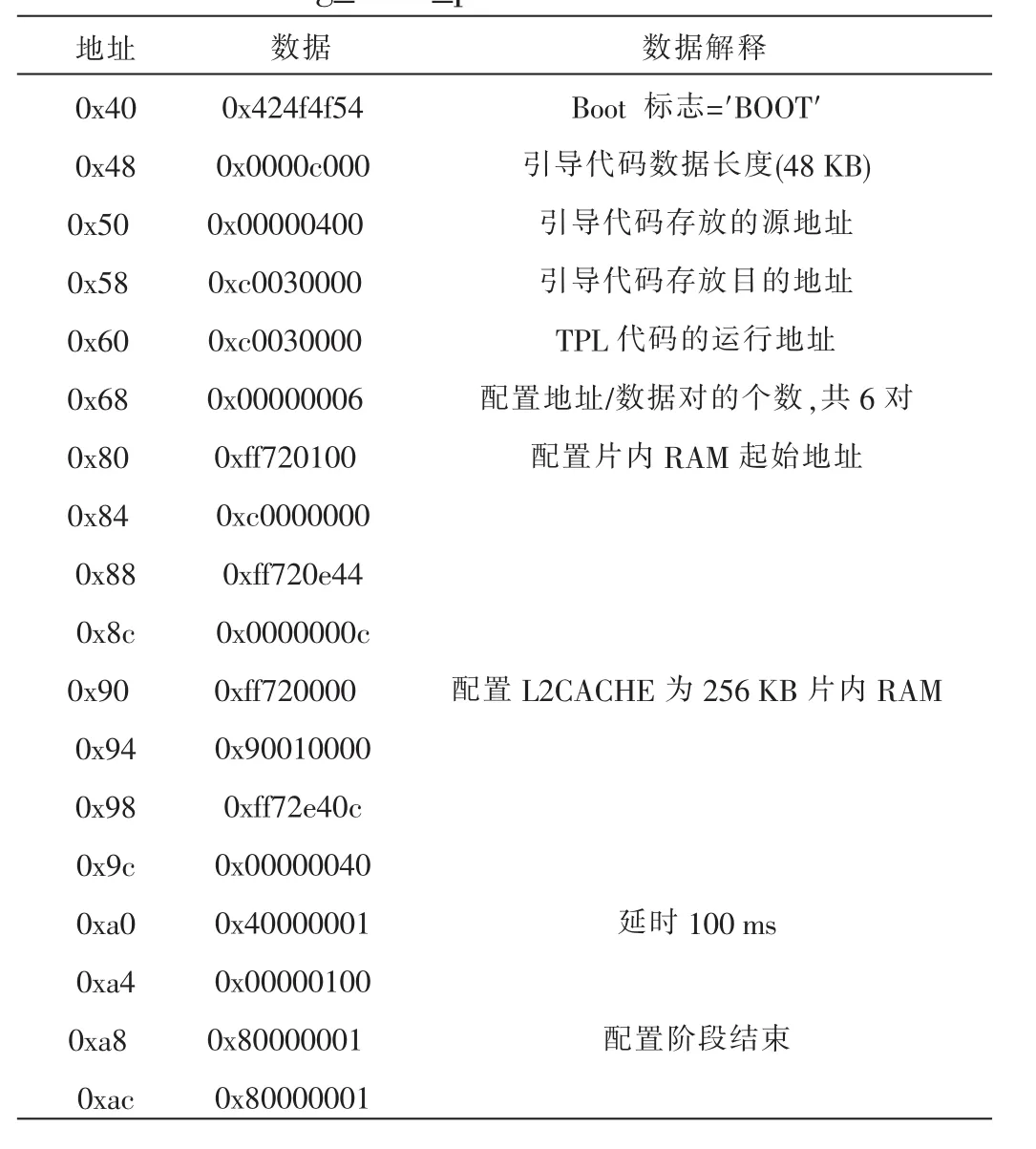

TPL程序的編譯按RAM引導的方式處理。程序的開始地址設為:0xc0030000~0xc0038800。現在需要對編譯后的uboot-tpl.bin進行格式處理,在其前面加上 SPI引導的可以識別的數據表頭,如表3所示。

表3是按照表1(SPI引導模式的數據結構)和表 2(配置地址域的數據格式)完成的一個SPI引導配置實例。在這個實例中,將L2CACHE設為片內RAM,開始地址設為0xc0000000。這一部分空間在處理器內核引導時已經通過TLB映射,可以直接使用。

對TPL進行數據格式化存放,要用到一個工具,即boot_format,它可以將基于HEX的文件和基于 BIN格式的文件合并到一起。這是一個飛思卡爾BSP里帶的數據格式化工具。采用以下命令:

合并后的文件為uboot_tpl_spi.bin。

表3 cfg_sram_p1010.dat數據格式

在 cfg_sram_p1010.dat文件里,TPL程序存放在 SPI Flash的0X400開始的地址。處理器先對片內RAM進行配置初始化,然后將TPL程序從0X400引導到0xc0030000開始的地址,并從0xc0030000開始運行。這時,處理器對DDR控制器進行配置,并對DDR空間進行自檢。

4 DDR的自檢及U-BOOT的運行

DDR RAM的自檢可以采用寫入特定數據(例如0x55,0xAA),然后回讀比較來檢查的方式;也可以通過檢查行列地址數據線來檢查。相關文檔很多,這里就不介紹了。

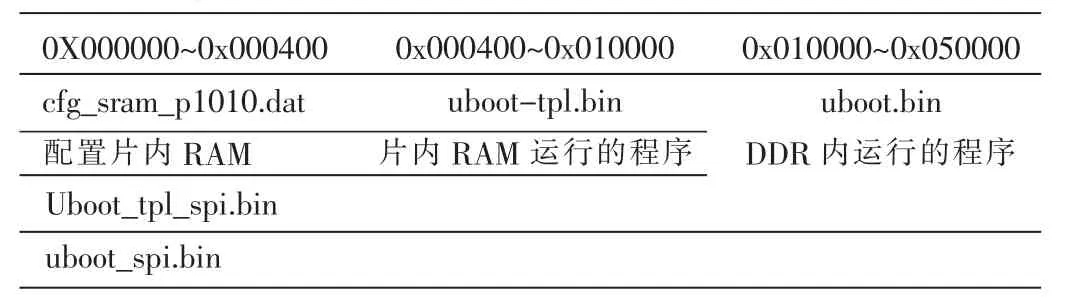

當檢查完DDR內存后,就可以引導并運行U-Boot程序了。U-Boot程序按RAM引導的方式編譯。程序起始地址設為0X11000000。編譯后的文件為uboot.bin。但在實際中需要將兩個單獨的BIN文件合并成一個文件,以方便生產和產品實用化。當uboot.bin與uboot_tpl_spi.bin合為的一個文件 uboot_spi.bin時,uboot_tpl_spi.bin放在前面,uboot.bin程序放在后面,如表4所示。

表4 產品實用化的文件數據格式

在表 4中,處理器在運行 TPL時,將 U-Boot從 SPI Flash的 0X10000地址引導到 DDR3的 0X11000000開始的地址(代碼數據總長度0x40000),而后跳運行入口地址(0X1103f000),運行 U-Boot程序。這時,整個硬件系統引導起來了。操作系統可以通過U-Boot運行起來。

5 結論

嵌入式處理器在使用SPI引導硬件時,先通過片內RAM運行一段程序,對DDR內存進行自檢,而后再將U-Boot程序及環境變量引導到 DDR空間[7],把硬件系統引導起來。通過實例化的應用,證明這在高性價比的嵌入式應用中是一個不錯的選擇,不僅能提高系統的可靠性,而且簡單易行。

[1]張偉棟,趙紅.基于 PowerPC8640處理器的通用處理模塊設計[J].微型機與應用,2015,34(6):32-34.

[2]李相國,楊樹元.基于PowerPC處理器SMP系統的UBoot移植[J].微計算機應用,2008,29(9):95-99.

[3]王齊.Linux PowerPC詳解:核心篇[M].北京:機械工業出版社,2007.

[4]李宗海,陳蜀宇,李海偉.嵌入式 Linux系統在 ARM平臺上的構建[J].計算機系統應用,2010,19(10):153-157.

[5]Freescale Semiconductor,Inc.Booting from On-Chip ROM(eSDHC or eSPI)[EB/OL].(2012-6-1)[2014-4-18].http://cache.freescale.com/files/32bit/doc/app_note/AN3659.pdf.

[6]鄧國榮,劉厚欽.基于 NOR Flash的 OMAPL138雙核系統自舉引導啟動實現[J].電子技術應用,2014,40(2):19-26.

[7]鄒洋,李琳皓,梁峰.Nucleus操作系統在 ARM11上的移植研究與實現[J].電子技術應用,2014,40(9):10-13.

RAM selfcheck about embedded processor based on SPI Boot

Gao Chuanfa,Sun Zhenhua,Ren Huafeng

(Tec.Center,XJEC,Xuchang 461000,China)

This paper introduces the embedded processor based on SPI Boot how to complete the RAM selfcheck,to improve the system reliability.All the system Boot process stages,including ROM-onchip running,RAM-onchip running and DDR memory running,are introduced im detail.The data format processing of all the Boot stages is analyzed in detail,and the practical utility of production is verified by instances.

SPI Boot;RAM selfcheck;system reliability;Boot process

TP307

A

1674-7720(2015)22-0083-03

高傳發,孫振華,任華鋒.嵌入式處理器基于SPI引導的RAM自檢探討[J].微型機與應用,2015,34(22):83-85.

2015-06-23)

高傳發(1972-),男,本科,高級工程師,主要研究方向:繼電保護及自動裝置產品研發。

孫振華(1983-),男,碩士,工程師,主要研究方向:變電站自動化研發。

任華鋒(1976-),男,本科,高級工程師,主要研究方向:變電站自動化研發。