基于MCP2515的CAN總線通信單元設計

丁雪靜+++許永輝

摘 要: CAN總線接口芯片MCP2515采用SPI接口,具有體積小、低功耗、功能完善、使用方便等特點。為了實現基于該接口芯片的CAN總線通信單元設計,采用DSP+FPGA架構,在FPGA內部實現SPI接口邏輯和MCP2515指令轉換邏輯,以完成不同的SPI指令,在DSP中接收上位機指令和完成對MCP2515的控制。實際測試結果表明,該通信單元設計合理,運行穩定,滿足了實際需求。

關鍵詞: CAN總線; MCP2515; SPI; DSP

中圖分類號: TN915?34 文獻標識碼: A 文章編號: 1004?373X(2015)21?0060?04

Design of CAN bus communication unit based on MCP2515

DING Xuejing, XU Yonghui

(Department of Automatic Test and Control, Harbin Institute of Technology, Harbin 150001, China)

Abstract: The CAN bus interface chip MCP2515 with SPI interface has the characteristics of small volume, low power consumption, perfect function and convenient use. To realize the design of CAN bus communication unit based on this interface chip, the DSP + FPGA framework is adopted in this design. The SPI interface logic and MCP2515 instruction transformation logic are achieved in FPGA to accomplish the different SPI commands. The upper computer instructions are received and the control to MCP2515 is finished in DSP. The practical test results show that the communication unit has reasonable design and stable operation, which meets the actual needs.

Keywords: CAN bus; MCP2515; SPI; DSP

CAN作為一種性能可靠的串行通信協議,主要應用于工業自動化、醫療設備和工業設備等方面領域。MCP2515[1]是一款獨立控制器局域網協議控制器,該控制器完全支持CAN V2.0B技術規范,通信速率最大為1 Mb/s,能夠發送和接收標準和擴展的數據幀及遠程幀等多種幀格式。同時擁有2個接收緩沖器,可優先存儲報文,6個29位驗收濾波寄存器,2個29位驗收屏蔽寄存器,3個發送緩沖器,具有優先級設定及發送終止功能,并且該器件具有體積小,采用低功耗CMOS技術等特點。基于MCP2515的功能特點,本文介紹了基于該控制器的CAN總線通信單元設計。

1 CAN通信單元總體設計

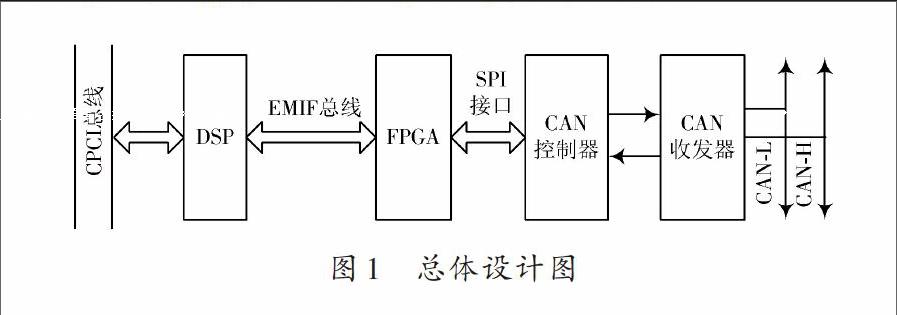

為實現CAN通信,并對其進行實時的程控,本模塊利用LabWindows/CVI作為上位機,設計用戶控制面板,進行不同CAN節點之間的數據交互以及波特率設置等。同時,采用DSP+FPGA架構進行CAN通信單元設計,MCP2515通過SPI接口與FPGA進行連接,并在FPGA內部進行SPI接口邏輯和指令轉換邏輯設計,在DSP中接收上位機命令和對MCP2515的控制。在電路設計時,利用TJA1050作為高速CAN收發器,由此,完成CAN總線通信單元的整體設計,如圖1所示。

2 CAN通信單元硬件設計

根據CAN通信原理[2],設計了硬件電路圖。在電路設計中,采用由無源陶瓷振蕩器、起振電容、反饋電阻等構成皮爾斯(Pierce)式振蕩電路,晶振頻率取16 MHz,與此對應的起振電容的推薦值為22 pF。采用TJA1050作為CAN收發器[3],該器件采用了SOI技術可以有效降低電磁輻射,并且具有瞬態保護和熱保護功能,具有較強的抗電磁干擾能力。考慮到該通信單元工作場合的電磁環境惡劣,同時可能存在潛在的共模電壓干擾,因此在CAN控制器和收發器增加了信號隔離電路,此外,對CAN收發器的供電電壓也做了隔離處理。

CAN通信接收通道和發送通道分別采用HCPL0631和HCPL063L高速光耦隔離器進行信號隔離,消除CAN總線節點之間的電磁干擾。本設計采用Altium Designer Winter 09進行原理圖設計和PCB設計。

2.1 CAN控制器MCP2515

MCP2515是一款獨立的CAN控制器,該器件由3部分構成:CAN通信協議模塊;CAN通信控制邏輯模塊;SPI接口協議模塊。下面分別對3個部分進行簡單的介紹。

(1) CAN通信協議模塊:該模塊主要用于CAN總線報文的接收和發送。在報文發送時,先將報文載入報文緩沖器和控制寄存器中,MCU通過SPI接口設置控制寄存器中的數據幀格式位、數據長度位等內容完成CAN數據幀發送設置,使用發送使能引腳啟動報文發送。在報文接收時,MCU通過SPI接口讀取CAN通信協議模塊寄存器組中的通信狀態信息和報文濾波信息,確定CAN總線是否有報文和報文是否送入接收緩沖器中。

(2) CAN通信控制邏輯模塊:通過與其他模塊連接,進而控制MCP2515的設置和運行,以便傳輸信息與控制。

(3) SPI接口協議模塊:MCU通過SPI接口與MCP2515實現數據傳輸,使用標準的SPI讀/寫指令以及MCP2515的SPI數據通信協議實現對芯片寄存器的讀/寫。CAN通信的所有指令和數據均通過SPI接口進行傳輸,指令包含該芯片的復位指令、讀指令、寫指令、讀RX緩沖器指令、裝載TX緩沖器指令以及位修改指令。通過以上指令實現MCP2515的初始化、數據發送以及數據接收等功能。

2.2 CAN收發器TJA1050

本設計采用NXP公司的TJA1050芯片[4]作為CAN收發器。作為CAN控制器和CAN總線之間的物理接口,既可以將CAN控制器輸出信號TXCAN轉換為差分信號對發(CANH和CANL)送至總線上,也可以將CAN總線上的差分信號對轉換成CAN控制器信號RXCAN。TJA1050最高傳輸速率為1 Mb/s,并具有靜音模式,在發送禁止時,不會對總線上其他節點帶來影響,并且具有較高的抗電磁干擾能力。

3 CAN通信單元邏輯設計

本設計采用Altera公司的Cyclone Ⅲ系列的EP3C55 FPGA進行通信單元控制邏輯設計[5?6]。通過DSP的EMIF接口,將相應控制信號和DSP數據寫入FPGA,并通過地址線進行譯碼。當譯碼信號cs_daL有效時,鎖存至寄存器buf的低16位;當cs_daH有效時,鎖存至寄存器buf的高16位;當cs_num有效時,鎖存串行數據位數;當cs_RD有效時,并且DSP控制信號OE同時有效時,將接收FIFO中的值送至DSP的數據線上。該通信邏輯單元同時包含指令解析模塊,該模塊對鎖存的32位數據和指令長度進行判斷,若長度為8,則為復位指令,只將buf[7:0]該 8位數據依次送給send信號;若長度為24,并且buf[16]等于1,則為讀指令,只將buf[23:8]該16位發送至send信號,并在后8個SCK信號之后,將SO信號鎖存至接收寄存器,進而存入接收FIFO中;如果buf[16]等于0,則為寫指令,將buf[23:0]該24位數據送給send信號;若長度為32,則為位修改指令,將buf[31:0]所有的32位信號均送至send信號。SPI邏輯模塊將指令、相應寄存器地址和數據輸出至外部電路MCP2515器件的相應引腳,根據SPI時序圖進行時序設計,當CS信號為低電平并且SCK有效時,將指令、MCP2515內部寄存器地址、需要發送的數據通過SI引腳依次串行輸出,并將CAN總線上的數據發送至MCP2515中的緩存寄存器,通過SO引腳輸送至FPGA的接收FIFO中,邏輯設計如圖2所示。

4 CAN通信單元程序設計

4.1 DSP軟件設計

軟件部分采用CCStudio v3.3進行編程設計,對于CAN通信模塊軟件設計分為3個基本部分:MCP2515的初始化設置、數據的發送和數據的接收。這3部分是CAN通信控制邏輯的基本內容,通過以上3部分可以實現CAN總線的數據發送和讀取。下面對這3個部分進行簡單的介紹。

4.1.1 MCP2515初始化

MCP2515在運行之前需進行初始化,在初始化之前必須進行MCP2515復位設置,以便于將MCP2515內部寄存器恢復到默認值。由于只有在配置模式下,才能夠對MC2515進行初始化,故需將MCP2515設置在配置模式下,在進入模式的配置之后,正式進入初始化設置,其中初始化主要包含波特率設置、中斷寄存器設置、驗收屏蔽寄存器設置、驗收濾波寄存器設置。在完成以上功能設置后,還需將MCP2515設置為正常模式,在正常模式下,方可進行正常的數據接收和發送。圖3為MCP2515初始化流程。

4.1.2 MCP2515數據發送

在進行數據發送時,只需要按照特定的幀格式將數據進行組合,并送入MCP2515發送緩沖區,并根據設定的優先級,啟動發送命令即可。本設計利用SPI寫命令寫寄存器啟動發送。同時對于報文發送是否成功進行判斷,如果發送成功,將TxBnCTRL.TXREQ位進行清零,否則判斷報文發送失敗是由于報文出錯還是仲裁失敗引起的。圖4即為報文發送流程圖。

4.1.3 MCP2515數據接收

圖5為報文接收流程圖。在進行數據接收時,首先進行起始幀檢測,在檢測到起始幀的情況下,將報文載入報文集成緩沖器(MAB)中,之后判斷收到的報文是否有效。如果報文無效,即產生錯位幀,否則繼續判斷報文是否符合接收緩沖器RXB0條件或者接收緩沖器RXB1條件。當符合接收緩沖器條件時,判斷相應的緩沖器是否為空以及是否可以接收新的報文,對于緩沖器RXB0可設置滾存模式,即當RXB0數據存滿時,如果繼續接收新的報文,可將其滾存至RXB1中,當RXB0或RXB1接收報文時,將產生中斷,置相應緩沖中的滿中斷標志位CANINTE.RXxIF為1,并通過設置RXBxCTRL.FLIGHT位使能報文接收的驗收濾波寄存器編號。之后使能相應的緩沖器中斷,最后判斷是否打開中斷。

4.2 上位機軟件設計

上位機軟件設計包含底層驅動程序設計和上位機應用軟件設計,底層驅動程序用于實現對硬件控制,該程序利用VISA中的Driver Studio進行開發。在底層硬件的支持下,采用LabWindows/CVI進行用戶界面設計。通過上位機軟件可以方便用戶實時對CAN總線通信進行控制,并且對數據幀、擴展幀格式、波特率等參數進行配置。圖5為CAN通信模塊測試軟面板。其中分為3部分:通信配置、數據發送和數據接收。其中通信配置包含通道選擇、波特率設置、數據位數選擇、幀格式選擇、ID設置、驗證屏蔽寄存器設置、驗證濾波寄存器設置;發送數據區可設置發送字節數,發送何種形式的報文設定,其中可發送特定報文、廣播報文和遠程報文等特殊報文;接收數據區用于接收CAN總線上的其他CAN節點發送來的報文,并且完成一次接收后,需清空接收數據區。同時,在進行CAN通信配置設定之前需進行MCP2515初始化設置。模塊初始化即將所有通信配置進行初始化,使模塊進入初始化狀態。圖6為上位機軟件界面。

5 測試結果

為了驗證CAN通信單元設計的正確性,即硬件電路設計無誤,FPGA邏輯設計正確、DSP程序正確運行、驅動程序設計正確,以及上位機軟件設計正確等方面。本設計采用周立功ZLG CANTest進行驗證,經過100 000次循環測試,數據傳輸正確無誤,表明該通信單元能夠在設定的波特率下進行多種形式的報文發送和接收,圖7即為測試結果。該結果表明,設計正確和CAN通信單元運行正常。

6 結 語

本文介紹了一種基于MCP2515的CAN總線通信單元設計方法。在硬件設計方面,利用MCP2515和TJA1050實現信號形式轉換,采用FPGA+DSP架構,進行上位機命令接收和CAN通信邏輯設計,并實現SPI指令和數據解析。在軟件設計方面,提供了幀格式和遠程報文/廣播報文/特定報文設置,以及對數據位和報文進行濾波、屏蔽功能設置。通過以上設置,可進行多種報文發送。測試證明,該通信單元可進行正常的報文接收和發送,通信可靠、運行穩定、符合技術要求。

參考文獻

[1] Microchip Technology Inc. MCP2515 datasheet [R]. US: Microchip Technology Inc., 2005.

[2] 饒運濤,鄒繼軍,鄭勇蕓.現場總線CAN原理與應用技術[M].北京:北京航空航天大學出版社,2006.

[3] 侯明,杜弈.基于CAN總線的接口電路設計[J].通信技術,2008,41(7):138?140.

[4] Philips. TJA1050 datasheet [R]. Netherland: Philips, 1999.

[5] 王躍飛,侯亮,劉菲.基于FPGA的CAN網絡實時管理系統設計[J].電子測量與儀器學報,2013,27(8):721?728.

[6] 李亞峰.基于Verilog HDL設計CAN控制器[D].北京:北京交通大學,2007.