晶振電路的原理及匹配方法

孔進亮

(珠海格力電器股份有限公司 廣東珠海 519070)

振蕩電路是單片機系統的“脈搏”,為單片機系統提供準確的時基。如果振蕩電路工作頻率出現偏差,會導致計時不準,甚至通訊不能同步(特別是高速通訊)。振蕩電路在單片機系統中起著至關重要的作用,本文將以晶振電路為例,介紹晶振電路的原理及其匹配方法。

1 晶振電路原理

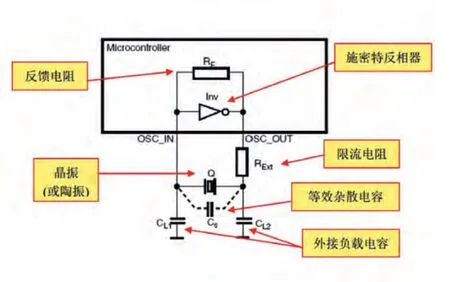

我們在單片機上使用的晶振電路(圖1)稱為作皮爾斯(Pierce)振蕩器[1]。

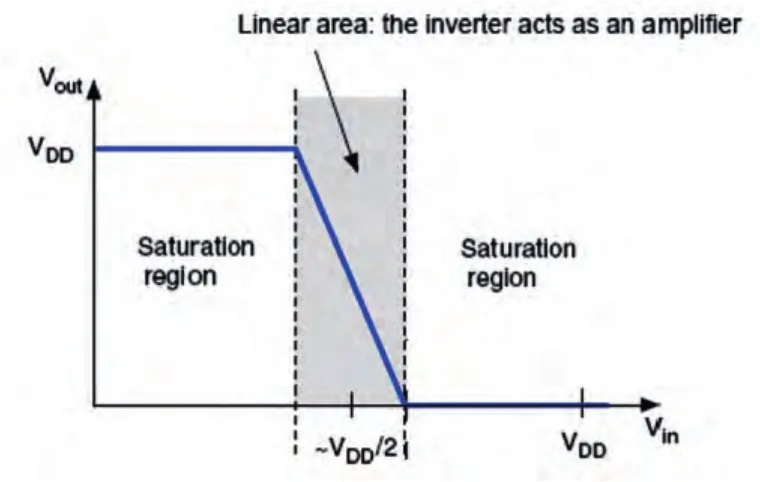

我們知道振蕩電路主要由決定振蕩頻率的選頻網絡和維持振蕩的正反饋放大器組成,該電路將直流電源能量轉換為一定波形的交變振蕩信號。在單片機內部,反相器作為為主動元件,對輸入信號進行反相和放大,晶振及其負載電容(包括CL1、CL2、CS等)組成了反饋網絡。由于反向器的線性區域很窄,容易出現抖動,故此加入RF引入直流負反饋,迫使反向器工作在線性區域(圖2)。這時,工作在線性區的反向器就等同于反向放大器了。RF并為反向器提供直流偏置,使電路更靈敏。

反饋振蕩電路正常工作必須滿足三個條件:起振條件(保證接通電源后能逐步建立起振蕩),平衡條件(保證進入維持等幅持續振蕩的平衡狀態)和穩定條件(保證平衡狀態不因外界不穩定因素影響而受到破壞)。

要達到振蕩狀態,振蕩電路幅值和相位均需要滿足一定的條件,稱巴克豪林(Barkhausen)判據[1]:

A(f)=|A(f)|×ejfα(f)

B(f)=|B(f)|×ejfβ(f)

︱A(f)?B(f)︱≥1

α(f)+β(f)=2nπ(n=0,1,2…)

其中:A(f)是放大器部分,給這個閉環系統提供能量以保持其振蕩;B(f)是反饋通道,決定了振蕩電路的頻率。

振蕩電路的閉環增益應大于1,并且相移為2nπ。即振蕩電路要保證處于正反饋狀態。

(1)起振

剛接通電源時,電路中存在各種電擾動,但只有頻率為諧振角頻率的分量才能通過選頻網絡產生較大的反饋電壓。通過主動元件的放大和反饋,振蕩電壓振幅不斷增大(正反饋)。在起振過程中,直流電源補充的能量要大于整個環路消耗的能量。

(2)平衡過程與平衡條件

因為放大器線性放大的范圍是有限的,隨著輸出振幅增大,放大器將由放大區進入飽和區或截止區,其放大能力逐漸下降。當放大器增益下降而導致閉環增益下降到1時,振幅的增長過程將停止,振蕩電路達到平衡,進入等幅振蕩狀態。此時,直流電源補充的能量剛好抵消整個環路消耗的能量。既電路達到振蕩平衡時,振蕩電路處于放大倍數為1的正反饋狀態,即:

圖1 單片機晶振電路

圖2 反向器工作示意圖[1]

︱A(f)?B(f)︱=1

α(f)+β(f)=2nπ(n=0,1,2…)

(3)平衡狀態的穩定性和穩定條件

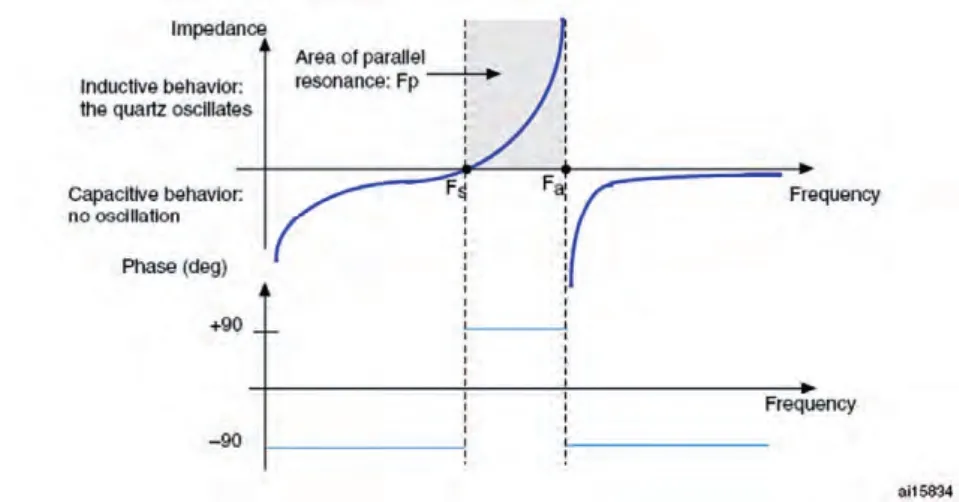

振蕩電路在工作過程中,不可避免地要受到各種外界因素變化的影響,如電源電壓波動、溫度變化、噪聲干擾等。要使振幅穩定,振蕩器在其平衡點必須具有阻止振幅變化的能力。保證相位穩定,要求振蕩器的相頻特性在振蕩頻率點應具有阻止相位變化的能力。石英晶體頻域特性可以滿足以上要求(圖4),其參數具有高度的穩定性,所以其組成的振蕩電路具有穩定的振蕩頻率。

2 晶振電路的參數計算

2.1 晶振頻率計算

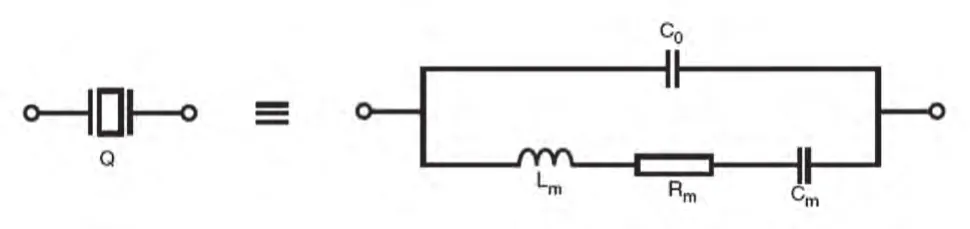

石英晶體是常用的振蕩電路元件。它可用圖3所示模型表示。

C0:等效并接的電容(注:也叫并電容、靜電電容,其值一般僅與晶振的尺寸有關)。

Lm:(動態等效電感)代表晶振機械振動的慣性。

Cm:(動態等效電容)代表晶振的彈性。

Rm:(動態等效電阻)代表對電路的損耗。

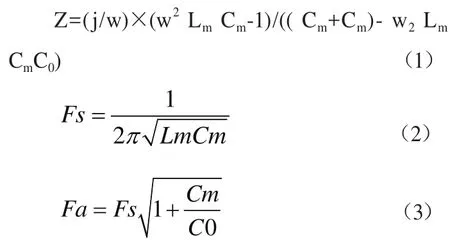

晶振的阻抗可表示為以下方程(Rm忽略不計):

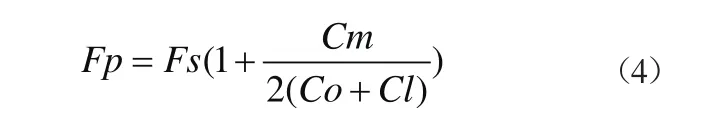

Fs的是當電抗Z=0時的串聯諧頻率(注:Lm、Cm和Rm支路的諧振頻率);Fa是當電抗Z趨于無窮大時的并聯諧振頻率(注:整個等效電路的諧振頻率);Fs到Fa之間的區域即“并聯諧振區”(圖4中的陰影部分),該區域是晶振電路的正常工作區域。在此區域晶振呈電感特性,在電路中產生180°的相移(與反向器的180°相移疊加,產生360°的相移,而符合正反饋的相位)。其頻率FP(又稱FL,負載頻率)表達式如下:

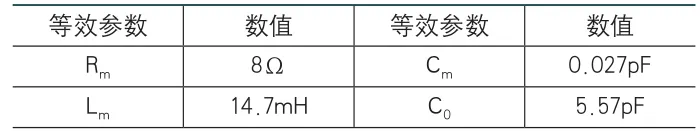

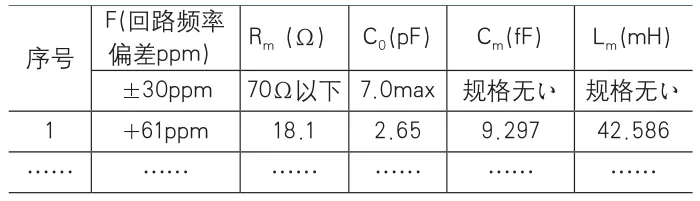

從公式(4)可知,可以通過調節負載電容CL來微調振蕩器的頻率,故此晶振制造商在規格書中會給出外部負載電容CL的值。調整CL值,可以使晶振晶體振蕩時達到其標稱頻率。以8MHz晶振參數為例(如表1),通過表達式(2)、(3)和(4),我們可以計算出該晶振的Fs、Fa、FP:

Fs=7988768Hz,Fa=8008102Hz;如果該晶振的CL為10pF,則其振蕩頻率為:FP=7995695Hz。

要使其達到準確的標稱振蕩頻率8MHz,則CL應該為4.02pF。

圖3 石英晶體模型[1]

圖4 石英晶振的頻域電抗特性[1]

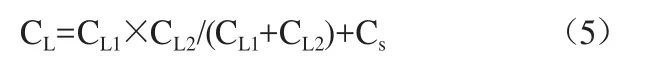

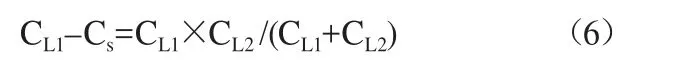

2.2 負載電容CL計算

CL值取決于外部電容器CL1和CL2,和電路板上的雜散電容Cs。外部電容器CL1和CL2可用來調整CL,使之達到晶振制造商的標稱值。但雜散電容Cs與芯片的引腳、焊盤、封裝引腳、印刷電路板等均有關系,無法計算,一般按5pF估算。

CL的公式如下:

例如,如果CL=15pF,假設Cs= 5pF,根據公式(6)計算得CL1=CL2= 20pF ;

圖5 使用感應探頭測量頻率

圖6 負性阻抗測量和計算

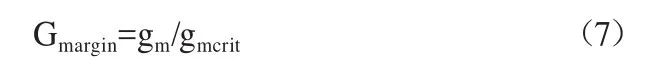

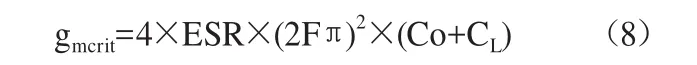

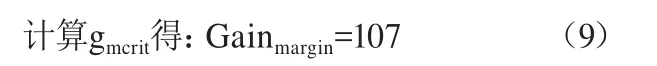

2.3 增益裕量計算

振蕩電路的增益裕量決定了振蕩電路是否能夠正常起振:

(注:margin,即裕量)

gm:主動元件(單片機內部的反向器)的跨導,此參數取決于單片機內部電路。

gmcrit(注:gmcrit,即gm critical):取決于晶振的參數。

若CL1=CL2、晶振的CL將與制造商給定的值相同,則gmcrit的計算公式:

ESR:晶振的等效串聯電阻

基于振蕩電路設計的理論[1],單片機內部反向器的跨導(gm)必須滿足:gm>gmcrit。而為保證可靠的起振,gm應達到gmcrit的5倍以上,即gainmargin最小值一般設為5。

例如,有如下參數的石英晶體,并且已知微控制器的振蕩器部分gm等于25mA/V。

石英晶體參數:頻率=8MHz,C0=7pF,CL=10pF,ESR=80Ω。

由于107>>5,因此晶振將正常起振。

如果不能滿足增益裕量起振條件(即增益裕量Gainmargin小于5,晶振將無法正常起振),應嘗試使用ESR較低或CL較低的晶振。

2.4 驅動功率DL及外部限流電阻RExt計算

晶振的功耗必須限制在某一范圍內,超過這個值時,晶振會受到損害,出現電極劣化、頻偏、壽命衰減。

驅動級別計算公式:

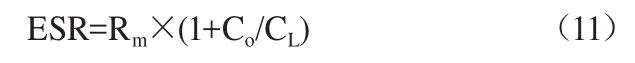

其中,ESR是指晶振的等效串聯電阻:

IQ是流過晶振電流的均方根有效值,使用示波器可觀測到其波形為正弦波。電流值可使用峰-峰值(IPP)。

可以調節外部限流電阻,使流過晶振的電流不超過IQMAX均方根有效值。

IQMAX均方根有效值表達式如下:

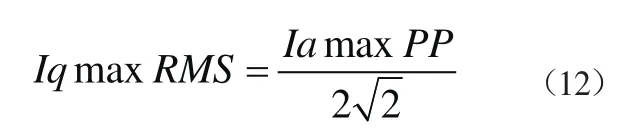

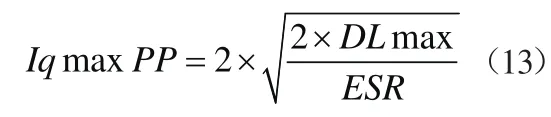

流過晶振的電流IPP不應超過IQMAXPP(使用峰-峰值表示),IQMAXPP表達式如下:

當IQ超過IQmaxPP時,必需要增加RExt,并且將RExt加入到ESR中重新計算IQmax。

2.5 外部電阻RExt計算

圖7 在晶振引腳(XOUT端)上串入可調電阻VR

圖8 使用小電流探頭測試晶振電流

RExt的作用是限制晶振的驅動功率,并且它與CL2組成一個低通濾波器,以確保振蕩器的起振點在基頻上,從而避免3次、5次、7次諧波頻率。如果晶振的功耗超過額定值,則外部電阻RExt是必需的;如果晶振的功耗小于額定值,RExt可取0Ω。

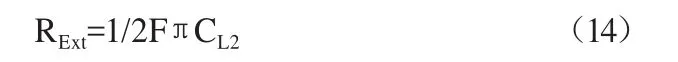

RExt值計算如下:

表1 8MHz晶振參數

表2 晶振在電路板中的頻率偏差

輸入條件:振蕩器頻率F=8MHz;CL2= 15pF

得到:RExt= 1326Ω

如果RExt值太小,晶振上可能會承擔太多的功耗。如果RExt值太大,振蕩器起振條件不滿足從而無法正常工作。計算完RExt值后要重新計算Gain margin的值,以確保RExt值對起振條件沒有影響。例如,RExt值的值需要加入到ESR中參與gmcrit的計算,同時要保證:

2.6 啟動時間

啟動時間是指振蕩器啟動并達到穩定所需的時間。這個時間受外部CL1和CL2電容影響,同時它隨著晶振頻率的增加而減少。不同種類的晶振對啟動時間影響也很大。頻率為MHz級的晶振的啟動時間是毫秒級的。32kHz的晶振的啟動時間一般要1~5秒。

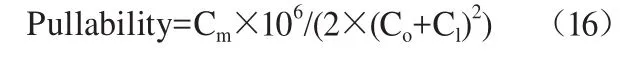

2.7 牽引度(Pullability)

晶振的牽引度(也叫可調度)是指工作在正常并聯諧振區的晶振頻率的變化率。這也用于衡量隨負載電容變化而導致的頻率變化,負載電容的減少會導致頻率的增加,反之負載電容的增加會導致頻率的減小。晶振的牽引度表達式如下:

3 晶振電路的評估及實際測試

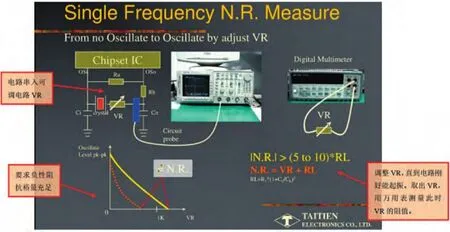

從公式(5)和公式(7)發現,CS參數一般只能估算,gm是單片機內部電路的參數,廠家沒有公開,通常難以計算。我們需要用其他方法對電路進行評估。

在正反饋的振蕩電路中,我們將消耗能量的電路部分等效為負載,而提供能量的主動元件(放大器)部分,等效為源負阻器件,產生“負電阻”。

振蕩電路的起振條件為負阻絕對值大于正阻。振蕩穩定后負阻絕對值等于內阻。因此負性阻抗是一個衡量振蕩電路穩定性很重要的參數。而對晶振電路的增益裕量的評估轉換為對負性阻抗的測量。

對晶振電路的參數評估測試如下:

3.1 頻率測量

(1)晶振的單體參數測試,可以使用晶振參數測試儀;

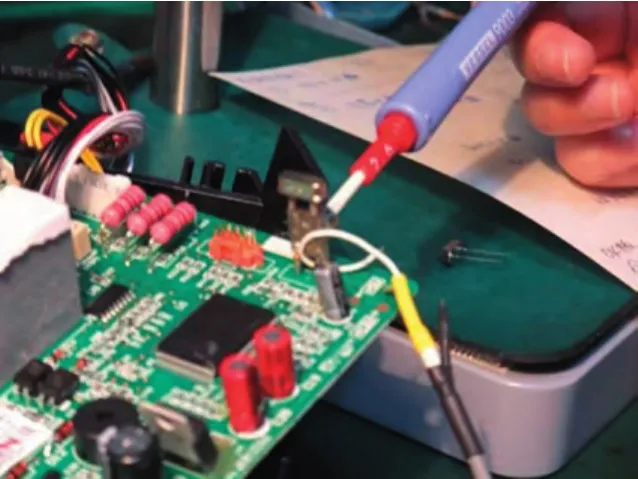

(2)晶振電路頻率實測:通過頻譜儀和數字頻率計實測晶振在電路中的頻率(圖5);

(3)算出晶振在電路板中的頻率偏差△f/f0(表2)。

根據不同的應用場合,一般要求頻率偏差為±30ppm~±50ppm不等;如果是實時鐘(RTC)的應用,則要求達到0ppm~10ppm。以實時鐘為例,起使用的是32.768kHz晶振,在實際電路存在10ppm的偏差,每天產生誤差達到0.864秒。可見振蕩電路中的頻率偏差對時間精度有影響。

3.2 負性阻抗測量

負性阻抗(-R),前面已有介紹,其測量方法如下:

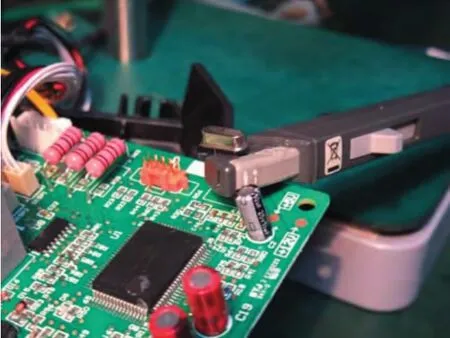

(1)晶振電路中串入可調電阻VR,不斷增大VR直到晶振停止振蕩。重新調節VR,直到電路剛好能起振。取出VR,用萬用表測量此時VR的阻值。如圖6、7。

(2)計算負性阻抗:N.R.= VR+RL。要求│N.R.│> (5~10)×RL(注:RL即晶振的ESR,見公式(11))

3.3 驅動功率測量

按圖7在晶振引腳上串入電流探頭,測量流過晶振的電流值,按2.4、2.5(公式(10)~(14))計算驅動功率和限流電阻。

3.4 晶振波形測試及啟動時間測試

一般的示波器探頭附加電容達到8~15pF,對于晶振電路來說,引入的附加電容太大,已經影響電路的工作。故此對晶振波形測試需要使用主動式FET探頭,探頭附加電容小于1pF,測試時可以減少對晶振電路的影響。根據測試的波形評估實際測試波形是否出現削頂、削底、振幅不足、振蕩不穩定等異常情況。

3.5 晶振電路參數調整

當前述1~4項測試出的參數出現異常時,則需要對電路參數進行調整。

4 結束語

單片機系統中,晶振電路的可靠性、穩定性和準確性,對系統運行有著重要的影響。在對時間精度要求很高的應用中,晶體電路的匹配性能測試和調整是必不可少的環節。希望通過本文使大家的對晶振電路有更深刻的理解,電路設計水平進一步提升。

[1] ST,AN2867應用文檔《ST微控制器振蕩器電路設計指南》,2009

[2] 沈偉慈,《通信電路》(第二版),西安:西安電子科技大學出版社,2007

[3] [日]稻葉保,《振蕩電路的設計與應用》,北京:科學出版社,2004

[4] HOLTEK,HA0075s《Holtek單片機復位電路和振蕩電路應用》

[5] HOLTEK,HA0301T《HT32系列微控制器晶振& ADC設計的注意事項及PCB 布局指南》

[6] Microchip,01155a_cn《Microchip時鐘晶振的實時校準》

[7] Seraphim,《石英晶體振蕩電路之回路分析介紹》

[8] 趙毅強,楊棟,《低功耗低頻快速起振電路的設計》,北京工業大學學報,2012

[9] 劉懲,李冰,《用于時鐘芯片的Pierce晶體振蕩器設計》,半導體技術第33卷第1期,2008

[10] 羅一平,《三點式振蕩器中負阻特性和反饋特性的等價性》,浙江師大學報(自然科學版)第19卷第2期,1996