OMAP-L138 DSP與FPGA通信方案設計

張偉文,高偉強,林 淦,劉建群,閻秋生

(廣東工業大學機電工程學院,廣東廣州 510006)

OMAP-L138 DSP與FPGA通信方案設計

張偉文,高偉強,林 淦,劉建群,閻秋生

(廣東工業大學機電工程學院,廣東廣州 510006)

針對雙刀頭高性能柔性材料切割數控系統,結合OMAP-L138+FPGA控制系統的數據傳送需求以及平臺資源,提出一種OMAP-L138的DSP通過EMIFA接口與FPGA的FIFO進行數據通信的設計方案,DSP將處理后的數據通過EMIFA接口傳送到FPGA的異步緩存FIFO模塊。FIFO在接收DSP發送的高速數據的同時,將緩存的數據輸出。通過邏輯分析儀實驗測試驗證,該方案能夠實現數據的正確通信。

OMAP-L138;FPGA;EMIFA;FIFO;異步緩存

0 引言

OMAP-L138是美國TI公司生產的基于達芬奇(DaVinci)技術的ARM+DSP雙核處理器,具有ARM926EJ-S和C674X高速浮點DPS兩個異構內核,采用OMAP-L138+FPGA雙芯片構建數控系統的硬件平臺,能夠滿足高性能數控系統對界面層、控制層和設備層開發的要求。異構多核結構系統中,各處理器之間的實時通信將直接影響整個控制系統的性能及可靠性,其中ARM與DSP的通信通過共享內存方式進行數據交互,而DSP與FPGA常用的通信接口主要有總線型接口、存儲型接口、串口型接口、主機型接口和特殊接口。其中總線接口開發難度較大,需要協議支持;串口接口開發簡單,但是速率較慢;特殊接口不具備通用性,需要修改DSP驅動,開發周期長。

根據OMAP-L138+FPGA控制系統對數據傳輸量的需求及控制以及平臺的資源,選擇EMIF接口作為DSP與FPGA之間的通信接口方案。由于FP?GA開發端并沒有EMIF總線接口,需要進行編程完成接口功能。通常情況下采用FPGA的雙端口RAM或者FIFO來協調實現[1-3]。因此,本文針對雙刀頭高性能柔性材料切割系統的需求,采用OMAP-L138+FPGA雙芯片設計了數控系統硬件平臺,提出一種OMAP-L138 DSP通過EMIFA接口與FPGA的FIFO進行數據通信的設計方案,實現了DSP與FPGA的高速實時通信。

1 OMAP-L138+FPGA數控系統硬件平臺設計

本文研究的柔性材料切割系統要求有兩個數控切割刀頭,分別控制兩組X-Y-C軸和Z軸4軸刀頭運動切割皮革、布料等柔性材料。其中C軸是導向控制軸,用于刀刃方向對X-Y輪廓的跟隨控制。該系統是8軸進給,雙3軸聯動運動控制系統。因此,硬件系統不但要有強大的插補運算能力,還有設備驅動的擴展要求。

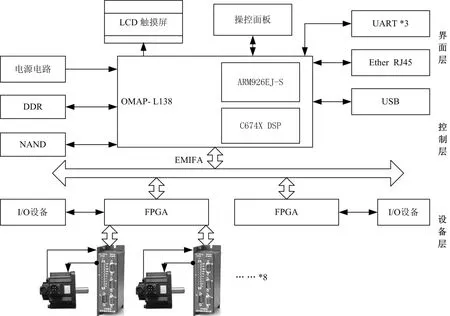

根據要求,硬件系統由OMAP-L138和Cy?clone II FPGA組成(如圖1所示)。系統劃分為界面層、控制層和設備層三部分。界面層由ARM內核基于Linux操作系統開發,主要提供人機操控界面、數控程序管理、文件服務、上位機通訊和系統維護等功能。控制層在DPS內核基于DPS/BIOS實時操作系統開發,主要完成數控軌跡前瞻、運動加減速規劃、雙三聯動插補、刀向跟隨運動、雙刀頭干涉避讓、刀尖Z向補償等控制與計算。設備層由FPGA實現,主要實現對伺服驅動的數字/脈沖轉換控制,并提供各種I/O信號的處理功能。

圖1 8軸OMAP-L138+FPGA柔性材料切割數控系統結構

2 DSP的EMIF(外部存儲器接口)介紹和硬件接口設計

2.1 OMAP-L138 DSP硬件接口EMIFA介紹

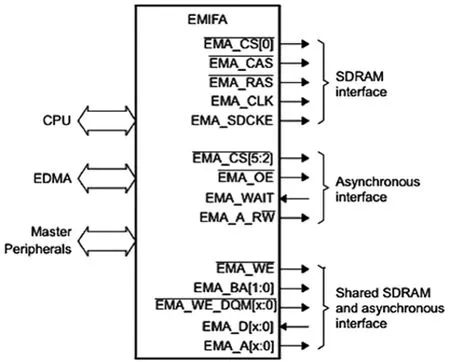

EMIFA是外部存儲器件和OMAP-L138 DSP的接口,提供64 bit寬度的外部總數據接口,也可以作為32 bit寬度使用;共支持4個大小32 M異步外部存儲器,可以通過配置外接不同類型的存儲設備,包括同步突發靜態 RAM(SB?SRAM)、同步動態RAM(SDRAM)、各種異步設備(SRAM、ROM和FIFO)以及同步FIFO[4]。圖2為OMAP-L138 DSP EMIFA接口的功能模塊圖。

圖2 OMAP-L138 DSP的EMIFA接口功能模塊

2.2 FPGA與EMIFA的硬件接口及讀寫時序

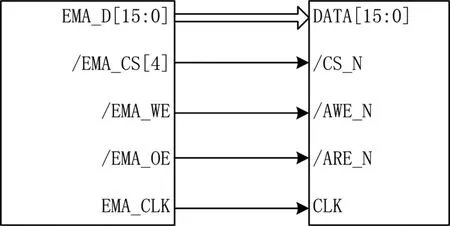

如圖3所示為FPGA與EMIFA的硬件接口連接圖。OMAP-L138 DSP的EMIFA與FIFO通信數據為16位,選取片選空間/EMA_CS[4]。其中,FP?GA工作時鐘為EMIFA工作時鐘(EMA_CLK, 100 MHz),/EMA_WE為DSP往FPGA寫入數據的判別信號,/EMA_OE為DSP讀取FPGA數據的判別信號。

圖3 FPGA和DSP之間的接口連接圖

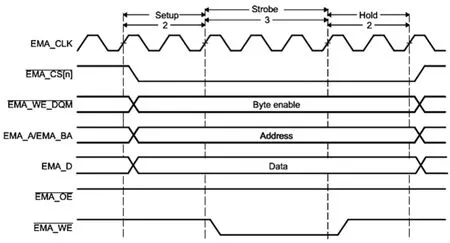

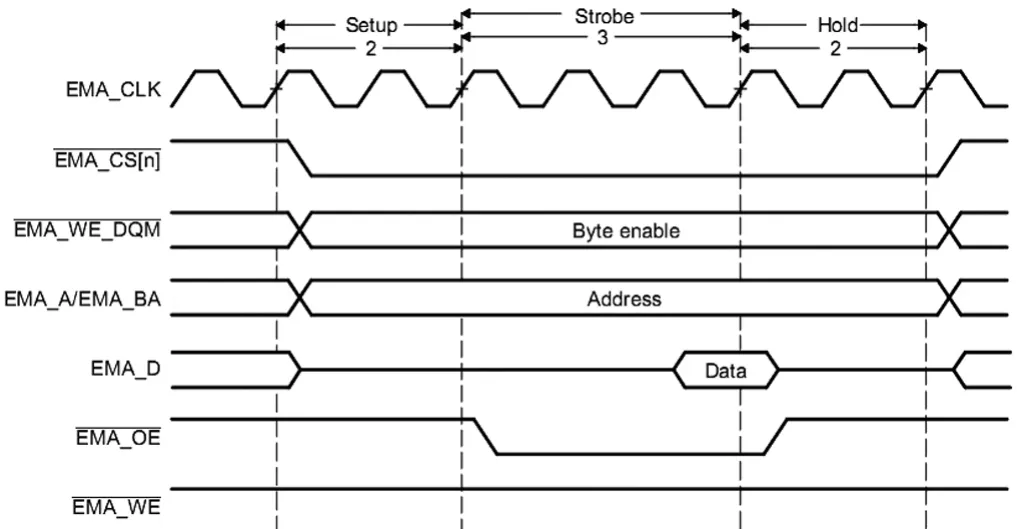

如圖4所示為FPGA與EMIFA的接口寫時序圖,從中可以看出,DSP往FPGA寫入數據需要三個步驟:建立(Setup)、寫入(Strobe)和保持(Hold)。同時,把單個數據所占時長設計為7個主時鐘周期,前2個時鐘周期設為建立時間,/EMA_WE從第3個時鐘周期開始置低并保持3個周期長度,這樣就保證了有充足的時間用于數據寫入準備。在/EMA_WE的兩次寫入低電平之間需保證2個時鐘周期以上的時間用于數據保持。FPGA就在這個時刻進行數據采樣,完成數據的傳輸。

圖4 EMIFA與FPGA的FIFO的接口寫時序圖

如圖5所示為FPGA與EMIFA的接口讀時序圖。與寫時序一樣,DSP讀取FPGA數據同樣需要三個步驟:建立(Setup)、寫入(Strobe)和保持(Hold),各個階段所占時長與寫時序一致。本次設計DSP讀取的FPGA數據為FIFO的數據存儲個數,在/EMA_OE為低電平時完成數據的讀取。

圖5 EMIFA與FPGA的接口讀時序圖

3 FPGA異步緩存FIFO模塊設計

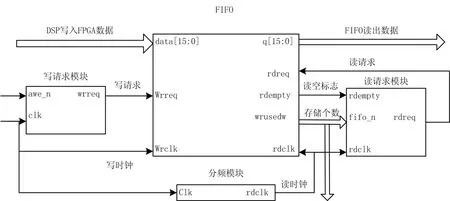

FIFO(First In First Out)是一種先進先出的數據緩存器,而異步FIFO是用一種時鐘寫入數據,用另一種時鐘讀出數據[5]。本次設計中,FPGA選用Cyclone II系列的EP2C8,FIFO深度為4 M。如圖6所示,為異步緩存模塊設計框圖。其中,clk為FPGA工作時鐘 (CLK,100 MHz),rdclk為clk通過分頻模塊得到的時鐘,大小為4 kHz。

圖6 異步緩存模塊設計框圖

3.1 讀寫請求的產生

(1)基于字面匹配的語義相似度計算方法。比較典型的有基于LCS[8]、TF-IDF[9]的語義相似度計算方法。基于LCS的語義相似度計算方法是利用2個文本中詞語的最大公共子串的長度來計算文本之間的相似度;基于TF-IDF的語義相似度計算方法是將文本建模成詞頻向量,運用余弦相似度來衡量文本之間的相似度。這類方法的優點是計算速度快、工作量小,缺點是忽略了詞語的語義信息,需要人工設定停用詞表。

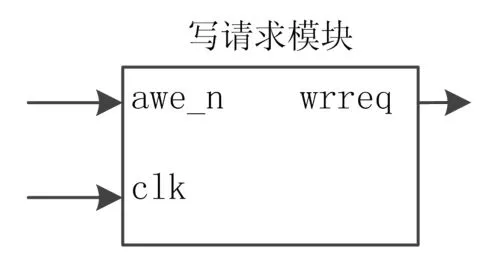

根據FPGA與DSP EMIFA接口的寫時序圖(如圖4所示),DSP往FPGA寫入單個脈沖數據時,/EMA_CS[4]拉低并持續7個寫時鐘周期,/ EMA_WE拉低并持續3個寫時鐘周期。而FIFO在寫時鐘的上升沿檢測到寫請求(wrreq)為高電平時,寫入一次數據。因此,為了避免FIFO重復寫入同一脈沖數據,寫請求應該在每一個/EMA_WE信號的下降沿產生(有效,即置高),并持續一個寫時鐘周期。寫請求產生模塊如圖7所示,其中clk配置外接DSP的EMA_CLK引腳,awe_n外接/ EMA_WE,wrreq為寫請求。

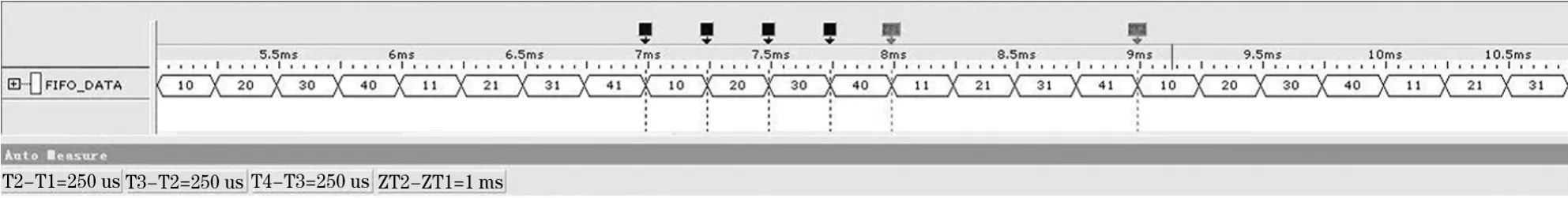

FIFO讀出數據和寫入數據原理一致,在讀時鐘的上升沿檢測到讀請求(rdreq)為高電平時,讀出一個數據。本次設計中,讀時鐘頻率設置為4 kHZ。FIFO在讀時鐘下讀出的每個數據持續時間為250μs,因此,FIFO在讀出第一個數據開始,讀請求信號(rdreq)應該一直有效、置高。為了保證數據的連續性,讀請求信號(rddreq)在FIFO的存儲個數大于等于4個,直到rdempty為高電平時置低。圖8為讀請求產生模塊,其中,rdclk接由clk通過分頻模塊產生的時鐘信號,rdempty和fifo_n分別接FIFO的rdempty信號和wrusedsw信號。

圖7 寫請求產生模塊

圖8 讀請求產生模塊

3.2 DSP讀取FPGA的FIFO存儲個數

本次設計中FIFO存儲容量(深度)設置為4 M,由于DSP往FPGA的FIFO寫入數據的速度遠遠高于FIFO讀出數據的速度,勢必會造成FIFO存儲數據的溢出。為了避免數據溢出造成的數據丟失和紊亂,DSP在每次通信中應該先查詢FPGA的FIFO的存儲數據個數。若存儲個數低于上限值,DSP繼續往FPGA傳送數據;否則,DSP停止往FPGA傳送數據。本次設計中,設置允許DSP往FPGA傳送數據的上限為200個,即50組脈沖數據包。

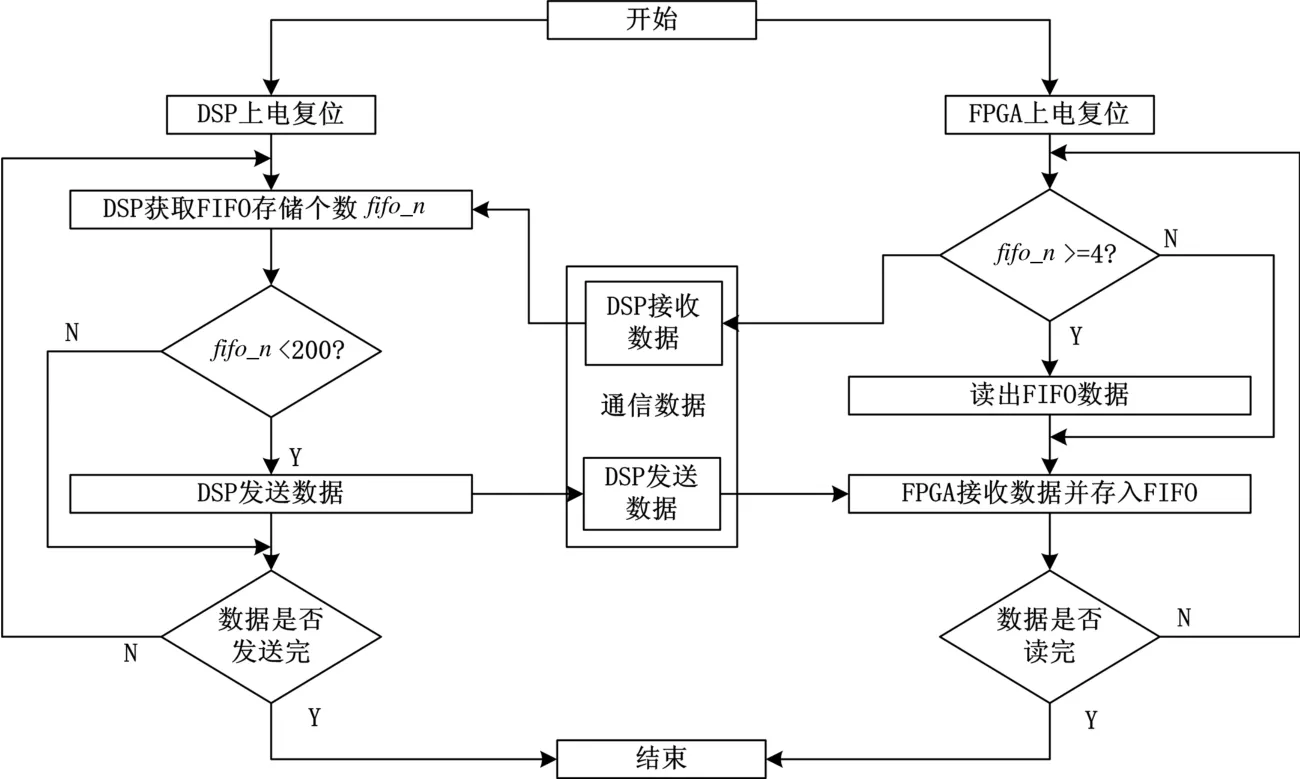

4 接口實現流程

DSP和FPGA開始工作時,上電復位。在DSP與FPGA的通信過程中,DSP在每次通信前,先獲取FPGA的FIFO存儲個數fifo_n。當fifo_n小于規定的上限值(本次設計設置為200)時,DSP發送一次數據包。如此循環,直到數據發送完畢,最后停止通信。

FPGA在兩者通信過程中處于從屬狀態,當DSP需要讀取FIFO存儲個數fifo_n時,FPGA只需把fifo_n賦值給通信數據DATA;當DSP發送數據包時,FPGA將接收的數據依次寫入FIFO中。與此同時,當FIFO存儲數據的個數超過4個時,開始讀出數據,直到FIFO為空。圖9為接口實現程序流程圖。

圖9 程序流程圖

5 EMIFA配置程序及實驗驗證

如圖10所示,為基于OMAP-L138和FPGA的異構雙核嵌入式系統測試板。DSP接口軟件設計主要是通過TI公司的集成開發環境CCS3.3軟件,利用支持庫文件對EMIFA相關寄存器進行配置。本次設計為了便于實驗分析驗證,EMIFA配置程序主要實現了DSP往FPGA的FIFO中重復寫入10、20、30、40、11、21、31、41數據。

圖10 控制平臺測試板

6 結論

經過邏輯分析儀實驗驗證分析,能夠實現正確符合設計要求的數據通信。將本次設計完成的OMAP-L138與FPGA之間的通信方案應用到柔性材料數控系統中,OMAP-L138將進行了插補運算后的數據通過該方案傳輸給FPGA,再由FPGA進行數據脈沖轉換輸出同步脈沖驅動8軸實現雙刀頭3軸聯動插補控制。運用了該方案的雙刀頭高性能柔性材料切割系統已開發完畢,并投入到生產線上,已于深圳某鞋業公司穩定運行生產,獲得了預期效果。因此,本次基于異步緩存FIFO的DSP EMIFA與 FPGA的通信方案能夠實現OMAMP-L138與FPGA的正確通信。

圖11 邏輯分析儀測試結果

[1]李樂.DSP+FPGA折反射全景視頻處理系統中雙核高速數據通信[J].電子與信息學報,2010,32(3):649-654.

[2]胡彬,陳濤.TMS320C6713DSPEMIF接口與FPGA雙口RAM接口設計[J].測試測量技術,2008(10):32-35.

[3]任勇屹,張祺,韋忠正.一種FPGA和TMS320DM642的通信方案[J].計算機應用與軟件,2013,30(7):298-300.

[4]Texas Instruments.External Memory Interface A(EMI?FA)[R].December 2011.

[5]胡波,李鵬.異步FIFO在FPGA與DSP通信中的運用[J].電子科技,2011,24(3):53-61.

(編輯:向 飛)

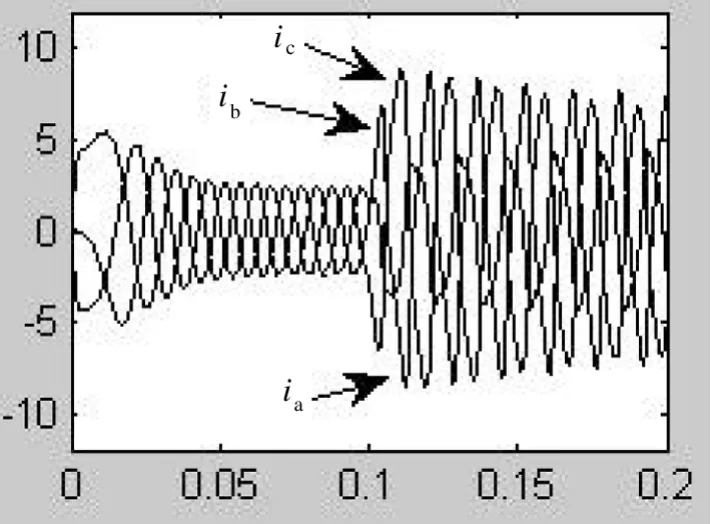

圖9 T1和T2同時在t=0.1 s故障時MLD模型中三相電流

圖10 T1和T2同時在t=0.1 s故障時三相電流殘差

參考文獻:

[1]崔博文,任章,陳劍,等.逆變器供電的電動機變頻調速系統實時故障檢測[J].電機與控制學報,2006(01):54-56.

[2]崔博文,任章,陳劍,等.逆變器供電的感應電機驅動系統故障仿真研究[J].電機與控制學報,2007,11(1):578-583.

[3]仇志凌.基于LCL濾波器的三相三線并網變流器若干關鍵技術研究[D].杭州:浙江大學,2009.

[4]安群濤.三相電機驅動系統中逆變器障診斷與容錯控制策略研究[D].哈爾濱:哈爾濱工業大學,2011.

第一作者簡介:羅 凱,男,1986年生,江西南昌人,碩士研究生。研究領域:船舶電力推進及其控制。

Design on Communication between OMAP-L138 DSP and FPGA

ZHANG Wei-wen,GAO Wei-qiang,LIN Gan,LIU Jian-qun,YAN Qiu-sheng

(School of Electromechanical Engineering,Guangdong University of Technology,Guangzhou510006,China)

A data communication design between OMAP-L138 DSP and FPGA FIFO is proposed with the data transfer requirement of OMAPL138+FPGA control system and the platform resources for High performance flexible materials pole head CNC cutting system.DSP transmits the processed data to FPGA via the asynchronous FIFO with EMIFA interface.And the FIFO receivers the high-speed data from DSP,while outputting data from the asynchronous FIFO.The design is verified to achieve the correct communication with the laboratory tests by logic analyzer.

OMAP-L138;FPGA;EMIFA;FIFO;asynchronous cache

TP273

B

1009-9492(2015)10-0115-05

10.3969/j.issn.1009-9492.2015.10.029

張偉文,男,1989年生,廣東汕尾人,碩士研究生。研究領域:數控技術。

崔博文,男,1966年生,博士,教授。研究領域:電力電子技術、電力電子系統故障診斷技術。

(編輯:向 飛)

2015-04-15