基于FPGA的高標清數字光端機的研究

楊紅軍,洪三其

YANG Hong-jun, HONG San-qi

(武漢輕工大學 機械工程學院,武漢 430023)

0 引言

隨著社會的進步及科技的發展,人們對于安防監控的需求越來越高,傳統的模擬標清視頻技術由于圖像質量差、分辨率低等缺陷已不能滿足社會的需求,但由于該類設備還占有大量市場,因此,對原有設備進行改造,使同軸電纜中同時可傳輸模擬標清和高清視頻信號成為當前研究的重點。本文從低成本的觀念出發,設計了一種基于FPGA的數字光端機,可以將多路低速并行數字信號復用到一路高速串行數字信號中,并通過光纖實現千兆速率高速傳輸,在交通、治安管理,家庭、小區、學校安全防范,遠程視頻會議、遠程教育等領域具有廣泛的應用前景。

1 光端機的系統結構

根據視頻信號的采集到最后視頻信號的還原輸出數據流的傳輸過程,光端機的硬件系統結構如圖1所示。

視頻信號先通過模擬緩沖模塊對信號進行補償、濾波,增強信號的驅動能力,然后通過模數轉換后輸入到FPGA構成的光端機信號發送模塊,經過處理后,然后由通過光模塊傳輸到光端機的接收端,其接收端同樣由FGPA芯片構成,通過處理后的信號經過數模轉換后經驅動輸出給終端顯示裝置,還原成高清或標清視頻。

2 硬件電路的設計及元件選型

圖1 光端機的組成結構

2.1 模數轉換(ADC)及數模轉換(DAC)模塊

本系統設計了的數字光端機可以同時采集及傳輸多路視頻信號,這里以四路信號為例。通常安防領域的同軸技術類型標清視頻信號及高清視頻信號峰峰值最大為1Vp-p,模擬調制帶寬標清最高20MHz,高清最高40MHz,本系統可同時處理高標清信號,因此模數轉換裝置ADC的輸入模擬調制帶寬應至少在40MHz以上,依據采樣定理可知ADC的采樣頻率至少為80MHz及以上,為便于計算,設計ADC采樣頻率選擇90MHz,根據經驗設置采樣精度8bit。那么每信道數據為720Mbps,四個信道數據為2880Mbps。通過主控芯片FPGA的串行化數據組裝,則傳輸數據為2880Mbps,設置FPGA信道帶寬為3G(因為其中包含幀頭數據及串口通訊等數據)。在光端機接收端,信號分離后,每信道720Mbps數據不變,DAC轉換速率為90MHz,精度8bit。

據此,ADC 選用ADI公司的AD9057BRS-60型號ADC,其采樣率最高兼容60MSPS,內置2.5V電壓參考,設有跟蹤和保持電路,兼容TTL/CMOS輸入,單一5V供電,精度為8bit[1]。每個信道采用兩片ADC進行采樣。設定每個ADC采樣時鐘45MHz,并以間隔180°的時鐘相位差進行采樣,以降低成本。DAC選用AD公司的AD9114數模轉換器,分辨率8bit,輸出形式為4mA~20mA的差分電流,因此需要在輸出引腳之間接50Ω 的電阻,轉為以電壓信號輸出。

2.2 FPGA模塊硬件電路設計

本設計選擇ALTERA公司的FPGA Cyclone IV系列EP4CGX30CF23I7NGX作為主處理器,完成整個系統的調度以及信號處理等。EP4CGX30提供高達八個3.125Gbps高速收發器,具有6K到150K的邏輯單元,6.3Mb的嵌入式存儲器,小于1.5W的總功耗,工作溫度為-40°C~100°C,484-BGA封裝,具有Serdes模塊及CDR單元,電源電壓為1.16V~1.24V[2]。

2.2.1 發送端FPGA模塊設計

選擇FPGA的BANK7 I/O口作為輸入口數據通道,接收ADC傳輸的數據,其模塊接口設計如圖2所示。

圖2 FPGA ADC模塊接口設計

發送端FPGA發射光信號接口設計如圖3所示。

Serdes模塊支持信號傳輸速率達3.15Gbps,輸出信號電平為PCML電平。在輸出端設計交流電容,使FPGA的差分PCML信號與光模塊進行AC耦合。并在靠近發送方在兩條差分傳輸線上并聯電阻,實現信號鏈路的阻抗匹配,防止信號反射。

光端機接收端FPGA的DAC接口及光鏈路接口與發送端FPGA接口設計方法類似,這里不再描述。

2.2.2 FPGA的485控制數據模塊

圖3 發送端光模塊信號輸出接口

在FPGA的反向低速傳輸過程中,RS485控制數據量相對較少,設計傳輸速率為150Mbps。由于FPGA中的Serdes模塊支持的最低信號輸出速率為600Mbps。這里需通過對FPGA一個BANK進行編寫,在信號接收處理后的輸出轉化為LVDS差分輸出,并配置I/O電平為2.5V,如圖4所示。

圖4 FPGA 485信號傳輸接口設計

如圖4所示,其中R1和R2為LVDS的輸出匹配電阻,C1和C2為交流耦合電容,同時2.5V的電源及分壓電阻給LVDS提供輸出的電壓偏置。

2.2.3 FPGA時鐘域及同源時鐘設計

FPGA對數據的處理過程如圖5所示。

從圖中可以看出,FPGA系統邏輯工作的時鐘信號采用常用頻點24.75MHz,由外部晶振直接提供。Serdes時鐘信號為150MHz。ADC時鐘信號為45MHz,這里的45MHz的時鐘信號,一個是PLL2電路倍頻的45MHz時鐘信號提供給ADC1/2/3/4,另外一個相位差180°的時鐘信號是通過PLL2內部電路進行設置后將反向的45MHz的時鐘信號提供給ADC5/6/7/8。

圖5 FPGA的工作過程

在光接收機接收數據時,利用FPGA器件Serdes模塊中CDR單元,通過接收的數據流恢復數據的時鐘信號,并通過鎖相環電路后,發送給接收數據,解幀、解串。這就實現了整條數據鏈路上的同一時鐘配置,解決數據傳輸中的數據的延遲、堵塞或者放空[3]。

2.3 其他硬件模塊

2.3.1 光模塊硬件設計

在本文的光端機視頻信號傳輸中,正向視頻信號數據傳輸3Gbps,反向控制數據傳輸為150Mbps,因此光模塊選用奧雷光電公司的上下非對稱速率光收發一體模塊ATR-B41XX,發送速率可達3Gbps,接收速率為350Mbps,節省資源。ATR-B41XX采用單一3.3V電壓供電,LVDS差分檢測輸出[6]。這里發送端選用傳輸距離為20km,工作溫度-20℃~70℃的ATR-B4127,接收端光模塊為配對使用的ATR-B4127[4]。

2.3.2 運放模塊

選用Burr-Brown公司的OPA2345,OPA2345是一個具有雙通道軌到軌輸入與輸出的CMOS型運算放大器,增益帶寬5G,工作電壓3.3V,工作溫度-40℃~+85℃,單一2.5V~5.5V的輸入共模電壓300mV的范圍,最大靜態電流僅為250mA[5]。

3 FPGA的數據傳輸幀結構設計

從圖5所示 FPGA的工作過程可以看出,FPGA對數據流信號的處理,在橫向上要完成幀結構、幀頭以及數據復用及解復用的處理。在縱向上要完成發送端與接收端的數據通道時鐘設計。有關時針同源的設計已在硬件電路的設計中描述過了,在此還需要對幀頭的結構進行設計,以實現數據的自適應傳輸。在過程工業的控制中存在著大量的通信協議,這些協議基本都是建立在數據幀的基礎之上,其差別在于數據幀的格式[6]。通過特殊的幀頭設計,在接收端只要檢測出數據幀頭就可以立即將要傳輸的視頻信號等數據發送出去。幀頭數據在數據幀的起始位置,幀頭后依次是信道的數據、串口通訊數據。采用硬件電路嵌位以及軟件編程數據嵌位的方法使數據幀頭具有唯一特性。

由ADC9057輸入信號范圍通過運放的硬件電路嵌位為2.205V~2.925V。又ADC精度8bit,2~3V的輸入,則輸入2.925V對應的二進制為11101011,2.205V對應為00111100。為應對有效數據突變,在FPGA內部對輸入信號進行軟件編程嵌位,使ADC轉換后的值最大嵌位在11101011,最小嵌位為00111100。最小值嵌位是防止長0出現,影響數據傳輸。根據排列組合,只要將幀頭設置超過10個連續以上的1就保證了幀頭唯一性。為方便計算及傳輸,幀頭設置為0001111111111000,為16bit。

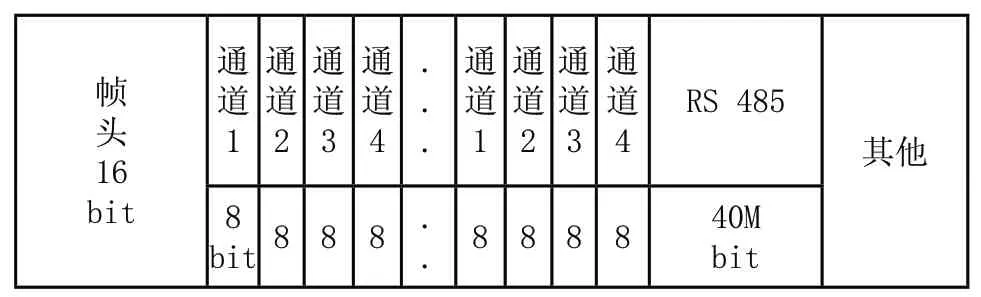

前面已經設計一周期數據為3 G,有效數據為2880M,規定0.5s為一幀,那么一幀數據就為1500Mbit,視頻有效數據1440Mbit,RS485定義40Mbit,其他為預留空間。則幀結構如表1所示。

表1 幀結構表

4 系統測試

系統測試是檢測系統傳輸過程中信號的時鐘抖動、眼圖優劣、設備的靈敏度、設備的動態范圍以及系統的功耗等。

光端機信號測試眼圖,如圖6所示,可以看到眼圖的輪廓明顯,眼睛掙得很開,交叉點平衡,信號變換間沒有大的抖動,完全沒有壓到眼圖的模板,沒有碼間串擾現象,因此可以知道系統信號傳輸穩定,信號質量很高。

圖6 信號測試眼圖

將光端機視頻信號的接收端分別接入標清及高清的不同格式視頻信號,經測試表明當傳輸960H、720p每秒25幀、1080p每秒25幀等高清視頻圖像時,圖像顯示穩定,無噪點、畫面平滑、連續、不卡幀,因此光端機具有自適應高標清視頻信號傳輸的能力。

5 結束語

本文研究的四路高標清視頻自適應傳輸數字光端機系統,設計基于FPGA平臺,通過調試及測試,驗證了高清標清視頻自適應傳輸功能,實踐檢驗光端機具有標清、高清信號傳輸能力,達到了設計技術指標。光端機在數據幀的設計中,有多的數據量傳輸富余,可以用于實現更多的其他業務數據傳輸需求。

[1]AD9057 [DB/OL].http://pdf1.alldatasheet.com/ datasheet-pdf/view/48514/AD/AD9057.html

[2]CycloneIVFPGA[DB/OL].https://www.altera.com/content/dam/ altera-www/global/en_US/pdfs/ literature/hb/cyclone-iv/cyclone4-handbook.pdf.

[3]潘波,朱偉.基于Serdes的千兆以太網設計與實現[J].微處理機.2014,(01),33-35.

[4]ART-B41XX [DB/OL].http://www.allrayinc.com/main/ProductParameter_om.asp?PParentID=72&ParentID=90&SortID=99&id=654.

[5]OPA2345 [DB/OL].http://pdf1.alldatasheet.com/datasheet-pdf/view/56774/BURR-BROWN/OPA2345.html.

[6]董立,尤楓,趙恒永.基于用戶定制的數據幀處理技術[J].計算機工程與設計,2010,(12),3003-3005.