基于CPLD的LCD1602顯示系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

陳海峰,丁麗麗

(1.華南農(nóng)業(yè)大學(xué) 珠江學(xué)院,廣東 廣州510900;2.廣州城建職業(yè)學(xué)院,廣東 廣州510900)

基于CPLD的LCD1602顯示系統(tǒng)設(shè)計(jì)與實(shí)現(xiàn)

陳海峰1,丁麗麗2

(1.華南農(nóng)業(yè)大學(xué) 珠江學(xué)院,廣東 廣州510900;2.廣州城建職業(yè)學(xué)院,廣東 廣州510900)

為了提高LCD1602顯示效果,增強(qiáng)抗擾能力,文章基于TOP2812開發(fā)板,依據(jù)LCD1602操作時(shí)序要求,在開發(fā)板CPLD部分實(shí)現(xiàn)了LCD1602顯示系統(tǒng)的設(shè)計(jì)。文中對(duì)LCD1602時(shí)序進(jìn)行了詳細(xì)分析,并在Quartus II平臺(tái)下采用Verilog HDL編寫了test bench測(cè)試文件和驅(qū)動(dòng)程序,經(jīng)仿真和實(shí)際測(cè)試表明,顯示效果較好,達(dá)到了設(shè)計(jì)要求。

CPLD;LCD1602;顯示系統(tǒng);時(shí)序;Verilog HDL

隨著技術(shù)的發(fā)展,社會(huì)數(shù)字化的程度顯得越來越明顯,集成電路在社會(huì)當(dāng)中的應(yīng)用也越來越廣泛。傳統(tǒng)的ASIC曾在數(shù)字領(lǐng)域扮演重要角色,雖種類繁多,但功能固定、管腳有限,應(yīng)用范圍也相對(duì)較窄,因此在一定程度上限制了人們對(duì)其的使用。如今,隨著現(xiàn)場(chǎng)可編程技術(shù)的發(fā)展,F(xiàn)PGA及CPLD[1]技術(shù)已不再是傳統(tǒng)ASCI技術(shù)領(lǐng)域的一個(gè)點(diǎn)綴與補(bǔ)充,其顯然已成為電子應(yīng)用領(lǐng)域廣受歡迎的實(shí)用化技術(shù),為數(shù)字系統(tǒng)的科研實(shí)驗(yàn)、樣機(jī)試制、小批量產(chǎn)品的即時(shí)實(shí)現(xiàn)等提供了最佳途徑[2-3]。EPM240T100C5是Altera公司生產(chǎn)的MaxII系列CPLD,其功耗低、價(jià)格廉、配置靈活、資源豐富,具有較高的市場(chǎng)性價(jià)比,因而備受青睞。

在顯示輸出方面,目前主要采用3種方式,即:圖形、數(shù)字或?qū)S梅?hào),在嵌入式領(lǐng)域,顯示常采用LED、數(shù)碼管及液晶顯示器[4]。前兩種雖然實(shí)現(xiàn)簡(jiǎn)單,但顯示內(nèi)容不夠豐富。LCD1602具有體積小、功耗低、顯示容量大、接口簡(jiǎn)單,操作方便,能夠顯示字符、數(shù)字及符號(hào)等優(yōu)點(diǎn),因此被廣泛應(yīng)用于日常生活當(dāng)中。

該文以EPM2405100C5為控制核心,在Quartus II平臺(tái)下采用Verilog HDL編寫LCD1602顯示驅(qū)動(dòng)程序,并生成相應(yīng)目標(biāo)文件,最終下載至目標(biāo)芯片,實(shí)現(xiàn)LCD1602的顯示設(shè)計(jì)功能。

1 實(shí)現(xiàn)原理

將EPM240T100C5的I/O口與LCD1602的數(shù)據(jù)管腳及控制管腳進(jìn)行接口,利用Verilog HDL編寫軟件程序,使CPLD輸出滿足LCD1602的操作時(shí)序。由于LCD1602屬慢顯示設(shè)備,而CPLD往往時(shí)鐘頻率較高,為此需要對(duì)CPLD主時(shí)鐘進(jìn)行分頻,從而產(chǎn)生合適的時(shí)鐘信號(hào)供LCD1602使用。在讀/寫數(shù)據(jù)時(shí),需要對(duì)LCD1602的忙標(biāo)志進(jìn)行檢測(cè),只有在忙標(biāo)志位為0的情況下,才能完成對(duì)數(shù)據(jù)或指令的讀取與寫入。此外,為方便對(duì)LCD1602模塊進(jìn)行操作,其內(nèi)部控制器為該模塊提供了11條控制指令,通過寫入相應(yīng)的控制指令,可定制該模塊的顯示模式。LCD1602為用戶提供的存儲(chǔ)空間分3部分:DDRAM、CGRAM和CGROM。DDRAM共有80個(gè)存儲(chǔ)空間,對(duì)應(yīng)屏幕的兩行,每行40個(gè),但每行可顯示的地址只有16個(gè),其他地址所寫入的數(shù)據(jù)可通過移屏進(jìn)行顯示。CGRAM為用戶自定義字符圖形RAM,用戶可以定制特定的圖形。CGROM為字符發(fā)生ROM,其內(nèi)部已存儲(chǔ)160個(gè)不同點(diǎn)陣字符圖形,由于其編碼與ASCII碼基本一致,因此在進(jìn)入寫操作時(shí),也可直接寫入對(duì)應(yīng)字符,如寫8’h41,可顯示字符A,直接寫入“A”,也可達(dá)到同樣的顯示效果。

LCD1602的初始化主要用于完成字符顯示模式、光標(biāo)顯示模式、寫入數(shù)據(jù)后地址指針變化的設(shè)置、清屏及開顯示等操作。該模塊若要成功地被驅(qū)動(dòng),除了正確的初始化步驟以外,還必須依賴于準(zhǔn)確的操作時(shí)序,因此分析其操作時(shí)序也就顯得尤為重要。

2 時(shí)序分析

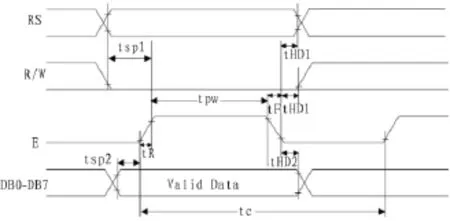

操作時(shí)序?yàn)镮C芯片的工作提供了正確的節(jié)拍,如果節(jié)拍錯(cuò)了,那么芯片將不可能正常工作。LCD1602的寫操作時(shí)序圖[5]如圖1所示。

圖1 LCD1602寫操作時(shí)序圖Fig.1 Write timing of LCD1602

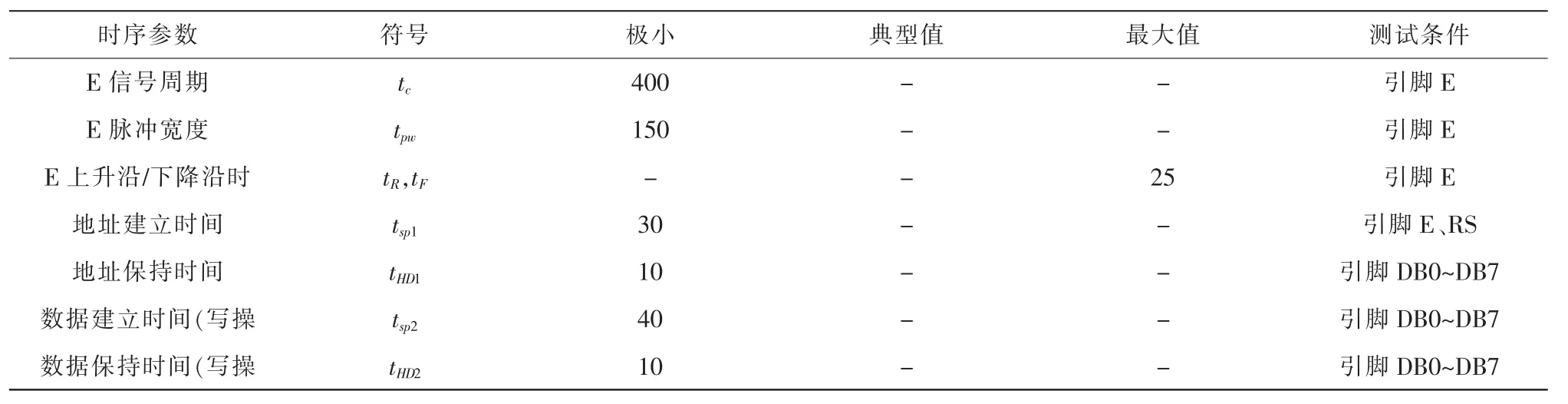

由圖1可知,若要寫入正確的數(shù)據(jù),必須在E的上升沿到來之前建立RS及R/W電平,同時(shí)完成數(shù)據(jù)的寫入操作,在E處于高電平期間,寫入的數(shù)據(jù)才能有效。圖1中,tsp1即為RS、R/W的建立時(shí)間,tsp2為數(shù)據(jù)的建立時(shí)間,若要正確完成寫入操作,必須使各建立時(shí)間滿足時(shí)序要求。數(shù)據(jù)在E的高電平期間有效,即持續(xù)一個(gè)脈沖寬度tpw。圖1中具體參數(shù)的時(shí)間要求如表1所示。

為方便建立E信號(hào)的波形,可取tpw=tc/2,即將E的波形設(shè)計(jì)為方波,只要保證tc>400 ns,,則其高、低電平所維持的時(shí)間都將不小于200 ns,而如果將RS、R/W及數(shù)據(jù)變化的時(shí)間都取在E信號(hào)低電平的中間位置,則地址及數(shù)據(jù)的建立時(shí)間和地址及數(shù)據(jù)的保持時(shí)間都將大于100 ns,對(duì)比表1的時(shí)序參數(shù)要求,顯然按這種方法設(shè)計(jì)出的時(shí)序是完全滿足LCD1602寫操作時(shí)序要求的。

因此,只需選取一個(gè)合適的tc,也就基本確定寫操作時(shí)序了。由于LCD1602初始化時(shí)需要延時(shí)5 ms來完成對(duì)顯示模式的設(shè)定,因此可選取5 ms作為tc的取值,從而簡(jiǎn)化顯示模塊的初始化操作。

表1 LCD1602時(shí)序參數(shù)要求Tab.1 Tim ing parameters of LCD1602

3 軟件實(shí)現(xiàn)

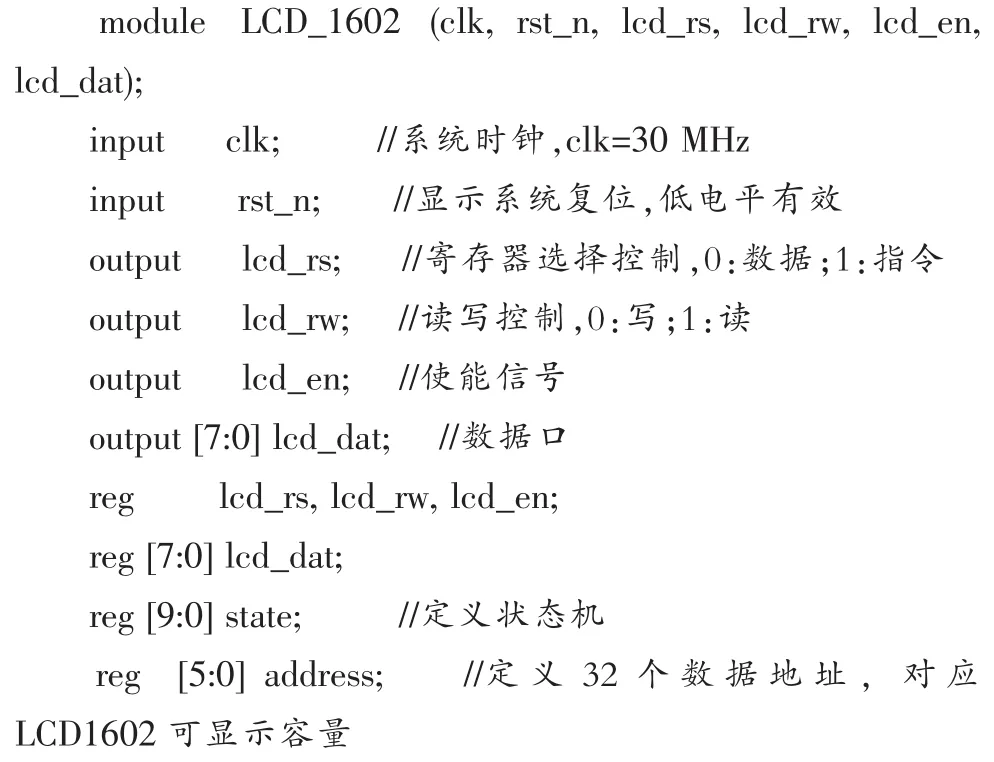

文中設(shè)計(jì)采用Verilog HDL實(shí)現(xiàn),模塊程序的接口如下所示:

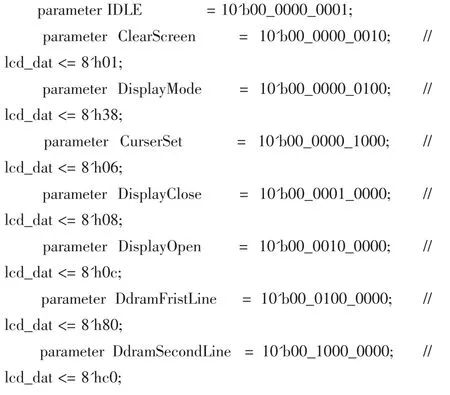

由于LCD1602初始化需要按特定步驟寫入不同的控制指令,其可顯示的數(shù)據(jù)地址在空間上是兩個(gè)獨(dú)立的固定區(qū)域,因此可借用有限狀態(tài)機(jī)的設(shè)計(jì)思想進(jìn)行設(shè)計(jì)系統(tǒng)。狀態(tài)采用一位獨(dú)熱碼[6]進(jìn)行編碼。所定義狀態(tài)如下:

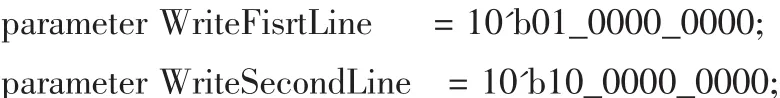

在Quartus II平臺(tái)下,經(jīng)綜合所得的狀態(tài)轉(zhuǎn)移關(guān)系如圖2所示。

圖2 狀態(tài)轉(zhuǎn)移圖Fig.2 State transition diagram

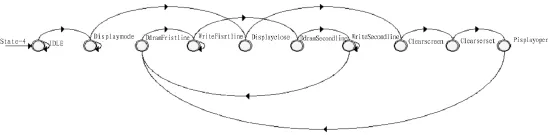

要想實(shí)現(xiàn)狀態(tài)的轉(zhuǎn)移,需構(gòu)建LCD1602顯示模塊所必需的時(shí)鐘,在時(shí)序分析過程中已確定將E信號(hào)的周期設(shè)計(jì)為5ms,而數(shù)據(jù)的寫入以及RS、R/W電平的變化總是在E信號(hào)低電平的中間發(fā)生,因此可重新建立一個(gè)時(shí)鐘,使其在該位置發(fā)生跳變,可以是上升沿也可以是下降沿,其周期與E信號(hào)周期相等,為便于設(shè)計(jì),也將該時(shí)鐘設(shè)計(jì)成脈寬為50%的方波信號(hào)。這里設(shè)E信號(hào)的時(shí)鐘為lcd_en,在E信號(hào)低電平中間位置跳變的時(shí)鐘為clk_flag。若選擇clk_flag的上升沿觸發(fā)RS、R/W電平的改變及數(shù)據(jù)的寫入操作,則顯然clk_flag高電平要超前clk_div高電平90°。為得到相位上互差90°的兩個(gè)時(shí)鐘,可以通過對(duì)系統(tǒng)時(shí)鐘分頻,構(gòu)建一個(gè)周期為2.5 ms的時(shí)鐘clk_div,使得clk_flag總是在clk_div的上升沿翻轉(zhuǎn),而lcd_en總是在clk_div的下降沿翻轉(zhuǎn),由此即可得到相位上互差90°的兩個(gè)時(shí)鐘信號(hào)了。由于主時(shí)鐘為30 Mhz,因此需對(duì)其進(jìn)行 37 500分頻,即可得到周期為 2.5 ms的clk_div。其軟件實(shí)現(xiàn)如下:

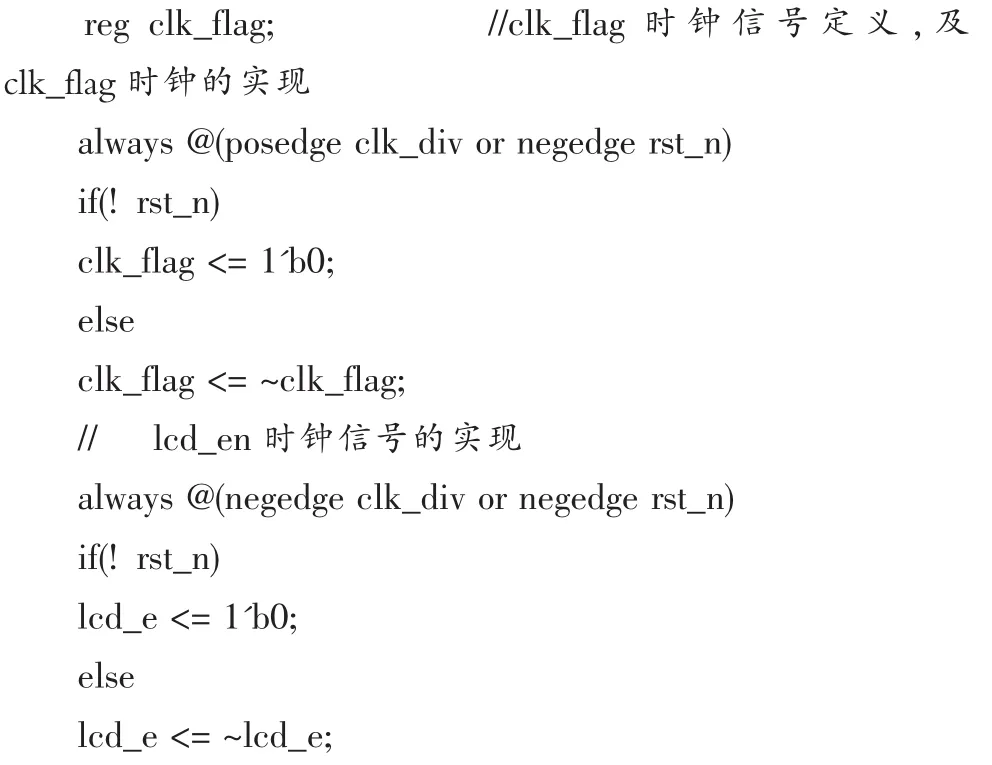

由clk_div時(shí)鐘信號(hào)獲取lcd_en及l(fā)cd_flag兩個(gè)時(shí)鐘信號(hào),具體如下:

至此,只需捕獲clk_flag的上升沿,并在該跳變沿處送入指令或數(shù)據(jù)即可。而狀態(tài)之間的轉(zhuǎn)移關(guān)系則需按初始化的正確步驟進(jìn)行,完成初始化后,指定DDRAM的地址,并向lcd_dat送數(shù)據(jù)即可實(shí)現(xiàn)數(shù)據(jù)的寫入操作。

4 仿真結(jié)果及實(shí)現(xiàn)效果

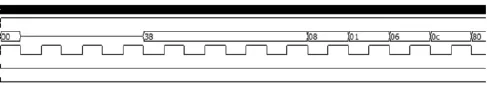

軟件仿真借助了第三方的仿真軟件Modelsim,在Quartus II當(dāng)中利用Test Bench Template Writer建立仿真模板文件,并在模板當(dāng)中給出激勵(lì)條件,編譯后即可生成用于仿真測(cè)試的vt文件了。初始化部分的仿真結(jié)果如圖3所示。

圖3 初始化部分仿真結(jié)果Fig.3 The simulation result of initialization

上圖信號(hào)從上到下依次為:clk,rst_n,lcd_dat,lcd_en,lcd_rs,lcd_rw。由圖3可知,由于系統(tǒng)時(shí)鐘頻率較高,clk已顯示為一條粗線,rst_n僅延時(shí)10個(gè)仿真單位,即被拉高為高電平,lcd_dat中出線一段藍(lán)色線條,占lcd_en的3個(gè)周期,即實(shí)現(xiàn)了15ms的延時(shí),緊接著的四個(gè)周期連續(xù)寫入8’h38,然后8’h01等,直到8’h0c完成對(duì)LCD1602的初始化。圖4為初始化后向 LCD1602寫入的數(shù)據(jù),由于顯示內(nèi)容的編碼與ASCII碼基本一致,可將其設(shè)置為ASCII進(jìn)行觀察。

將Verilog HDL編寫的程序進(jìn)行編譯,并將生的目標(biāo)代碼下載至EPM240T100C5,最終顯示的效果如圖5所示。

圖5 LCD1602顯示效果圖Fig.5 Display effort of LCD1602

5 結(jié)束語

通過對(duì)LCD1602時(shí)序進(jìn)行詳細(xì)分析,本文實(shí)現(xiàn)了用CPLD驅(qū)動(dòng)LCD1602顯示模塊工作的目的。通過仿真及硬件驗(yàn)證,均說明了設(shè)計(jì)的合理性與正確性。另外,采用模塊化設(shè)計(jì),也為后續(xù)系統(tǒng)的大規(guī)模化和可擴(kuò)展性提供了很大方便。相比單片機(jī)實(shí)現(xiàn)過程,利用CPLD實(shí)現(xiàn)顯得更加簡(jiǎn)單、方便。另外,CPLD管腳的可配置特點(diǎn)也為CPLD的使用帶來了極大的靈活性。隨著CPLD及FPGA技術(shù)的發(fā)展,數(shù)字系統(tǒng)設(shè)計(jì)也必將發(fā)展到一個(gè)新的階段。

[1]宋萬杰.CPLD技術(shù)及應(yīng)用[M].西安:西安電子科技大學(xué)出版社,2004.

[2]尚明.FPGA技術(shù)的應(yīng)用與發(fā)展趨勢(shì)[J].科技資訊,2007(14): 10-12.SHANG Ming.Application and development trend of FPGA technology[J].Science and Technology Information,2007(14): 10-12.

[3]孫明星.FPGA模擬IIC接口的Verilog HDL設(shè)計(jì)[D].蘇州:常熟理工學(xué)院,2008.

[4]黃杰勇.基于CPLD實(shí)現(xiàn)LCD1602顯示設(shè)計(jì)[J].科技創(chuàng)新導(dǎo)報(bào),2013(4):83,85.HANG Jie-yong.The achievement of LCD1602 display design based on CPLD[J].Science and Technology Innovation Herald,2013(4):83,85.

[5]長(zhǎng)沙太陽人電子有限公司[S].SMC1602 LCM使用說明書.

[6]夏宇聞.Verilog數(shù)字系統(tǒng)設(shè)計(jì)教程[M].北京:北京航空航天大學(xué)出版社,2008.

Design and im plementation of LCD1602 display system based on CPLD

CHEN Hai-feng1,DING Li-li2

(1.Zhujiang College of South China Agricultural University,Guangzhou 510900,China; 2.Guangzhou City Construction College,Guangzhou 510900,China)

In order to improve the display effort and enhance anti-disturbance capability of LCD1602,in this paper,the LCD1602 display system was designed according to the timing diagram of LCD1602 based on CPLD which is part of TOP2812 development kits.The timing diagram of LCD1602 display system was analyzed in detail.The driver and test bench file were programmed in Verilog HDL on the platform of Quartus II.The simulation and actual test shown good display effort,which reached the design requirements.

CPLD;LCD1602;display system;timing;Verilog HDL

TN46

A

1674-6236(2015)10-0182-04

2014-08-24 稿件編號(hào):201408134

陳海峰(1985—),男,河南洛陽人,碩士研究生。研究方向:工業(yè)控制及嵌入式系統(tǒng)。