模塊式可擴展的高速同步采集記錄系統設計

王 琦,王 壯,程 翥,苗可可

(1.國防科技大學 電子科學與工程學院,湖南 長沙410073;2.95972部隊,甘肅 酒泉735000)

0 引 言

數據采集記錄系統的本質是信號的變換和存儲,一個好的、全面的、穩定的多通道高速數據采集記錄系統[1,2]需要解決好高速模擬-數字轉換、精準時鐘同步、精確數據同步、高速數據傳輸、大數據存儲、數據控制、硬件接口、通道擴展以及采集功能模式設計等問題。目前,大部分多通道高速數據采集記錄系統均采用單板設計模式,即將實際需求的所有采集通道設計在一個電路板上,使用單個或多個FPGA 等控制運算單元進行數據控制,然后通過標準接口將數據發送至存儲單元存儲。這樣的設計通用性較差、采集通道很難擴展、采集控制和人機交互設計比較復雜。

為解決這些問題,本文運用模塊式思想設計了一種通道可擴展的多通道高速數據采集同步記錄系統,并對其核心模塊進行了邏輯設計。整體設計方面,系統由時鐘模塊、采集模塊、存儲模塊和主板控制器組成,各模塊接口均采用通用標準協議,數量可以任意擴展。

1 系統模塊式設計

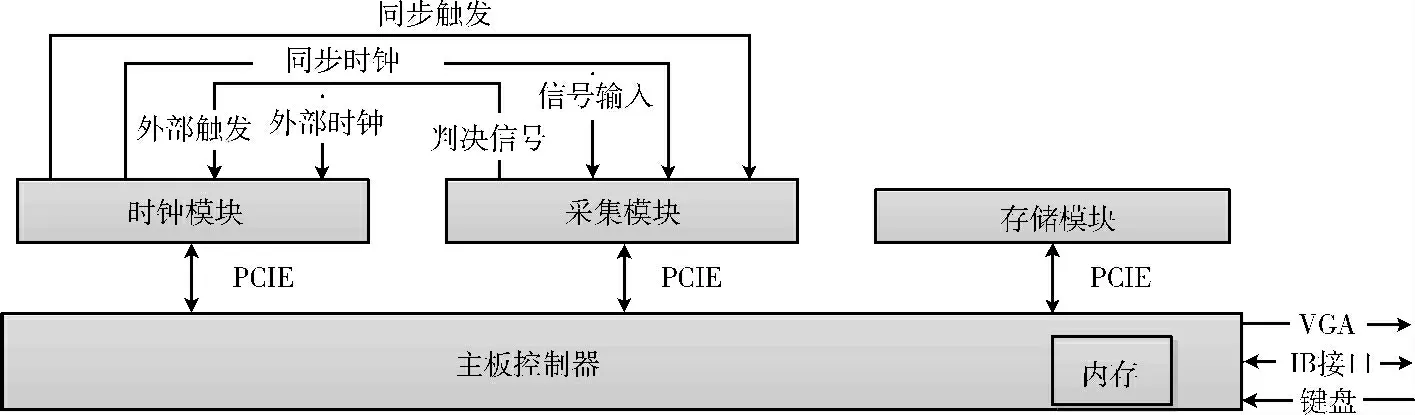

如圖1所示,系統由主板控制器通過PCIE[3]接口分別控制時鐘模塊、采集模塊、存儲模塊;時鐘模塊輸出的精準同步時鐘信號與觸發信號控制采集模塊,使得各采集通道同步采集,各路采集數據同步存儲;采集模塊通過ADC芯片、時鐘芯片、SDRAM、FPGA 芯片等[4],將模擬信號模數轉換、打包、緩存、發送,同時能夠條件式輸出判決信號,觸發時鐘模塊,實現對周期脈沖等特定信號的采集,FPGA 內設計的各功能通過Wishbone總線[5]進行控制;存儲模塊采用raid陣列[6],通過控制多塊固態硬盤,實現數據的高速存儲。主板控制器集成有INFINIBAND (IB)高速數據互聯接口,用于系統整體擴展時,系統間的數據共享。

系統工作時,外部模擬信號耦合輸入采集模塊,在時鐘模塊的同步時鐘控制下,采集模塊對數據進行采集,并對數據進行統計運算,與閾值比較后會產生判決信號觸發時鐘板輸出同步觸發信號。當觸發條件滿足時,時鐘模塊輸出的同步觸發信號觸發采集模塊對數據進行打包、緩存與上傳,主板控制器將采集模塊上傳的數據寫入存儲模塊,存儲模塊對寫入的數據進行永久存儲。

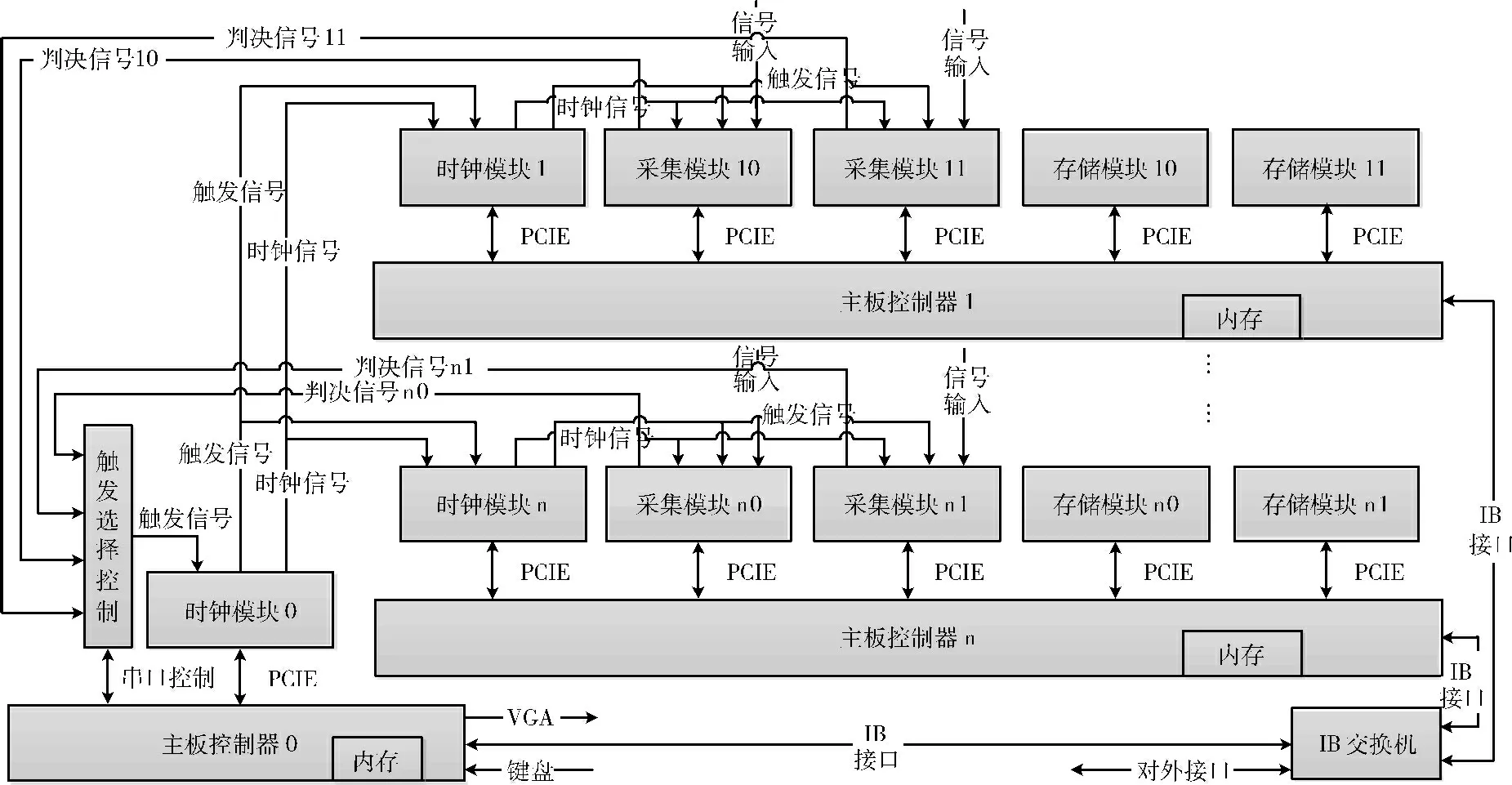

系統可以主板內各模塊擴展,也可以主板間整體擴展,如圖2所示,主板控制器0控制時鐘模塊0、其它主板控制器和人機交互以及觸發信號的選擇工作。在IB 交換機下,各主板通過高速IB 接口實現交叉互聯,由主機統一控制,各模塊產生的觸發信號也由主機控制選擇,選擇的觸發信號輸出到時鐘模塊觸發其輸出觸發信號。若每個采集模塊能夠實現8路AD 采集,時鐘模塊能輸出4 路時鐘信號和觸發信號,那么時鐘模塊一級級聯可以實現128路同步AD采集,所有采集通道均在時鐘模塊0的控制下高速同步采集,在同一觸發信號的控制下高速同步存儲。

整個系統中,采集模塊是核心模塊,其工作性能直接影響到整個系統的性能,因此下面重點介紹了采集模塊的結構設計和FPGA 內的功能程序設計。

2 采集模塊模塊式設計

為了提高系統的擴展性能,采集模塊采用通用接口,為了實現高數數據采集、運算,使用基于硬件電路處理的FPGA 作為運算與控制單元。

圖1 系統整體結構

圖2 系統采集通道擴展結構

2.1 采集模塊結構

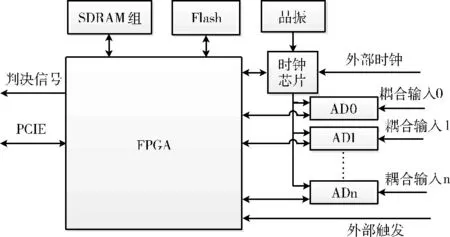

如圖3所示,采集模塊使用FPGA 芯片作為控制和運算單元,外設包括高速AD 芯片、精確時鐘芯片、大容量SDRAM、Flash芯片等。一塊FPGA 芯片可以外設多路AD、多塊SDRAM,同時采集板上集成有外部時鐘輸入、外部觸發輸入、判決信號輸出、PCIE等接口。

圖3 采集模塊硬件結構

外部輸入的同步時鐘信號通過精確時鐘芯片分配給各路AD 芯片,控制數據采集,保證同模塊各路之間和不同模塊之間的采集時鐘同步;觸發信號輸入FPGA,控制數據傳輸轉存,保證同模塊各路之間和不同模塊之間的數據同步存儲;大容量SDRAM 組對數據進行緩存,緩存數據通過PCIE接口輸出[7],上位機的控制命令也通過PCIE 接口[8]發送至FPGA;Flash存儲硬件程序、初始化參數、校準數據等。

2.2 FPGA模塊式設計

為了保證數據高效采集傳輸,關鍵在于采集模塊的邏輯設計,需要重點解決兩個問題:采集模塊FPGA 各外設與邏輯功能的控制問題和FPGA 采集數據的傳輸問題[9]。采集模塊外設的邏輯控制需要設計片上總線,FPGA 采集數據的傳輸需要設計板間數據高速互聯接口。

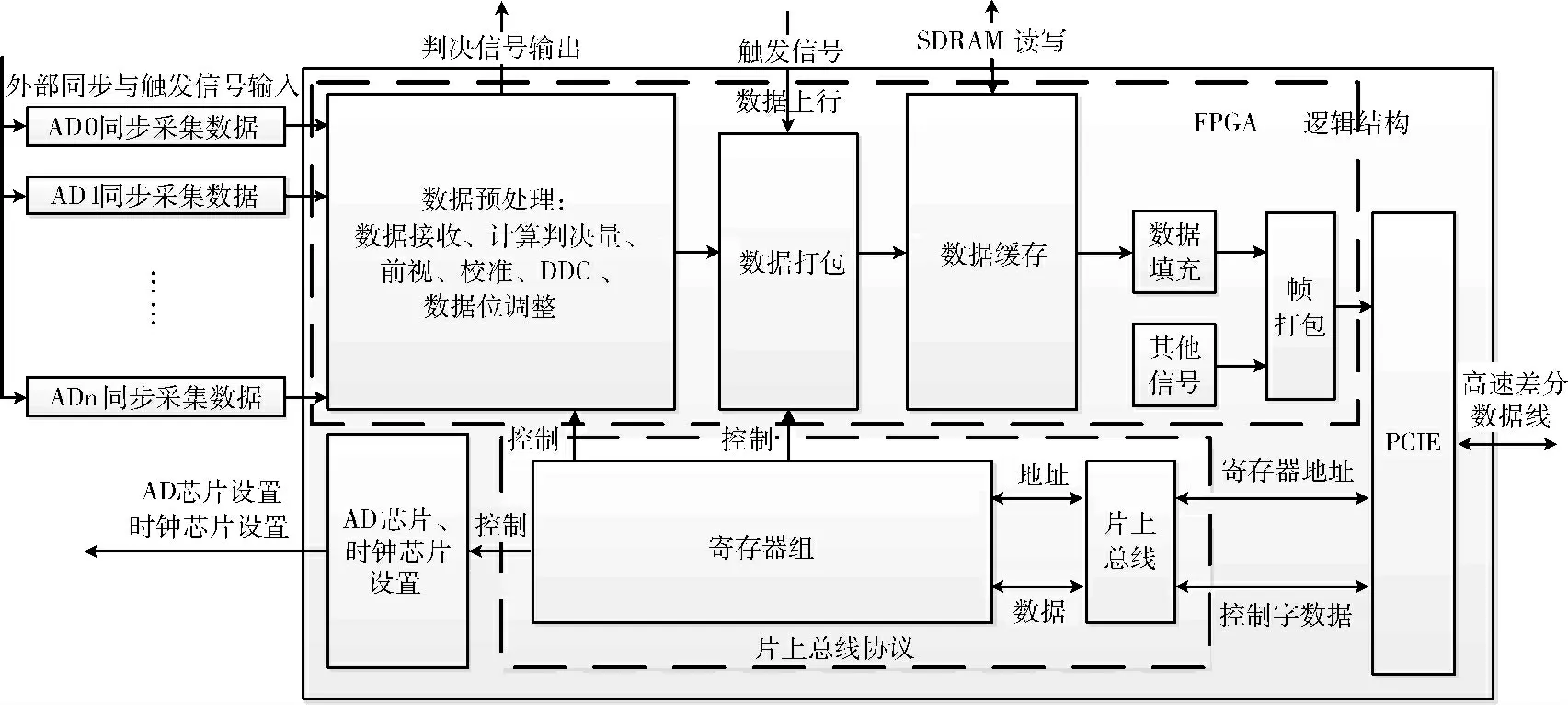

由于采集模塊FPGA 外設多,FPGA 內部邏輯功能繁雜,必須有一個可靠的、統一的、可擴展的控制總線進行控制管理,結構如圖4片上總線協議虛線框中所示。片上總線架構有很多,目前使用較多的幾種片上總線標準有ARM 的AMBA 總線、Silicore的Wishbone總線、IBM 公司的CoreConnect總線、Altera的Avalon總線和OCP-IP設計的OCP 總線,而Wishbone總線除了共享總線互聯外,還能實現交叉總線、點對點總線的互聯方式,因此在采集模塊功能控制中采用Wishbone總線[5]。

圖4 FPGA 邏輯結構

圖4中FPGA 邏輯結構主要包括兩大部分內容,數據上行模塊和片上總線模塊,此外還有外設的AD 芯片、時鐘芯片、Flash芯片等的驅動模塊以及PCIE數據互聯模塊。

數據上行要解決數據同步采集、同步數據傳輸、分路打包[10]、數據緩存等問題,圖4數據上行虛線框中為數據上行邏輯結構。數據進入FPGA 后,數據預處理模塊對每一路采集的信號進行預處理,包括增益校準、直流校準、前視緩存、觸發統計判決量計算、數字下變頻 (DDC)[11]、數據打包等,在觸發信號有效情況下按照VITA-49格式對數據打包,包頭信息內含點數、時間、通道編號、包編號和用戶可鍵盤輸入的參數等信息,通過路由控制進入SDRAM 緩存,數據從SDRAM 出來后,與溫度報警信號、溢出報警信號等數據進行幀打包,通過PCIE接口上傳。

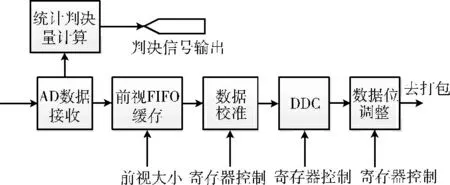

圖5所示為數據預處理模塊的數據控制邏輯結構。主要包括AD 數據接收、前視FIFO 緩存、數據校準、DDC、數據位調整等模塊。

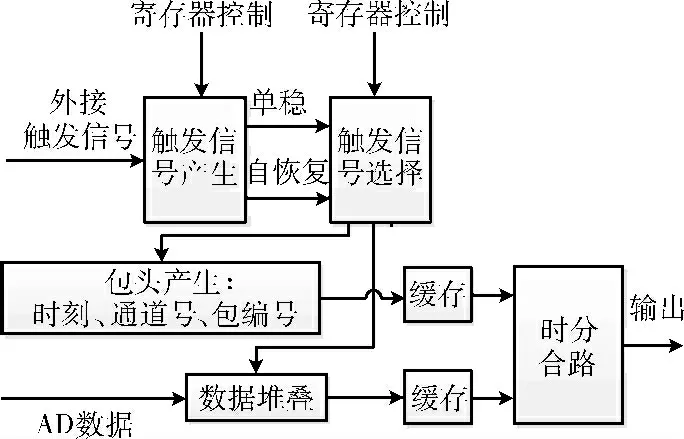

采集數據進入FPGA 后,分兩路分別進行處理:一路進行統計判決量計算,得到判決信號輸出;另一路進入前視FIFO,從前視FIFO 出來之后經過校準、DDC、數據位調整后進行打包,數據打包要在同一觸發信號下進行,其模塊設計如圖6所示。前視FIFO 前視大小、數據校準等都可通過寄存器控制。

圖5 數據預處理模塊邏輯結構

圖6 數據打包模塊邏輯結構

外部觸發信號進入FPGA 使得觸發有效或者寄存器設置觸發有效后,觸發信號產生模塊會根據寄存器設置,產生寬度可設定的單穩觸發信號,或者產生有效寬度可設定、間隔可設定、周期可設定的自恢復觸發信號;這些觸發信號經過選擇器控制VITA-49包頭信息產生、數據堆疊,產生的包頭信息進入緩存,調整與緩存中堆疊的AD 數據進行對齊,再按照打包標準數據寬度并行輸出。

3 系統實例

按照前文設計,實現了一套由一個時鐘模塊、兩個采集模塊、兩個存儲模塊和一個主板控制器構成的采集系統,實現了16通道、14bit、180 MHz連續采集,并對獲得的數據進行了測試。

3.1 系統實現

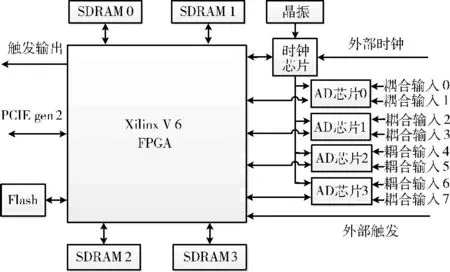

實現的系統中,時鐘模塊采用Xilinx FPGA 控制TICDCE72010時鐘芯片輸出4路同步時鐘信號,同時輸出4路同步觸發信號,設計有外部時鐘輸入、觸發輸入接口和8line PCIE gen1 接口。存儲模塊使用raid陣列管理控制器搭載8塊250 MB 固態硬盤進行高速存儲,存儲速度可達3.2GB/s。采集模塊使用Xilinx V6FPGA 作為控制和運算單元,結構如圖7所示。

圖7中,實際設計的采集模塊硬件結構使用PCIE gen2接口,FPGA 外設4個最高250M 采樣頻率、14bit采樣位數、2 通道的 LTC2157-14 AD 采集芯片,1 個 TICDCE72010時鐘芯片,4 個1GB SDRAM 芯片,1 個128 MB Flash芯片,設計有外部時鐘輸入、觸發輸入接口和8line PCIE gen2接口,輸入采用交流耦合輸入,輸入峰-峰值為1.5V。

圖7 實現的采集模塊硬件結構

3.2 性能測試

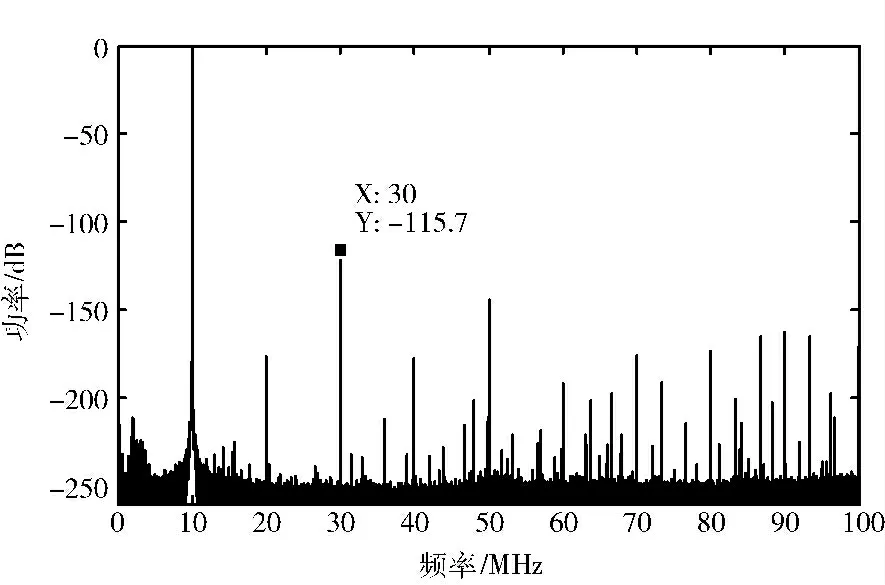

采集模塊采用PCIE gen2X8接口,數據實際傳輸速度可以達到3GB/s,在主板控制器控制下,AD 采集數據永久記錄速度平均為2.8GB/s,可實現8路14bit 180 MHz連續采集。前視大小最大為8192 個點,可以鍵盤觸發、GPS觸發、信號幅度觸發、帶寬能量觸發,觸發門限等參數可設置,采集樣式有單穩采集、自恢復采集,采集點數、間隔、周期等參數可設置。圖8為用200 MHz對峰-峰值1 V、頻率10 MHz的正弦信號進行采集后計算的功率譜。如圖8所示,相對峰峰值1V 的正弦信號,系統各頻點噪聲功率均在-100dB以下。

圖8 10 MHz正弦信號功率譜

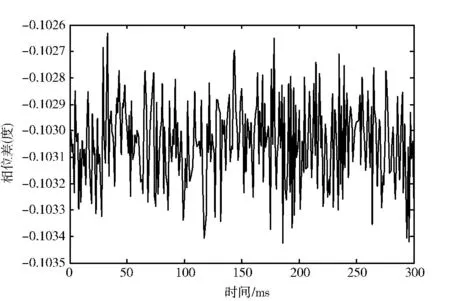

圖9所示為不同采集模塊上的兩路AD 用200 MHz對峰-峰值1V、頻率1 MHz的同一個正弦信號進行采集后計算的相位差隨時間的抖動。如圖9所示,由系統噪聲、采樣頻率等引起的兩路信號相位差在固定均值兩邊隨機抖動,均值為-0.1030度,標準差1.58×10-4度,可以看出兩路信號是在固定相位差周圍小范圍內抖動的,固定相位差可以通過調整時鐘芯片與數據對齊進行補償,相位差小范圍的抖動需要根據實際需求進行相應評估。

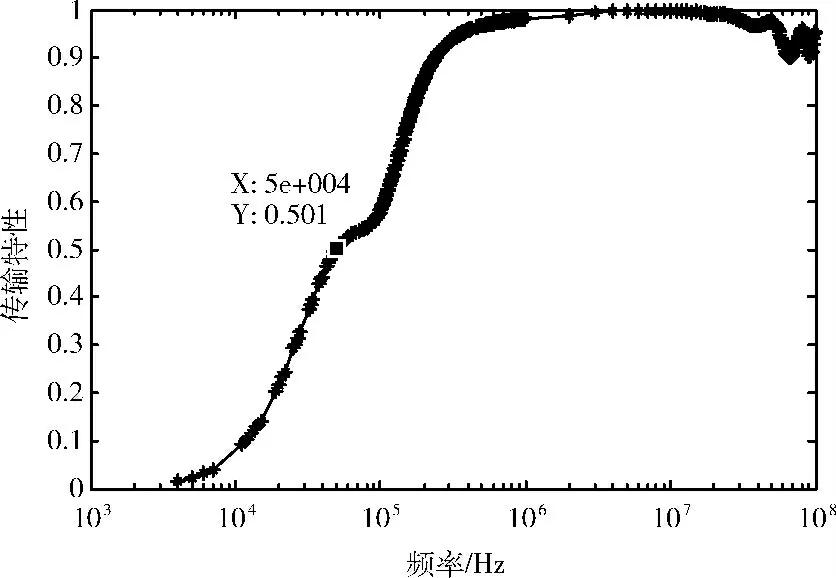

圖10 所示為采集模塊某一AD 采集通道對1 K-100 MHz信號的帶通特性。圖10中,采集模塊的3dB 帶寬為50K-100 MHz,500K-100 MHz內帶寬平坦度較好。

圖9 不同板AD 采集同一信號的相位差與時間關系

圖10 1K-100 MHz信號帶通特性曲線

4 結束語

整個系統在系統結構、各模塊結構、運算單元程序設計等方面均采用模塊化設計,使得系統采集通道數、各個功能等都能夠擴展,并且上位機容易控制,方便二次開發。

實現的系統采集模塊采用PCIE 2.0X8 接口,數據采集記錄速度達到2.8GB/s以上,能夠14bit 180 MHz的連續采樣,時鐘模塊一級級聯能夠實現128路同步采集記錄。系統同步性能穩定,信號通帶較平坦,系統噪聲較小。

[1]ZHAO Ruiguo,MA Jie,HE Zhiyong,et al.Design and application of high-speed acquisition database for liquid rocket engine[J].Journal of Rocket Propulsion,2011,37 (3):60-64(in Chinese).[趙瑞國,馬杰,何志勇,等.液體火箭發動機高速采集數據工程數據庫設計與應用[J].火箭推進,2011,37 (3):60-64.]

[2]FENG Ni,ZHANG Huixin.Design and application of highspeed acquisition and storage system of telemetry digital video signal[J].Computer Measurement and Control,2013,21(1):279-281 (in Chinese).[馮妮,張會新.遙測數字視頻信號高速采集存儲系統的設計與應用 [J].計算機測量與控制,2013,21 (1):279-281.]

[3]Keron MJ,Gardner FM.Interpolation in PCIE fundamentals[J].IEEE Transaction on Communications,2010,41 (3):501-507.

[4]WANG Jialiang,ZHAO Shuguang.PCI-E Interface implementation and DMA engine design with FPGA [J].Computer Technology and Development,2011,21 (6):181-184 (in Chinese). [王嘉良,趙曙光.用FPGA 實現PCI-E 接口和DMA 控制器設計 [J].計算機技術與發展,2011,21 (6):181-184.]

[5]XIA Hong,HAO Chun’e,YAN Jiangyu.Design and verification of AHB-WISHBONE bidirectional bridge [J].Computer Engineering and Design,2011,32 (6):2201-2204 (in Chinese). [夏宏,郝春娥,閆江毓.雙向AHB-WISHBONE 總線橋的設計與驗證 [J].計算機工程與設計,2011,32 (6):2201-2204.]

[6]ZHANG Yuankai,CAI Huizhi,LIU Yao,et al.High speed storage system based on PCIe and RAID5 [J].Control and Automation Publication Group,2010,26 (12):3-4 (in Chinese).[張元凱,蔡惠智,劉垚,等.基于PCIe和RAID5的高速存儲系統設計[J].微計算機信息,2010,26 (12):3-4.]

[7]SUN Xiaoye.High Speed SG DMA data transmission system based on PCIE [J].Computer Technology and Development,2013,23 (9):195-198 (in Chinese). [孫曉曄.基于PCIE的SG DMA 高速數據傳輸系統 [J].計算機技術與發展,2013,23 (9):195-198.]

[8]LI Muguo,HUANG Ying,LIU Yuzhi.Design of DMA transmission with PCIe bus interface based on FPGA [J].Computer Measurement and Control,2013,21 (1):233-235 (in Chinese).[李木國,黃影,劉于之.基于FPGA 的PCIe總線接口的DMA 傳輸設計 [J].計算機測量與控制,2013,21(1):233-235.]

[9]LI Lisi,CUI Zhihua,YIN Ye,et al.Design and verification of DMA controller of PCIe based on FPGA [J].Computer Measurement and Control,2014,22 (4):1166-1168 (in Chinese).[李麗斯,崔志華,殷曄,等.基于FPGA 的PCIe總線DMA 控制器的設計與驗證 [J].計算機測量與控制,2014,22 (4):1166-1168.]

[10]SUN Tingting,HUANG Jie.Reassemble packets of 3Gcore network based on FPGA [J].Computer Engineering and Design,2010,31 (8):1641-1644 (in Chinese).[孫婷婷,黃杰.基于FPGA 的3G 核心網數據包重組方法 [J].計算機工程與設計,2010,31 (8):1641-1644.]

[11]TIAN Liyu,YUAN Yidan,LI Xiaoyang,et al.Design and implementation of the on-line configurable digital down converter(DDC)based on FPGA [J].Transactions of Beijing Institute of Technology,2013,33 (3):311-316 (in Chinese).[田黎育,袁一丹,李曉陽,等.基于FPGA 的在線可重配置數字下變頻的設計與實現 [J].北京理工大學學報,2013,33 (3):311-316.]