基于FPGA的圓弧插補算法的設計

集美大學信息工程學院 沈旭照 吳一亮

基于FPGA的圓弧插補算法的設計

集美大學信息工程學院 沈旭照 吳一亮

本項目設計了一款基于FPGA的圓弧插補系統。選用京微雅格CME-M7系列的集成了ARM 硬核的高性能開發板,步進最小精度可達0.005mm。圓弧半徑最大可達2.7m,但是由于受到滑臺的自身尺寸的限制,最大的整圓的最大半徑為40cm。插補速度可達3m/min。系統具有較高的集成度和良好的穩定性。

FPGA;圓弧插補;DDA;步進電機

1. 系統設計方案

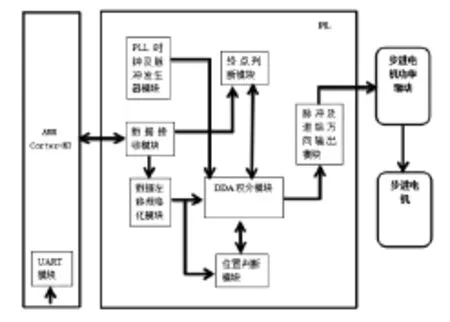

本次選用的是京微雅格CME-M7 系列,該系列是集成了ARM Cortex-M3硬核高性能FPGA,根據設計要求(輸入圓弧起點,終點,半徑,實現勻速和勻加速控制),可以將本次設計DDA圓弧插補功能主要劃分為如圖所示幾個部分(框圖中的路徑為數據路徑,時鐘路徑未畫出)。

2. MCU模塊

該芯片內嵌ARM Cortex-M3硬核,MCU主頻率最高達300M,MCU的時鐘也可由FPGA的PLL端供給,運用MCU高速的運算指令,將圓弧的起點、終點、半徑以及速度控制信號由pc的上位機通過UART串口輸入到MCU,通過一系列算法運算得到該圓弧的圓心位置以及x軸和y軸的總進給數。

本設計的FPGA端的時鐘頻率為50M,ARM核的時鐘頻率為200M,ARM端的時鐘通過FPGA的PLL端配置,但是由于FPGA與ARM核兩部分工作在不同頻域,為了減小亞穩態等現象,本設計采用異步FIFO進行FPGA與ARM核跨時鐘域通信處理,ARM向FIFO中寫入圓心位置以及x軸和y軸的總進給數,待ARM端寫結束后,FPGA向FIFO中讀取數據并送到數據接收端。具體的通信細節是FPGA通過GPIO口向ARM端發送FIFO空狀態,ARM端確認FIFO為空狀態時通過AHB FPGA slave port 1向FIFO中寫數據,FPGA端監測到ARM端寫結束后,開始從FIFO中讀取數據,并驗證每次讀取的數據通過發送PASS或FAIL的信號到LED指示燈。

具體的FPGA和ARM核異步FIFO通信架構如下圖所示。

3. FPGA模塊

3.1 PLL時鐘及脈沖發生模塊

CME-M7系列FPGA擁有資源豐富的PLL資源,8個de-skew全局時鐘,2個支持倍頻、分頻及de-skew 的PLL,ARM核的時鐘也由FPGA的PLL供給。根據DDA插補算法原理,積分器的累加是根據脈沖信號進行的,每來一個脈沖,積分器累加一次,并且根據DDA圓弧插補速度計算公式,合成的速度與源脈沖的頻率是成正比的,所以當脈沖頻率一定時,合成的速度便是勻速運動,脈沖頻率隨時間呈現遞增趨勢時,合成速度便是勻加速運動,所以該模塊首先會用PLL產生一個全局時鐘,供給各個同步模塊,而且還要根據速度控制算法產生頻率固定的均勻脈沖和頻率隨時間遞增或遞減的脈沖。

3.2 數據接收模塊

數據接收模塊接收來自ARM核運算后的數據,包括圓弧的起點,終點,半徑,圓心,x軸y軸各自需要的總進給數,以及速度控制信號和圓弧插補方向信號。

3.3 數據左移規格化模塊

根據圓弧插補改進原理,需要將輸入的圓弧起點(經過運算后的,即起點坐標減去圓心坐標的值)經過左移規格化后送入到被積函數寄存器,本次設計的被積函數寄存器位數定為20位,在程序設計中可以用parameter根據需要靈活定義寄存器位數,因為此時的數值為有符號數,被積函數的最高位為符號位,所以本次設計規格化是使除符號位的次高位為1;因為被積函數是起點坐標減去圓心坐標的值,而且圓弧的起點和圓心坐標都為有符號數,所以圓弧的真正起點坐標為20位有符號數。

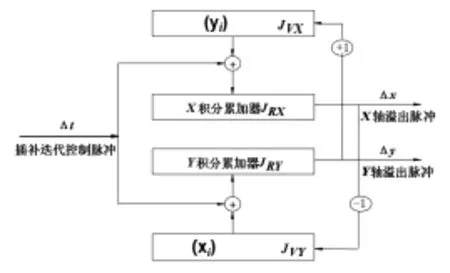

3.4 DDA積分模塊

DDA積分模塊作為本次設計的算法核心,在PLL時鐘及脈沖發生模塊發出的脈沖控制下進行累加運算,這里余數寄存器的位數也為20位,因為余數寄存器中的值為無符號數,所以每次進行累加都是用被積函數寄存器的絕對值進行累加的,當最高位為1時即是發生溢出。發生溢出后最高位清零其余位不變。

DDA圓弧插補算法結構圖如下所示。

3.5 位置判斷模塊

此模塊用于實時的位置判斷,根據動點的位置給出動點所在的象限,根據動點的象限位置給出累加器溢出時的進給脈沖和進給方向,并且需要根據象限相應的修改被積函數值。

3.6 終點判斷模塊

終點判斷模塊開始會從數據接收模塊接收x軸和y軸的各自終點判斷的計數值,然后根據DDA積分模塊每當有累加器溢出時,相應的終點計數值會相應的減一,直到x軸終點計數器和y軸終點計數器都為0時,停止插補,并輸出插補完成信號。

3.7 脈沖及進給方向輸出模塊

在DDA積分模塊累計溢出時,根據位置判斷模塊出相應的盡給脈沖和進給方向,并且修改被積函數寄存器的值。