高精度低功耗12-bit SAR ADC設計

上海交通大學微納電子學系 梁卓君 李永博 楊 曉

高精度低功耗12-bit SAR ADC設計

上海交通大學微納電子學系 梁卓君 李永博 楊 曉

模數轉換器(ADC)是一種將連續物理量(通常為電壓)轉換為代表量化幅度的數字量的器件。隨著電子技術的發展,集成電路成為人類社會的基礎。集成電路大部分為數字電路,而自然界信號為模擬形式,因此ADC的所用十分重要。借由大學生集成電路設計大賽平臺,我們設計了一款12-bit SAR ADC,它擁有低于100μA 的電流消耗和250KB/s的采樣速度。文章還包含了這款ADC的版圖設計。

SAR ADC;低功耗;高精度

一、設計作品整體說明

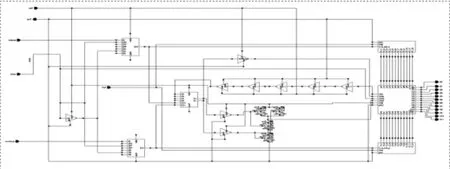

本參賽組的作品為12-bit SAR ADC的設計,ADC主要有四個部分組成:采樣保持模塊(S&H模塊)、比較器模塊(Comparator模塊)、數模轉換器模塊(DAC模塊)、控制邏輯模塊(Control logic模塊)。

圖1 電路頂層模塊的控制及連接關系

我們設計的12bit SAR ADC中,采樣保持模塊采用了互補的柵壓自舉結構,比較器采用了改進的動態比較器結構,DAC模塊采用了共模向下原理的非橋式電容結構,控制邏輯模塊共模向下的異步結構。

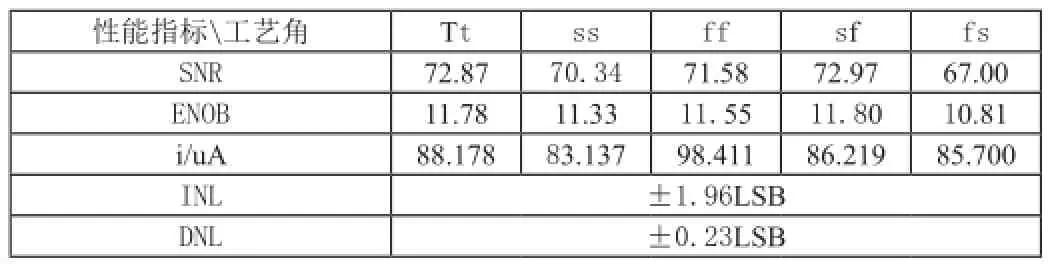

經過前仿,電路在五個工藝角tt、ss、ff、sf、fs下所達到的性能如下表所示,電路性能以SNR(信噪比)、ENOB(有效位數)及i(總直流電流)、INL、DNL來表征。

表1 電路不同工藝角下性能

二、原理圖設計說明,電路圖,仿真波形截圖

根據各個模塊的功能設計原理圖,完成功能性仿真并不斷調整完善。各個模塊的功能介紹、電路結構及前仿波形如下。

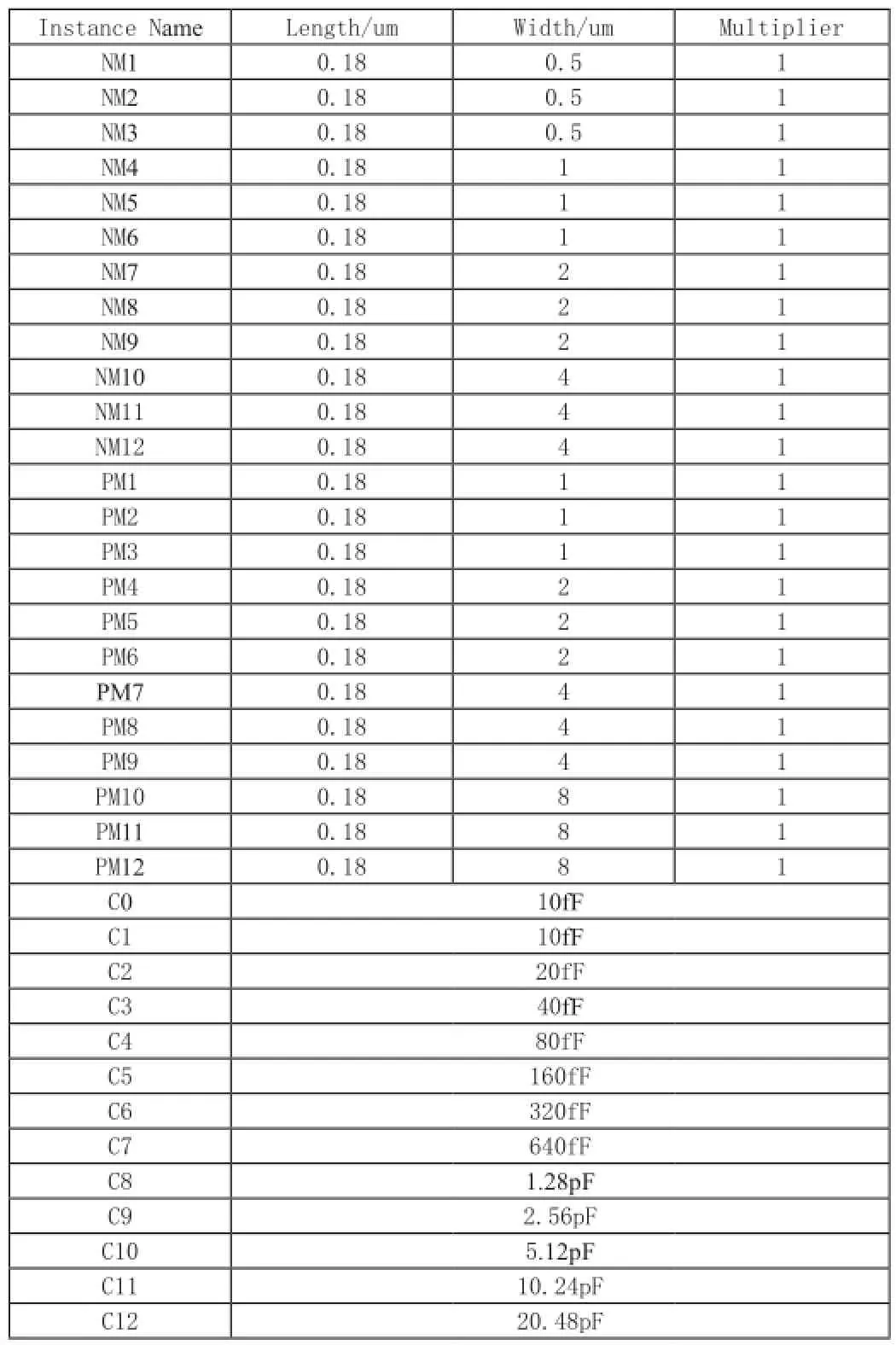

1.采樣保持模塊(S&H模塊)

采樣保持模塊主要完成依據控制信號對輸入信號進行周期性采樣,將采樣后的電平進行保持并輸入到后續的比較器模塊,進行后續的比較與判決。

圖2 采樣保持電路原理圖

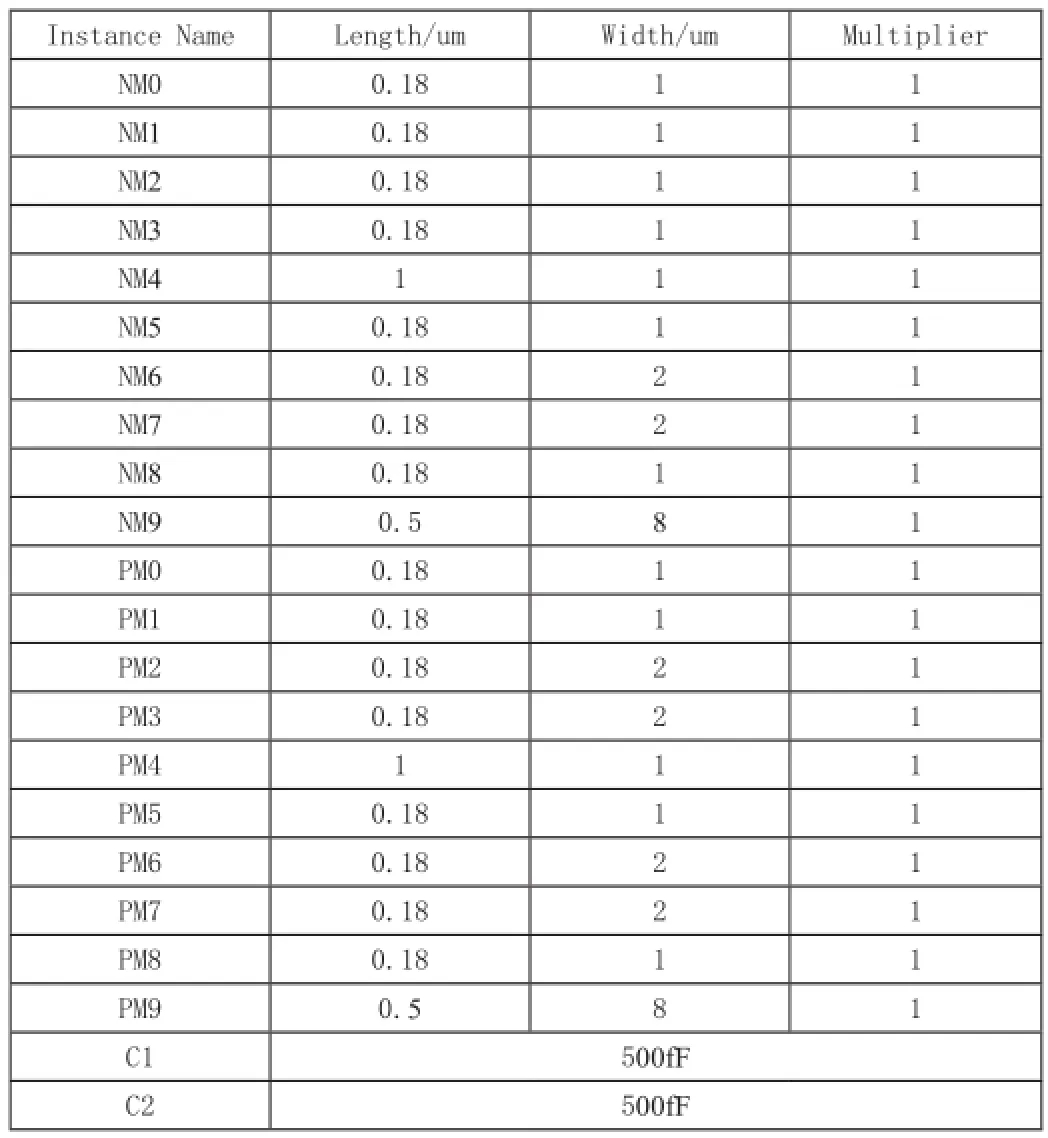

表2 采樣保持電路詳細參數

S&H單測ENOB達到11.5以上,SNR達到70.96以上,電流為2.34uA。

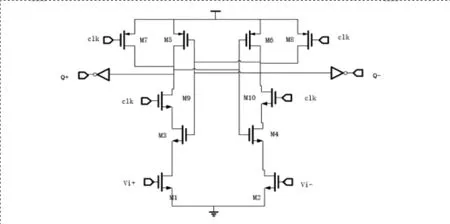

2.比較器模塊(Comparator模塊)

比較器模塊的主要功能是依據控制信號對兩個輸入電平進行比較判決,其主要完成對采樣保持模塊采樣的數據與DAC生成的標準信號進行數次比較,從而達到使其不斷逼近的目的。比較器結構采用了改進的動態比較器結構,功耗較低且比較速度較快,可以在10ns內完成比較。

圖3 比較器原理圖

表3 比較器詳細參數

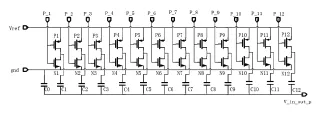

3.數模轉換器模塊(DAC模塊)

數模轉換器模塊主要功能是依據控制信號提供的12-bit數字位數,通過一系列電容陣列將數字信號轉換成模擬信號,并將模擬信號輸入到比較器中進行比較與判決。

圖4 數模轉換器模塊原理圖

表4 數模轉換器詳細參數

上述電容的實現中,由于0.18工藝的限制,小電容采用電容串聯的方式實現,大電容采用電容并聯的方式實現。

4.控制邏輯模塊(Control Logic模塊)

控制邏輯模塊是SAR ADC中最重要的模塊之一,它連接著其他的所有模塊,控制著整個電路的時序與邏輯。控制邏輯模塊通過一系列的控制信號控制著采樣保持模塊、比較器、數模轉換器的通斷與時鐘周期,在每一個采樣周期內,它通過對比較器的輸出結果進行判決,在下一個時鐘周期生成一個新的DAC輸入信號與采樣的信號進行比較,從而使得輸入的模擬信號能夠一步步逼近理想的數字信號。本次控制邏輯模塊采用異步邏輯結構,相比同步邏輯結構擁有更快的處理速度和更低的功耗。控制DAC的方式采用共模向下,這樣的目的也是為了進一步減小功耗。

圖5 控制邏輯模塊原理

表5 控制邏輯模塊詳細參數

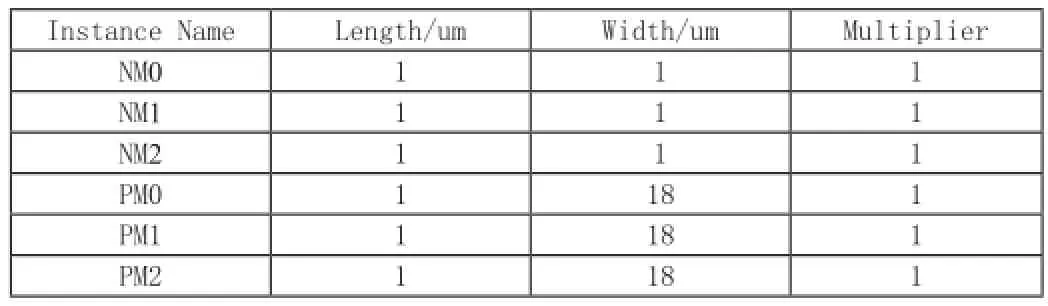

控制邏輯模塊中最關鍵的子模塊是DFF的搭建。

圖6 DFF模塊原理圖

表6 DFF模塊詳細參數

5.系統整體仿真

圖7 電路原理圖

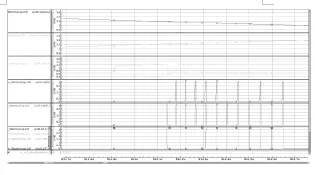

圖8 前仿結果

其中,第1,2行的信號表示差分輸入的兩個信號電平值,這兩個信號值經過采樣保持電路的采樣后輸入比較器中,與DAC的輸出值進行比較與判決,比較器的結果輸入控制邏輯模塊中進行進一步的判決并生成下一個周期的控制信號。

圖9 放大后的前仿波形

放大后的波形圖可以比較清晰地看出每個周期中信號的變化關系。第3行信號表示每個周期后信號的變化關系,從圖中可以看出,隨著時間的推移,兩個信號不斷逼近,這樣經過12個周期后,采樣的模擬信號最終轉化為數字信號,此波形體現了SAR ADC的工作模式。第4行信號表示比較器的輸出結果,與第三行信號相對應,若正輸入端信號大于負輸入端信號,則比較器輸出為1,反之輸出為0。

將前仿波形進行采樣并輸出到MATLAB中進行處理,可以算出各個工藝角下的電路性能。電路性能用SNR(信噪比)、ENOB(有效位數)、i(總直流電流)、INL、DNL來表示,將各個電路性能參數匯總如表7所示:

表7 電路性能參數

對SAR ADC輸出的數據進行分析,將其波形還原后的頻譜圖如圖10所示。

圖10 SAR ADC波形還原頻譜圖

為了方便計算和操作,采樣頻率為250k,同時為了符合采樣公式,對輸入頻率進行了修改為97.9004k 近似100K 對結果不會有很大影響。通過頻譜圖可以看出,還原后的波形的頻率就在97K左右。

圖11 DNL結果

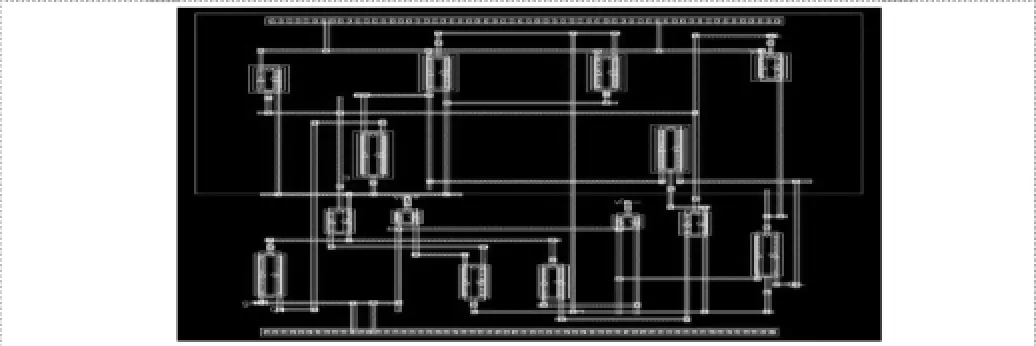

三、版圖設計說明

1.采樣保持模塊(S&H模塊)

S&H電路中有兩個晶體管的body端需要連接到drain端,較為特殊。其中的NMOS需要置于deep N-well中,PMOS由于body電壓不是VDD,不能與其它PMOS放于同一個N-well中,也需要單獨放置。

圖12 采樣保持電路版圖

2.比較器模塊(Comparator模塊)

比較器模塊的電路中,PMOS和NMOS分列上下兩半,因此畫版圖的過程中將PMOS和NMOS上下排列,便于繪制n-well:

圖13 比較器版圖

3.數模轉換器模塊(DAC模塊)

DAC模塊電路采用了單位電容改變Multiplier的數值以改變電容值。從兩個單位電容串聯形成最小電容開始,到16個Multiplier為64的單位電容并聯而成最大的電容,因此在繪制版圖時,以64個單位電容為一行,根據需要,將行與行之間并聯達到所需要的電容值。這樣便于將DAC模塊畫成正方形。

圖14 數模轉換器版圖

4.控制邏輯模塊(Control Logic模塊)

控制邏輯中的與門、D-Flip-flop和延時單元采用封裝后的模塊,這樣可以實現相同單元的復制,從而減少版圖繪制的復雜度。

圖15 控制邏輯版圖

圖16 與門版圖

圖17 D-Flip-Flop版圖

圖18 延遲單元版圖

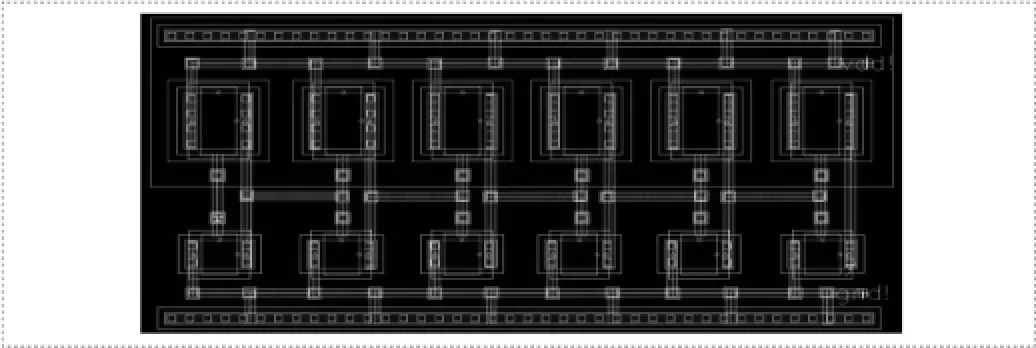

5.版圖整體

版圖面積:2572*779 um2。

圖19 版圖整體結構

四、DRC&LVS 報告

1.DRC檢驗

采用CSMC018_mixRF_sali_m6_argusDRC.rul規則文件進行檢驗,只有density錯誤出現,可以后期加dummy解決,故視為檢驗正確。

圖20 DRC檢驗結果

2.LVS檢驗

采用CSMC018_mixRF_sali_argusLVS.rul規則文件進行檢驗,檢驗結果通過。

圖21 LVS檢驗結果

五、創新點及實用性

采樣保持電路采用柵壓自舉結構,保證開關晶體管電導的恒定,并且采用傳輸門互補結構,抵消溝道電荷注入效應和時鐘饋通效應的影響,從而使得電路功耗較低,精度較高。為了達到低功耗的要求,控制邏輯模塊特地采用了異步結構而不是同步結構,同時,DAC模塊也采用了共模向下而非共模不變的方式。同時,我們設計了一種特殊的延時單元,由四個特殊參數的反相器構成了8ns的延時,從而滿足各個模塊之間的配合。同時,比較器模塊采用了優化的動態比較器結構,能在很短的時間內比較出結果,并且精度較高。

六、設計過程總結

設計的開始階段,我們查閱了很多關于SAR ADC的論文文獻,了解了SAR ADC的基本原理與工作模式;隨后我們依據所查閱的資料結合所學理論知識將整個SAR ADC電路分為采樣保持模塊、比較器模塊、數模轉換器模塊、控制邏輯模塊四個部分,分別搭建了這些子模塊的電路并將這些子模塊組合成一個整體電路進行功能仿真,在仿真過程中遇到的問題需要我們對各個子模塊的邏輯與時序關系進行一系列的調整,也使我們對整個電路協同工作的模式與整體功能的運作更加熟悉;經過無數次的仿真與修改,獲得了最優的電路原理圖之后,我們用Aether軟件進行版圖的繪制,一開始版圖出現了很多雜亂的錯誤,經過認真的學習與研究,我們一步步克服了問題,最終完成了整個12-bit SAR ADC的設計。

[1]Franco Maloberti,Data Converters,Xi AN JIAOTONG UNIVERSITY press.2013.7.1

[2]W. Miaorong, “A 9 ENOB 43 MS/s and A 9.12ENOB 26 MS/s 10-bit SAR ADC in 0.18um”, Shanghai Jiao Tong University, June. 2015.

[3]Geng Wenliang, “Analysis and Realization of Low Power ADC for Biological Signal Acquisition”, Shanghai Jiao Tong University, Jan. 2014.

[4]Qiulu Liang,10-bit High Precision Low Power SAR ADC Design Research [D].Beijing Jiao Tong University,2014.

[5]Le Hao, Design of 12-bit SAR ADC Based in Low Voltage and High Precision [D].Beijing Jiao Tong University, 2008.

[6]Chonglin Tang, Structure Design and Control Technology of Ultra-low Power SAR ADC [D].Xidian University, 2008.

[7]Fule Li,Design of Successive Approximation ADC,Tsinghua Microelectronic department, 2012.

[8]Tianting Zhao,CMOS 12-bit 125ksps fully differential SAR ADC [D].Nankai University, 2004.

[9]Yintang Yang,Xingyuan Tong,Zhangming Zhu,Xuguang Guan, A 10-bit 200kS/s 65nm CMOS SAR ADC IP Core[J].Journal of Electronics & Information Technology,2010,12:2993-2998.

An analog-to-digital converter (ADC) is a device that converts a continuous physical quantity (usually voltage) to a digital number that represents the quantity’s amplitude. With the development of electronic technology, integrated circuits become the base of human society. Because most of the integrated circuits are digital, while the natural signal is analog, the ADC plays an important role. We designed a 12-bit SAR ADC with a current consumption under 100μA and a sampling rate of 250KB/s. The layout of this SAR ADC is included.

SAR ADC, low power consumption, high accuracy