基于S3C2440的存儲器接口設計與初始化分析

黃飛翔 蔡啟仲

【摘 要】在嵌入式系統設計中,SDRAM的工作原理、控制時序及相關寄存器配置方法,相對較難。本文基于三星公司的S3C2440微處理器,設計外接美光內存芯片MT48LC16M16A2,并詳細分析了初始化代碼,目的是加深初學者對SDRAM的基礎知識的了解,能有助于今后的嵌入式學習以及設計提供參考。

【關鍵詞】SDRAM;存儲器;S3C2440

0 引言

制造商所生產的MCU片內存儲器空間往往不可能完全滿足所有的嵌入式系統應用設計,例如,AT89S51單片機的內部RAM大小為128字節。因此,對于需要較大片內存儲空間的應用設計來說,擴展片內存儲器空間是非常重要的。

1 硬件設計

1.1 三星S3C2440微處理器

1.1.1 S3C2440硬件資源

S3C2440是三星公司開發的一款基于ARM920T內核的16/32位RISC微處理器,集成的系統外設和接口有:1.8V內核電壓,3.3V存儲電壓,3.3V I/O電壓;16KB的指令高速緩存、16KB的數據高速緩存和存儲管理單元;外部的存儲控制器(SDRAM控制器和片選邏輯);LCD控制器,包括一個LCD DMA;4個帶外部請求管腳的DMA;3個UART,2個SPI;1個I2C總線控制器,1個I2S-BUS控制器;SD主機接口;4個PWM時鐘和1個內部時鐘;看門狗時鐘;117個GPIO,24個外部中斷源; 8路10位 ADC和觸摸屏接口;帶ALARM功能的RTC;帶PLL的片上時鐘發生器;NAND Flash控制器。

1.1.2 存儲器系統

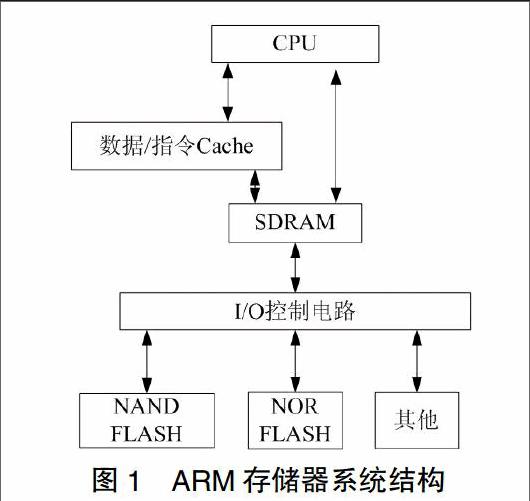

ARM存儲器系統由各種類型的存儲器按照一定的層次結構組合成[3],如圖1所示。

SDRAM在存儲結構中用做程序的運行空間,它在響應控制輸入前會等待一個時鐘周期,將CPU和RAM之間的速度進行匹配,加快了數據傳輸速度。

1.1.3 S3C2440的地址空間

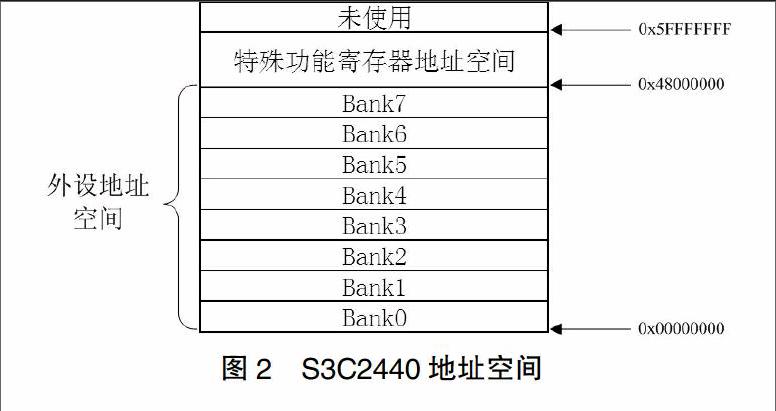

S3C2440是一款具有32位的地址總線和數據總線寬度的CPU,實際上只指引出了27根地址線,最大尋址空間為128MB。8個Bank分別對應S3C2440的8個片選信號線nGCS0~ nGCS7相互區別,可以做到總的尋址空間為8*128Mb=1GB。

S3C2440地址空間[4]如圖2所示,SDRAM需接在S3C2440的Bank6或Bank7上。

1.2 SDRAM存儲器MT48LC16M16A2

1.2.1 MT48LC16M16A2概述及特性[5]

MT48LC16M16A2是一款256Mb高速CMOS SDRAM,容量為256Mb,結構為4 x 4M x 16bits,16位位寬,兼容PC100、PC133,3.3V供電電壓,自動預充電,刷新時間為8192/64ms。

1.2.2 SDRAM讀寫時序

S3C2440對SDRAM的基本讀操作和寫操作均需要控制線與地址線相互配合。

SDRAM基本讀操作過程如下:

(1)發出Bank激活命令(必須大于RAS到CAS的延遲指標Trcd),并鎖存響應Bank的行地址與列地址;

(2)CL(CAS延遲值)個時鐘周期后,先指定行地址再指定列地址數據即可出現在數據總線上;

(3)向SDRAM預充電命令(PRECHAREG)以關閉激活頁,等待Trp時間,即可進行下一次讀、寫操作。

SDRAM基本寫操作過程如下:

(1)發出Bank激活命令(要求同前),并鎖存響應Bank的行地址與列地址;

(2)寫入數據依次出現在數據總線上;

(3)寫入最后一數據后延時Twr時間,向SDRAM預充電命令(PRECHAREG)以關閉激活頁,等待Trp時間后即可進行下一次讀、寫操作。

1.3 接口電路設計

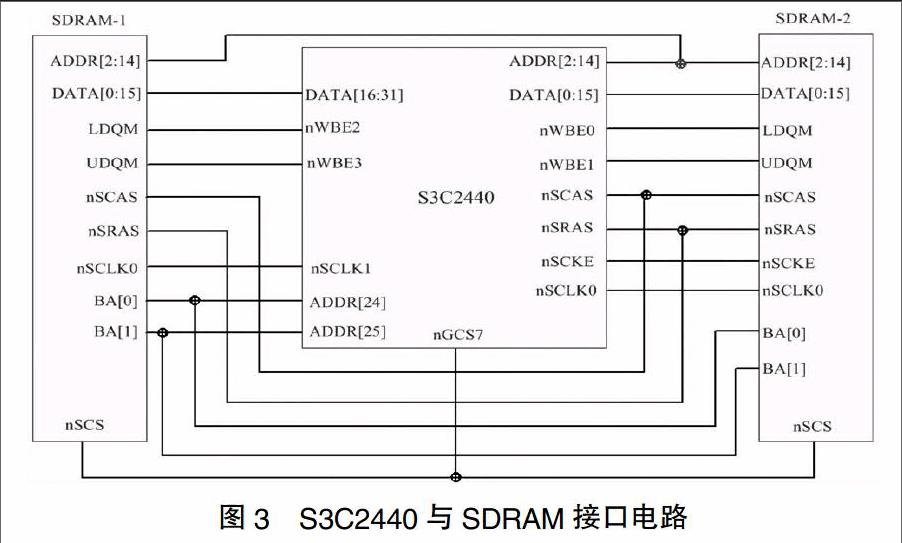

采用兩片MT48LC16M16A2并聯組成32位的位寬,它們與S3C2440的接口電路設計如圖3所示。

2 寄存器配置及SDRAM初始化分析

2.1 寄存器配置

Bank7不僅可以像Bank0~Bank5一樣支持ROM和SRAM,還可以外接SDRAM,因此除了需要像Bank0~Bank5一樣設置相應的總線帶寬\等待控制寄存器BWSCON和總線控制寄存器BANKCON7外,還需要根據MT48LC16M16A2數據手冊中的參數(例如Trp、Trc、Trcd和Trp等)來對刷新控制寄存器、存儲塊大小控制寄存器和模式設置寄存器的相應位進行配置,從而使得內存控制器可以產生相應的時序。假設系統的HCLK為100MHz(即時鐘周期為10ns),則各寄存器概述及根據SDRAM芯片時序的配置(未配置的位保持默認)如下:

(1)總線帶寬\等待控制寄存器(BWSCON)各位如下:

ST 啟動/禁止SDRAM的數據掩碼引腳,對于SDRAM,該位置0;

WS 是否使用存儲器的WAIT信號,通常置0為不使用;

DW 兩位,設置位寬(00=8bit、01=16bit、10=32bit、11=保留)。

(2)總線控制寄存器BANKCON7各位如下:

MT([16:15]):配置為0x03將Bank7映射的物理內存為SDRAM;

Trcd([3:2]):行地址到列地址的延遲時間設置為0x0,因為Trcd[5]=20ns(即2倍時鐘周期);

SCAN([1:0]):SDRAM列地址位數設置為0x01,因為本設計所采用MT48LC16M16A2的列地址數為9。

(3)刷新控制寄存器REFRESH

REFEN([23])設置為1,即啟用SDRAM刷新功能;TREFMD([22])設置為0,即選用自刷新模式;TRP([21:20])根據Trp[5]=20ns設置為0x00,即兩個時鐘周期;Tsrc[19:18](SDRAM半行周期運行時間),SDRAM的行周期運行時間滿足Trc=Tsrc+Trp,因為Trp[5]=20ns(2個時鐘周期),Trc[5]=66ns(7個時鐘周期),所以Tsrc為5個時鐘周期,即將Tsr([19:18])設置為0x01;MT48LC16M16A2刷新8192行的總時間為64ms,則單行刷新時間為7.81μs(64ms/8192),再由公式(單行刷新時間=211-SDRAM工作頻率(MHz)×刷新計數器值+1)計算得Refresh Counter([10:0])=0x4f4。

(4)存儲塊大小控制寄存器BANKSIZE

BK76MAP([2:0])配置為0x001,因為本設計外接64MB的SDRAM。

(5)SDRAM模式設置寄存器MRSRB7

CL[6:4] 配置為0x011,因為Tcl[5]=2.5ns(需3倍時鐘周期)。

2.2 設計并分析SDRAM啟動代碼

首先在xxx.inc文件中對下列常量進行定義。

其次,初始化文件中包含了xxx.inc文件,就可以在其中使用上述變量了,如下:

通過以上部分代碼,即可完成對SDRAM存儲器的初始化。

3 總結

本次設計介紹了S3C2440與SDRAM硬件接口的設計及相關寄存器的配置過程,為嵌入式系統設計提供了一定的學習和設計參考。

【參考文獻】

[1]王波波,王琤,等.ARM完全學習手冊[M].北京:化學工業出版社,2012.

[2]黃智偉,鄧月明,王彥.ARM9嵌入式系統設計基礎教程[M].北京航空航天大學出版社,2008.

[3]奚海蛟,諶利,呂鐵軍.ARM體系結構與外設接口實戰開發[M].北京航空航天大學出版社,2012.

[4]王小強,方鵬,粟思科.ARM處理器裸機開發實戰—機制而非策略[M].電子工業出版社,2012.

[5]MT48LC16M16A2說明書[S].

[6]S3C2440數據手冊[S].

[7]陳學立,邱兆坤,陳志勇.嵌入式處理器與SDRAM的接口設計與實現[J],現代電子技術,2010(2).

[責任編輯:湯靜]