多級運放穩定性研究

張楊俊杰 中船重工昆明船舶設備研究試驗中心 650034

多級運放穩定性研究

張楊俊杰 中船重工昆明船舶設備研究試驗中心 650034

本研究基于0.5 um CMOS工藝,將一個二級運算放大器設計在SV電壓下,其放大倍數達到了81.29 dB,在對電路進行補償時使用了密勒補償法,達到了64度的相位裕度,將cascode連接結構應用到偏置電路中,從而對偏置穩定性加以保證,此外還將差分輸入應用到輸入級,促使電路抗干擾能力得到增強。

反饋補償;運算放大器;高興算計算

引言

在數模混合信息系統或模擬系統中,運算放大器是一個重要部件,運算放大器的應用涉及到眾多領域[1],比如采樣保持電路、有源濾波器、波形發生器、模擬轉換器等等。通過復雜性各異和機構不同的運放能夠使多種功能得以實現[2];對于運算放大器來說,從偏值的產生到濾波或放大,其兩大重要因素均為穩定性和增益[3],運放電路結構決定了這兩方面的因素。同時優化這兩個方面可能會發生沖突,采用多級級聯的辦法能夠使放大倍數更高,然而多級運放需要引入多個極點才能實現高增益,而這卻會顯著惡化運放的穩定性。在輸入和輸出間采用調零電阻和添加償電容的辦法能夠調節單位增益帶寬以及相位特性[4]。本電路將由電阻構成的RC密勒補償與補償電容增加至第二級的輸入和輸出間。補償電容的作用在于對電路的極點進行調節,從而對增益帶寬進行調節。補償電阻的作用在于對電路的零點進行調節,進而對相位特性進行調節。

1.電路實現

CMOS二級運算放大器主要含有:輸入級放大電路、偏值電路、補償電路和二級放大電路。

偏值電路的組成包括電阻R1與晶體管M8-M13。M8與M9是一對匹配的pmos鏡像電流源,具有相同的參數。將電阻R1串聯到M12上,將會使M12與M13這兩個晶體管失去匹配。偏值電流Ⅰ1的大小取決于電阻R1。M11和M13以二極管形式連接起來,負責將偏值電壓提供給cascode連接的M10,此種cascode結構能夠使由溝道長度調制效應所導致的電流誤差得以減少。

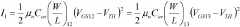

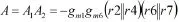

在M8與M9鏡像電流源的作用下,相等的電流I1通過M12和M13,可表達為:

然后根據電路結構得出:

而偏值電流即可由此得到:

由上式可知,M12與M13這兩個晶體管的尺寸和R1電阻的阻值與I1關系密切,而后者并不會被電源電壓所影響。所以在對偏值電流的大小進行調節時,可以采取調節M12與M13晶體管的尺寸和調節R1電阻阻值的辦法。

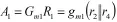

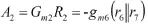

其第二級位的電壓增益如下:

因此可將總的放大倍數表示成:

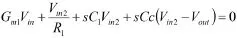

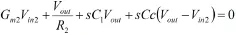

根據等效電路能夠獲得兩個如下的KCL等式:

公式(1):

而電路的傳輸函數如下公式(1)表示:

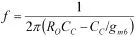

將一個電阻串串接到第二級的輸入與Cc之間,能夠對阻值的大小進行調節,從而實現對零點的調節。系統函數在串聯之后并不會出現變化,可以將零點表示成:

2.仿真結果

cadence中的spectre仿真的相頻特性與幅頻。仿真結果基本吻合相關理論,達到了64度的相位裕度和81.29dB的增益。

其單位增益達到26.74MHz的帶寬。在模擬集成電路中,運算放大器的作用非常重要,它對電路的整體性能起著決定性的影響。現代集成電路產品多追求低壓低功耗表現,運算放大器的電源電壓要想得到降低,就必須對集成電路的特征尺寸進行減小。關于運算放大器的研究,目前仍以兩級運算放大器為主,很少有人研究多級運算放大器。采取傳統的兩級運算放大器能夠使設計要求得到滿足,能夠實現100dB以上的增益,具有相對穩定的補償結構,在對傳統密勒補償結構的應用下,能夠達到約60度的相位裕度。工藝技術在不斷發展,極大的減小了器件特征尺寸,集成電路設計也隨之邁入深亞微米量級,逐漸凸顯其短溝道效應,溝道擊穿造成了電壓的降低,而晶體管則會減小其本征增益,與電源電壓的降速相比,晶體管閥值電壓的降低速度要低得多,這將會急劇減小放大器的直流增益,從而給電路性能造成非常嚴重的影響。在此種情形下,設計要求已經不能通過兩級運算放大器得到滿足,因而必須借助多級放大器展開級聯,從而確保增益的充分提供,在閉環工作下放大器的線性度也應得到保證。目前在深亞微米量級中,研究的重點已經逐漸放在了三級運算放大器之上。

3.結束語

本文在對二級運算放大器進行設計時應用了密勒補償,也就是將補償電阻與補償電容串聯到輸入級與輸出級之間。不僅促使增益獲得提高,而且還使運算放大器的單位增益帶寬得到了增加,此外,還提供了60度以上的相位裕度,從而使電路的穩定性得到保障。

[1]劉輝.低壓低功耗CMOS運算放大器的設計[D].成都:電子科技大學,2002.

[2]易清明,張靜,石敏.低功耗CMOS集成運算放大器的研究與設計[J].微電子學,2007, 37(3):11-16.

張楊俊杰,男(1992-),云南昆明人,民族:漢,學歷:大學本科