FPGA與PCM—9575嵌入式計算機異步通信的設計與實現

摘 要:短波發射機自動調諧系統采用FPGA與嵌入式計算機來實現各自的功能,其中他們之間的異步通信的設計是很重要的環節,其實用性、可靠性是需要考慮的主要方面,文章介紹利用ISE設計平臺采用層次化設計方式實現二者之間的通信,取得了良好的效果。

關鍵詞:異步通信嵌入式主板;FPGA;RS232;HDLC;FIFO

1 概述

短波(3.9MHZ-26.1MHZ)發射機更換工作頻率時為了保證發射機能正常工作在所需的頻率值,必須使高頻回路各個調諧器件在步進電機的帶動下轉動到相應的頻率的位置上。TBH522型150KW短波發射機數字化自動調諧系統采用XC2S200設計實現對8路步進電機位置的采集、轉動控制、及其他邏輯控制功能;使用臺灣生產的PCM-9575嵌入式主板實現與上位機通信、調諧頻率數據庫的存儲、發射機模擬量采集、人機對話界面等功能。由于該嵌入式主板有現成的RS232接口,我們對FPGA設計異步通信宏模塊,實現其與嵌入式主板通信,通信方式采用國際標準電子工業聯合會(EIA)定制的RS232標準,通信協議采用的是高級數據鏈路控制協議(HDLC)協議,負責傳送步進電機的預置位置、實際位置、鍵盤數據、頻率以及一些控制命令等數據。

2 FPGA異步通信總的設計思想

RRI和TRO為異步通信輸入輸出引腳,嵌入式計算機COM口設置為9600波特率、1位奇偶校驗位、1位停止位。CLK為系統時鐘16MHz。

LOAD信號只在接收到實際位置的時候維持大約4us的高電平,在其他狀態為低電平,在高電平時將步進電機實際位置計數器置數,低電平時步進電機實際位置計數器計數。

發送程序啟動時,不斷掃描8路地址的總線,從第1路到第8路連續發送8幀數據,然后再重新掃描。

接收程序接收到數據后將數據鎖存到總線上,內部設有差錯處理功能,當幀結構不正確或一幀數據不完整將不會把數據送到總線上。

2.1 層次化設計

異步通信模塊涉及到的RS232通信標準和HDLC協議控制都比較復雜,從通信的層次來說,RS232數據底層的通信協議,HDLC協議控制數據高層協議控制,當完成了底層的RS232通信的設計后,高層協議HDLC只需要按照其協議規定的數據格式調用底層的通信協議將一幀數據發送出去即可。在接收時,接受完一幀數據后,在按照協議規定的數據格式將數據“剝離”開,在按照數據的地址分配到相應的總線上即可。

2.2 數據處理的要求

從本設計的需求來說,異步通信模塊與嵌入式計算機通信的數據量并不是很高,與嵌入式計算機通信所定義的HDLC協議也十分簡單,沒有規定過多的應答數據;硬件上也采用SPI的3根線,即接收、發送和地線,沒有其它的應答信號。異步通信模塊與嵌入式計算機通信是一個被動的過程,在這種情況下,可以想象,嵌入式計算機向FPGA發送數據在時間上具有一定的隨機性,可以發完一幀數據后馬上發送下一幀數據,或者等待一段時間后再發送一幀數據,而FPGA接收數據是以幀為單位進行接受,即每次接受一幀數據送入緩存器中,然后將緩存器中的數據進行處理,處理完畢后再接收下一幀數據,而對于這種被動的接收勢必對處理的速度有很高的要求,即接收到一幀數據后,迅速將數據讀出,清空緩沖區,等待下一幀數據的到來。

在發送上也采取這種策略,將所要發送的數據迅速裝入緩沖區,做到不影響發送數據的連貫性。

為了提高讀寫速度,緩沖區采用同步先入先出堆棧(fifo),不用送地址,只要將讀、寫信號有效,然后送時鐘信號即可進行數據的高速度寫。

為了保持數據的可靠性,在接收上要做一定的差錯控制。

3 內部模塊設計與實現

異步通信模塊主要由發送部分和接收部分組成,設計利用ISE平臺實現,全部采用VHDL語言完成每個子模塊的設計。

3.1 發送部分

發送模塊功能是將8路步進電機實際位置的總線上的數據按照HDLC協議通過串行通信發送到嵌入式計算機中。主要包括復位電路模塊(reset_core)、發送控制模塊(transtmit_ctrl)、波特率分頻模塊(fen)、HDLC協議控制時鐘分頻模塊(FEN_HDLC)、先入先出堆棧(FIFO_T)、HDLC協議控制模塊(TX_HDLC)、異步通信發送模塊(UART_T)等7個模塊。

3.1.1 reset_core模塊

該模塊負責在上電后維持1μs的高電平,將內部工作的所有模塊中的狀態機復位,然后維持低電平,讓內部模塊開始工作。

3.1.2 transtmit_ctrl模塊

此模塊的功能是將8路步進電機的實際位置循環掃描寫入到FIFO_T堆棧中,特點是:(1)快速寫入數據,采用系統時鐘16MHz,用5個周期完成一個數據的寫入。相對于9600波特率的異步通信來說,此速度能夠保持發送數據的連貫性,保證系統的實時性。(2)寫入FIFO_T中的數據格式按照先后為:地址位——數據位高字節——數據位低字節。(3)利用狀態機控制,并且在控制上采用控制信號和數據傳輸與處理分開,利用狀態機組合進程產生控制信號,在其它進程利用前者產生的控制信號控制數據的傳輸與處理,確保數據傳送有足夠的建立時間和保持時間,保證數據的穩定和可靠。此狀態機充分考慮了和其他模塊之間信號的通信,數據穩定的建立、保持時間。完成后的狀態機將要發送的數據送到了深度為3個字節的FIFO模塊中,并且控制HDLC模塊將數據讀出發送出去。(4)狀態機組合邏輯進程,該進程在各個控制信號定義是盡量保持控制信號只在一個狀態有效,避免狀態轉換過程中出現毛刺。在此進程中并沒有進行數據的傳輸,只是通過狀態的轉換送出控制信號。(5)描述鍵盤狀態緩沖器信號進程。在上一個進程中可以看到,當鍵盤狀態緩沖器為低電平時,地址指向鍵盤地址,此時若模塊處于向堆棧數據過程中,很容易將先前的數據覆蓋,所以該信號應該保證在寫堆棧到來期間無效,并且在完成后聯合調試過程中發現,每次按鍵應該保證只向嵌入式計算機發送一次數據,多次發送將會引起嵌入式計算機的誤動作。該進程的功能就是使得每次按鍵后在等待發送數據過程中將鍵值捕獲,然后保證只發送一次。(6)鍵盤狀態寄存器描述進程,該進程是用鍵盤到來信號緩沖器來鎖存鍵盤狀態寄存器,使得數據能夠保持一個完整地寫周期。(7)數據選通進程,由地址來控制,負責將各路數據送到緩沖器中。各個進程之間利用信號來傳遞,互相協調工作,是一個完整的統一體,由寫信號作為預留,在需要時可以進行擴展和添加。

3.1.3 fifo_t模塊

此模塊是一個深度為3個字節的同步FIFO(先入先出堆棧),用來將地址、高字節數據、低字節數據寄存。

由于此模塊為一個同步FIFO,而本設計中的讀寫是分開的,讀寫的速度也不相同,寫的時候要求高速寫入,不影響通信的連貫性,讀的時候根據發送模塊的速度來讀取數據,所以讀、寫時鐘用兩個模塊中的狀態機產生,為了不產生沖突,兩個模塊在空閑狀態將時鐘送出低電平,然后將兩個始終用一個或門連接,送入FIFO中進行控制。

3.1.4 Tx_HDLC模塊

該模塊主要負責以下幾個功能:

(1)FIFO的讀操作。將FIFO中的地址、高位字節數據、低位字節數據讀出來。(2)HDLC協議的控制。包括產生幀頭、幀尾數據(7E)附到數據流上,產生CRC校驗多項式,將多項式的結果附到數據的尾部。(3)發送數據控制。利用狀態機控制發送程序,將處理好的一幀數據發送到嵌入式計算機上。

模塊特點:

(1)流水線作業,將FIFO中的數據讀出來后進行并-串轉換,將串行數據用流水線進行CRC運算,然后再進行串-并轉換將數據發送出去。(2)利用程序計數器進行時序控制,控制流水線的操作。(3)利用狀態機控制發送程序,并且控制和數據傳送分開,保證數據傳送有足夠的建立時間和保持時間。(4)增加數據鎖存語句,使得每次處理完的數據都能夠穩定一段時間,增強數據的可靠性。

3.1.5 異步通信發送模塊

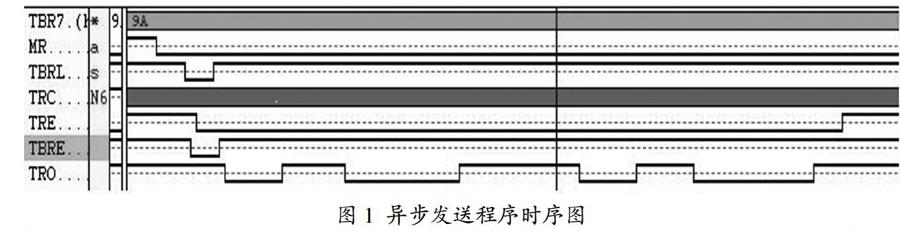

采用波特率為9600,數據為8位,偶校驗方式發送數據,發送時序為:

(1)腳至為低電平,此時內部狀態標志復位,將TRBL置為高電平。(2)將數據送入端口準備好,將TRBL信號置為低電平,此時TRE引腳邊為低電平,裝入數據,開始傳送。(3)RBL置為高電平,等待數據發送完成后,輸出引腳TRE變為高電平。

3.2 接收部分

接收部分實現的功能是將嵌入式計算機發送過來的步進電機預制位置、實際位置等數據送入相應的數據總線上。嵌入式計算機通過COM口發送數據,通信協按照HDLC協議,根據發送數據的格式規定,該部分主要由接收數據模塊(UART_R),接收控制模塊(UART_CTRL),先入先出堆棧(FIFO)模塊,檢錯控制模塊(MONITOR),數據控制模塊(MCU),裝載信號延時模塊(LOAD_DELAY)。

接收過程將一幀數據中的有效數據按照規定送到相應的數據總線上。工作流程如下:

(1)UART_R負責接收上位及發送過來的數據,每次接受一個字節。(2)接收過程受UART_CTRL控制,由UART_CTRL內部的狀態機形成的時序來控制UART_R模塊,然后將接收到的1幀數據寫入FIFO。(3)MCU模塊負責協調整個系統的工作,包括所有模塊的初始化,數據控制,當檢測到FIFO中的數據被寫滿,則將一幀數據從FIFO高速讀出,高速讀出是為了不影響數據的接收,然后按照地址將數據分配到相應的總線上。(4)數據接收需要差錯控制,幀數據不完整和不同步都視為錯誤數據,由內部邏輯和MONITOR產生控制信號。

3.2.1 接收數據模塊(UART_R)

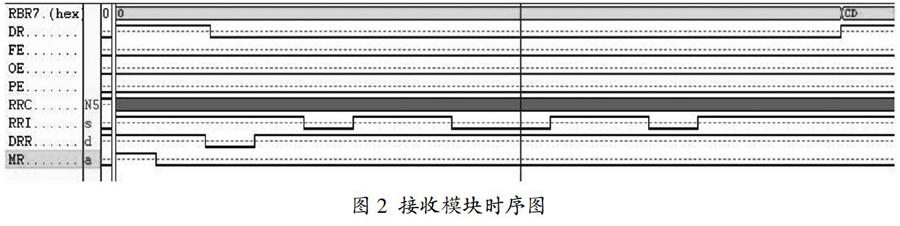

MR為高電平時,將模塊內部寄存器復位;MR為低電平時,啟動整個模塊,此時應將DRR置成低電平,將輸出引腳DR置為低電平,然后再將DRR置為高電平,開始接收數據。接收數據按照9600的波特率,數據接收完畢后DR送出高電平,RBR[7..0]輸出接收到的數據。時序圖如圖2所示。

3.2.2 接收控制模塊(UART_CTRL)

接收控制模塊負責啟動接收模塊接收嵌入式計算機發送過來的數據,并將數據寫入FIFO堆棧中。該模塊受MCU模塊控制,并和器協調工作,主要操作即是對FIFO的讀寫。該模塊沒有任何的總線傳輸,只是靠狀態機控制一些輸入輸出信號控制接收模塊和先入先出堆棧之間的數據通信。

3.2.3 檢錯控制模塊(MONITOR)

在接收模塊工作期間,MCU讀FIFO是采用16M時鐘控制,高速讀取是為了不影響數據的接收,每來一幀數據,MCU模塊會迅速將FIFO中的數據讀空,使得FIFO的外部信號EMPTY,迅速處于高電平,也就是說,在接收到完整的一幀數據的情況下,EMPTY信號會形成一個短暫的高電平,當通信出現問題,上位機還為發送完一幀數據就停止數據的發送,這時UARTR_CTRL將會繼續等待數據的到來,FIFO輸出的EMPTY信號也一直維持低電平,造成通信惡化,解決辦法即是加入了此模塊進行控制。

此模塊相當于一個看門狗定時器,外部信號只有3個,EMPTY,CLK為輸入信號。CLK為計數時鐘,引自波特率時鐘分頻器,EMPTY每來一個高脈沖(喂狗)將內部計數器清零,視為數據正確,ERROR送出低電平,當EMPTY長時間處于低電平,計數器計到2000后將ERROR自成一個高電平,將系統復位,再回到低電平。

3.2.4 數據控制模塊(MCU)

數據控制模塊負責將FIFO中的一幀數據讀出來,然后按照數據格式中規定的數據格式,將數據送入相應的數據總線上。該模塊主要特點:

(1)數據的高速讀取,采用16MHz時鐘控制,不影響通信的速度。(2)數據的鎖存,由內部狀態機產生控制信號,使得接收到的數據穩定的鎖存到數據總線上。(3)差錯控制,配有簡單的差錯控制,當幀數據不同步將總模塊重新復位,不會將錯誤的數據送到總線上。(4)狀態機控制時序清晰,每一部數據的傳輸都有足夠的建立/保持時間。

4 異步通信模塊設計綜述

該異步通信模塊實現了預期的設計功能,數據傳送較為可靠,但由于起初對設計需求分析不夠,系統中很多高級功能未被采用,例如HDLC協議中的插零,CRC校驗位沒有被采用,接收部分也沒有對接收到的CRC校驗位作處理,但是對于短波發射機自動調諧系統來說,由于通信數據量不大該設計已經夠用,該通信模塊已經使用8年,沒有出現任何問題,說明該設計是成功的,確保了我局安全傳輸發射工作。

參考文獻

[1]黃曉兵.TBH522型150KW短波發射機維護手冊[M].中國書籍出版社.

[2]湯永福.TBH522型150KW短波發射機自動調諧控制系統[Z].內部使用.

作者簡介:林大橋(1973-),男,漢族,福建龍巖人,國家新聞出版廣電總局七三一臺,工程碩士,本科,高級工程師。