基于FPGA的工業實時通信模塊分析

黃昊

摘 要:在傳統工業實時通信模塊的設計中,采用的多是PLC編程的方式,以CAN總線作為擴展總線,其通信速率無法滿足工業現場大型應用場合的需求,影響了信息的有效穿在。對于這種情況,本文提出了一種基于FPGA的工業實時以太網通信模塊,立足標準以太網,通過定時器實現PLC主從站之間通信的周期性,可以顯著提升通信速率。

關鍵詞:FPGA;工業實時通信模塊;設計

中圖分類號:TP202 文獻標識碼:A 文章編號:1006-8937(2016)32-0066-02

1 概 述

在當前的技術條件下,PLC內部通信采用的多是分層結構,將通信分為不同插箱之間的通信以及插箱內部各個模塊之間的通信,而傳統PLC采用的是單層通信模式,在不同插箱之間利用CAN總線實現串聯通信,不僅通信距離短,而且通信的速率不高,通常僅能達到500 Kbps,在這種情況下,系統掃描一個模件所需的時間約為1.6 ms,信息傳輸存在著很大的滯后性。如果利用通訊速率100 Mbps的工業實時以太網,在同等條件下,完成所有模件掃描的時間也僅需0.8 ms,通信速率得到了極大的提升。因此,針對當前CAN總線通信效率低下的問題,可以結合FPGA技術,將其升級為工業實時以太網,在提升通信速率的同時,滿足工業現場的各種復雜需求。

2 基于FPGA的工業實時通信模塊設計

FPGA,全稱Field Programmable Gate Array,即現場可編程邏輯門陣列,屬于一種比較特殊的半導體,在其中含有可以根據用戶需求進行編輯的元件,其在程序編輯方面具有設計周期短,便捷方便,修改簡單等特點。在實際應用中,FPGA相比較ASIC(專用集成短路)的響應速度要慢,實現同樣的功能也需要更大的面積,不過其同樣具有非常顯著的優勢,如能夠實現快速成品,成本更加低廉,可以對程序中存在的錯誤進行改正等。考慮到通信接口模塊本身的連接的受控模塊較多,其各自的接口形式和通信協議存在著一定的區別,加上部分數據對于通信延時有著較高的要求,可以采用具備較強靈活性的FPGA技術,進行工業實時以太網通信模塊的設計,需要從硬件和軟件兩個方面進行考慮[1]。

2.1 硬件結構

主控芯片選擇Xilinx公司的Spartan-6XC6SLX45 FPGA,外部存儲器選擇DDR3 SRAM芯片MT41J64M16LA-187EIT以及Flash芯片25P64V6P。在網路芯片的選擇種,采用了100M單物理層芯片的方案,選擇PHY芯片DP8363SQ,以IP core在FPGA內部實現Ethernet MAC,與PHY芯片通過RMII接口連接在一起。

這里的Microblaze是基于Xilinx公司FPGA的微處理器IP核,采用RISC架構以及哈佛結構的32位指令及數據總線,能夠對存儲在片上存儲器和外部存儲器中的程序進行全速執行,同時對其中的數據進行訪問。系統CPU設置有大量的外部設備,如SRAM、Flash、MAC等,系統為每一個設備分配了獨有的地質,CPU對于各個設備的訪問可以看做是相應地址的操作過程。

以太網IP core AXI Ethernet Lite MAC支持IEEE802.3標準,可以結合簡化媒體獨立結構,與工業標準PHY芯片連接,通過AXI4-Lite以及Microblaze實現相互之間的信息傳遞,支持10M乃至100 M的以太網通訊速率。IP核采用同步設計,為了確保以太網的通信速率能夠達到最大的100 Mbps,系統時鐘頻率設置為50 Mbps。本系統硬件平臺的搭設以及軟件應用程序的開發都是在嵌入式軟件開發工具EDK中實現的,硬件平臺的搭設環境為XPS,軟件程度的開發環境為SDK。

2.2 軟件設計

2.2.1 數據接收與發送

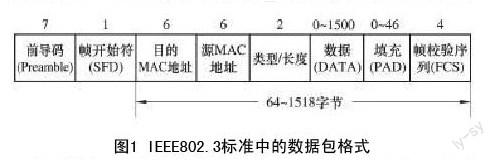

在通信模塊中,軟件設計主要是實現PHY芯片的初始化,確保其能夠對以太網接收中斷處理函數進行定義,同時以實現以太網接收中斷的初始化。初始化主要是針對以太網MAC數據幀而言,在IEEE802.3標準中,數據包的格式類型,如圖1所示。

在系統中,以太網接收數據端為PHY_dv,在程序運行時,會首先判斷PHY_dv是否置1,如果置1則可以進行數據幀的接收,接收完成后,MAC會自動進行自身目的地地址與數據幀目的地地址的對比,如果無法匹配,則地址無效,會將接收到的數據全部丟失,重新接收;如果匹配,MAC會針對數據幀進行CRC計算,并且繼續與接收到的數據幀的幀校驗序列FCS中的CRC進行比對,若匹配,完成數據接收,若不匹配,表明FCS錯誤,重新接收數據[2]。

MAC對于數據幀的發送主要是依照以太網CSMA/CD技術。

2.2.2 周期同步處理

在標準以太網中,數據發送采用的是CSMA/CD技術,當網絡負荷不高時,很少發生沖突,基本上能夠滿足對于通信實時性的要求。但是,在工業現場,具有容量巨大、傳輸速率快、IO點眾多的特點,網絡的負荷通常都比較重,容易發生沖突問題,從而造成網絡性能的下降。考慮到沖突和處理的隨機性以及網絡通信延時的不確定性,想要保證通信的實時性非常困難。

因此,在通信模塊的設計中,將定時器定義在頂層應用程序,從主站定期向從站發送數據,從站在接收到數據后,立即向主站回發數據。如果主站在向從站發送數據局后,在設定好的時間內沒有接收到從站回發的數據,則此次數據發送失敗,產生錯誤,主站會在將錯誤的計數器加8后,繼續進行下一個節點的數據傳輸、如果其中一個從站出現連續數據發送錯誤,在不斷的累計錯誤會移出,主站就可以判定從站斷線,發送相應的警報信息,通知工作人員進行處理。

2.2.3 以太網收發測試

以太網數據幀是以一種字節增序的方式存儲在TX buffer中,AXI Ethernet Lite MAC接受到的以太網數據幀同樣會以增序的方式存儲其中。數據發送的主要程序如下:

int main()

{

Initialize();

u32 i;

while(1)

{

for(i=0;i<1000;i++)

{

EmacRegisterWrite(0x07fc,0x01);

while(EmacRegisterRead(0x07fc)﹠(0x01)){}

}

}

return 0;

}

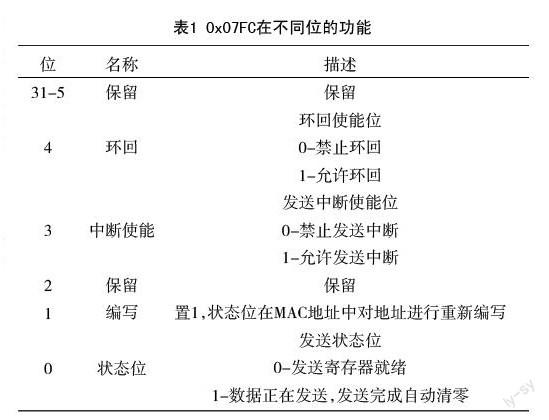

寄存器0x07FC是發送控制寄存器,上述程序中的EmacRegisterWrite(0x07fc,0x01)所表述的韓式是對0x07FC的第0位置1進行數據的發送,數據幀發送完成后,該位會自動置1。0x07FC在不同位的功能,見表1。

在程序中,對于MAC寄存器寫入數據0a0a0a……即需要通過以太網發送的數據,可以對其進行任意賦值。這里將其賦值為1 038,包含了數據幀的頭尾,實際數據長度為1 024.在程序中,對于目標地址的賦值為ff-ff-ff-ff-ff-ff-ff,源地址賦值00-00-5E-00-00-00。在FPGA中下載程序,結合wireshark抓包工具,就可以對發出的數據幀進行查看。

當PHY接收到一個數據幀后,會立即回發五幀數據,這里的寄存器0x17FC即為接收控制寄存器,其在不同位的功能如下:

0位即狀態位,0-接收寄存器就緒,1-數據正在接收,接收完成自動清零;1-2位屬于保留位,對接收的信息進行保留;3位為中斷使能,0-禁止接收中斷,1-允許接收中斷;4-31位同樣為保留位。

對程序進行編輯制定,同樣結合wireshark抓包工具,可以看到接收一幀數據同時回發五幀數據的過程[3]。

3 結 語

綜上所述,本文基于FPGA,針對工業實時以太網通信模塊進行了設計和開發,利用以太網通信來取代傳統PLC中的擴展總線CAN網,能夠極大的提升PLC的通信速率,滿足工業現場對于通信實時性的需求。經過測試,本文提出的方案具有良好的實踐效果。

參考文獻:

[1] 張偉.基于FPGA的通信接口模塊設計與實現[J].電子科技,2012,25(7):

95-98.

[2] 王琦,徐潔,彭文才,等.基于FPGA的工業實時以太網通信模塊設計[J].

水電自動化與大壩監測,2014,38(5):62-66.

[3] 賀永鵬,張向前,張凱,等.一種基于FPGA的嵌入式實時以太網[J].電氣 傳動,2015,45(7):70-73.