FPGA的驗證平臺及有效的SoC驗證方法

張躍玲,張磊,汪健,王鎮

(1.北方通用電子集團有限公司 微電子部,蘇州 215163;2.63963部隊)

?

張躍玲1,張磊2,汪健1,王鎮1

(1.北方通用電子集團有限公司 微電子部,蘇州 215163;2.63963部隊)

摘要:設計了一種基于FPGA的驗證平臺及有效的SoC驗證方法,介紹了此FPGA驗證軟硬件平臺及軟硬件協同驗證架構,討論和分析了利用FPGA軟硬件協同系統驗證SoC系統的過程和方法。利用此軟硬件協同驗證技術方法,驗證了SoC系統、DSP指令、硬件IP等。實驗證明,此FPGA驗證平臺能夠驗證SoC設計,提高了設計效率。

關鍵詞:DSP;SoC系統;FPGA平臺;驗證技術

引言

隨著集成電路技術的發展以及EDA 設計水平的迅速提高, 基于IP(Intellectual Property) 進行SoC(System on Chip)芯片設計的能力和技術得到了大大的提高。在一些應用中,需要處理的數據量不斷增大,并且處理時間也要縮短,數據運算更加復雜,內嵌DSP核處理器的SoC技術能夠縮短處理時間并能進行大數據量的處理,提高可靠性,縮小體積,降低功耗。因此本文研究一種基于DSP的SoC芯片的FPGA驗證方法,并將整個系統包括DSP處理器、片上總線、ASIC、內存模塊、I/O 外圍設備及其他IP模塊集成到一個芯片中。而在復雜的內嵌DSP核的SoC 芯片的系統設計中, 為了保證SoC芯片設計的正確性, 驗證工作變得越來越重要, 也更加復雜。FPGA驗證是復雜芯片和SoC芯片設計驗證的一種有效手段,可以彌補軟件模擬仿真的不足,減少驗證時間,檢驗SoC的設計是否實現了設計規范確定的功能,從而提高SoC芯片流片成功率。

1基于DSP核控制的SoC系統

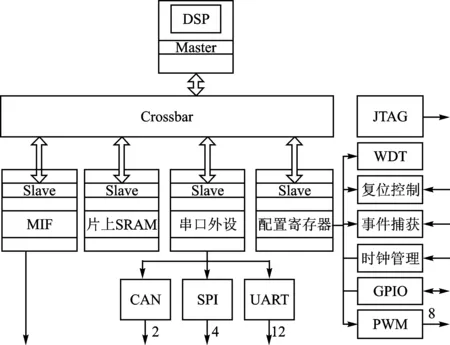

本文設計的SoC系統采用國內自主研發DSP核,主要包括: DSP處理器核、片上AXI總線、PWM、事件捕獲器、看門狗控制、中斷控制器、復位管理、存儲模塊、I/O以及其他外設(UART、CAN、SPI等)模塊。這些模塊與DSP核之間通過AXI總線連接,進行數據通信。AMBA AXI的總線協議具有高性能、支持高頻傳輸、高速亞微型系統互連的特征,為主從結構,一切觸發都由主設備發起。核間通信總線采用SoC系統中應用最多的AXI總線結構,比較靈活,可滿足對帶寬需求不同的各種IP。

基于DSP的SoC系統結構框圖如圖1所示。

圖1 基于DSP的SoC系統結構框圖

2SoC系統的FPGA驗證平臺

FPGA驗證平臺用于SoC芯片驗證,可以對大規模SoC系統的設計進行快速準確的實時驗證,根據不同SoC規模容量,采用不同的FPGA硬件資源,硬件平臺建設也有所不同。由于FPGA具有靜態可編程和在線動態重構特性,能夠使硬件功能電路同軟件程序一樣方便修改,使得FPGA驗證修改十分方便、實時性好,還可以縮短開發周期、降低開發成本。FPGA具有的這些特點使其成為通用的SoC功能驗證的器件,為SoC的系統原型驗證提供了一個非常合適的平臺。目前FPGA已經從系統集成、系統存儲、系統時鐘和系統接口4個方面滿足了SoC芯片驗證的要求,為快速系統原型驗證提供了一個非常合適的平臺。本文的FPGA驗證平臺采用Xilinx Virtex-6 LX760器件,是建立在Xilinx Virtex6 FPGA板上的軟硬件聯合驗證系統,并用ISE13.3進行綜合和布局布線。另外,此FPGA硬件驗證平臺包括支持DSP程序下載的JTAG接口。

2.1FPGA硬件平臺搭建

硬件平臺搭建主要使用了兩個Xilinx Virtex-6 LX760 FPGA器件,具有15.2M個邏輯門。Virtex-6 LX760面向高端應用,具有更多的時鐘和存儲資源,而且能夠支持更快的速度。通過分析,所選擇FPAG能夠滿足此SoC驗證使用,為了實現通用性,該FPGA硬件驗證平臺采用了子板和母板相結合的方式。在母板上設置有通用的FPGA芯片、相應的PROM、系統全局時鐘的選擇和配置模塊、系統復位邏輯、FPGA芯片下載接口、與子板連接的connector接口等模塊。子板根據驗證需求,配置了JTAG調試子板,以提供DSP仿真器連接的調試接口。另外還設計配置了驗證EMIF訪問外部存儲設備通路的SRAM存儲器子板。為了方便測試和驗證EMIF接口功能,在這兩類測試子板上,都設有關鍵信號的測試探測點,以方便測試一些基礎的時鐘、復位信號以及其他探測信號。

2.2FPGA軟件環境搭建

在SoC 設計中,經常會使用一些硬IP 核(如PLL、SRAM、ADC、USB transceiver 等),而在采用FPGA驗證技術驗證ASIC及SoC設計的過程中,需要做ASIC設計原碼的轉換,所以首先需要對SoC進行修改,以適合FPGA的開發環境。如門控的處理,添加PLL對所需要的時鐘進行適當的分/倍頻,存儲單元RAM、FIFO的替換,修改子模塊配置,特殊單元的處理等。還要根據特定的硬件平臺增加FPGA 相關時序Timing的約束和I/O引腳的指定約束,并搭建一個能夠自動仿真和驗證的環境。在FPGA驗證過程中主要使用ISE13.3內置綜合工具或專用綜合工具對RTL進行編譯、綜合,生成網表。生成的網表可以生成bit文件,包括優化、適配、bit文件生成等。進行靜態時序分析,檢查是否滿足預定的時鐘頻率要求,若不能滿足,則重新進行綜合編譯優化。如果多次進行優化仍不能滿足時序要求,則根據違反時序信息查找關鍵路徑,對RTL設計代碼進行修改優化。

FPGA驗證軟件除了需要上述提到的綜合布局布線的軟件環境ISE13.3外,還需要FPGA內部信號在線調試工具Chipscope,即時抓取一些內部邏輯信號,分析內部邏輯正確與否。在驗證調試階段,還需要DSP核下載調試軟件CCS3.3,以編寫控制處理器核DSP運行軟件的測試程序。

2.3軟硬件協同驗證系統

FPGA驗證SoC系統方法是軟硬件協同仿真和驗證,并搭建軟硬件協同驗證平臺系統。實現的基礎條件是能夠滿足工作要求的FPGA硬件平臺,以及有力的設計描述及編譯工具等軟件環境。而基于DSP控制的SoC驗證系統還需要DSP軟件程序開發環境及下載通路等。

2.3.1FPGA軟硬件協同驗證架構

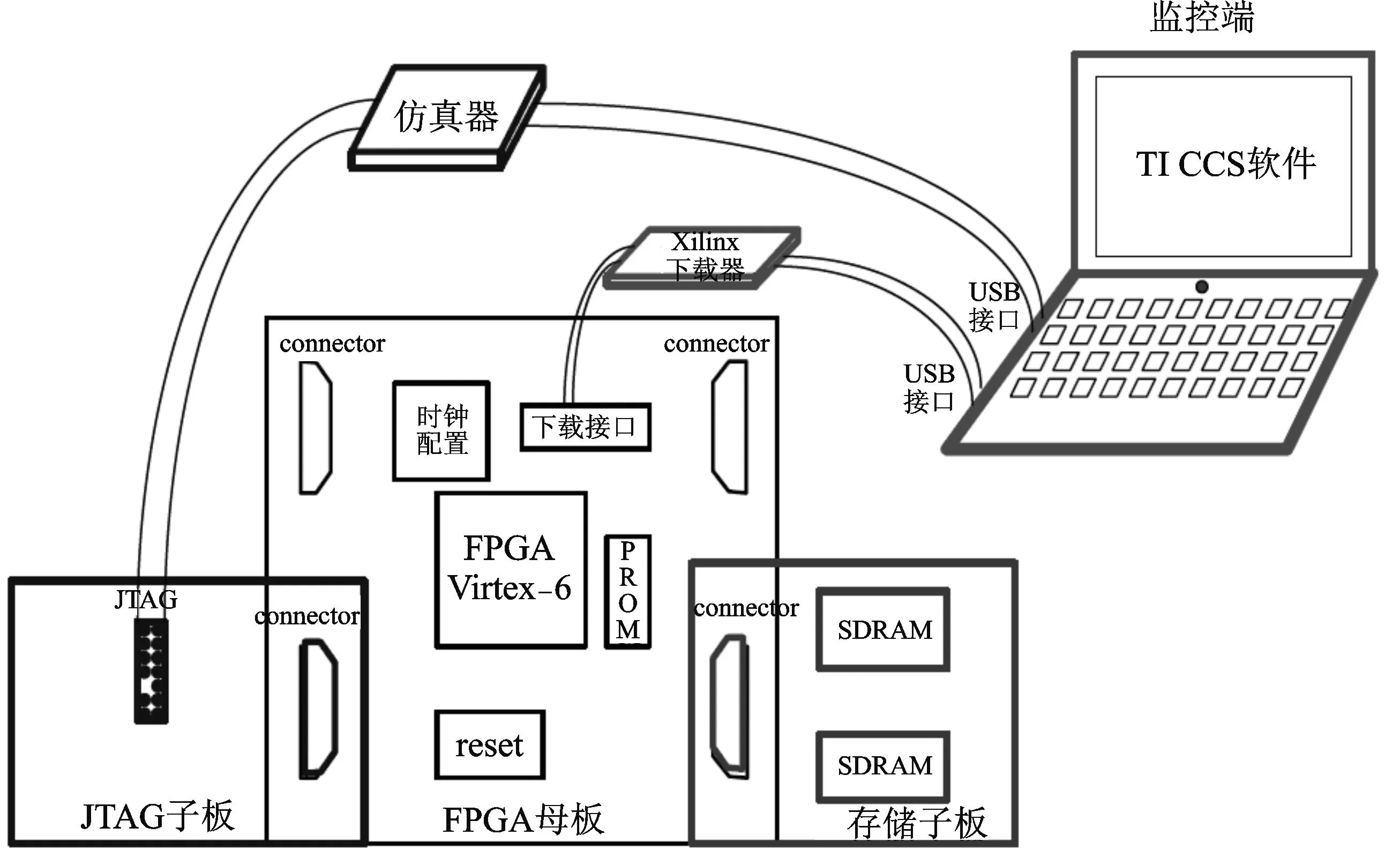

FPGA驗證是為了實現和驗證SoC芯片在實際硬件環境下的功能和運行工作情況。針對本文提出的基于DSP的SoC系統,搭建能夠實現和驗證其DSP程序指令及內部電路工作的軟硬件協同驗證系統平臺。建立的FPGA軟硬件協同驗證系統的基本架構如圖2所示。

其中包括FPGA原型驗證需要的Xilinx Virtex-6芯片的FPGA驗證母板、支持下載bit文件及驗證調試過程中需要的Xilinx FPGA編程器及下載線、能夠支持正確下載DSP激勵測試程序的DSP-JTAG調試子板、支持DSP芯片的仿真器、安裝有TI CCS軟件和 ISE13.3,以軟件及支持DSP芯片驅動的計算機。

圖2 FPGA軟硬件協同驗證系統的基本架構

2.3.2驗證過程

軟硬件協同驗證過程分以下幾個步驟:

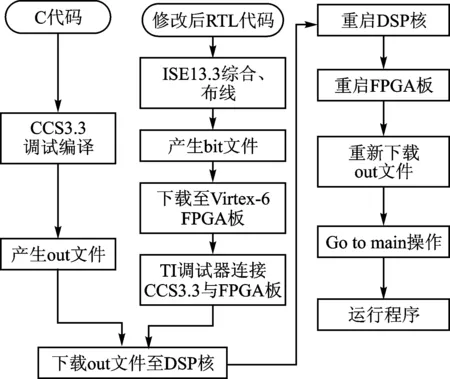

① 首先把要驗證的SoC系統由ISE13.3自動綜合及布局布線實現后生成相應的FPGA位流文件,經JTAG下載至構建的FPGA驗證系統中的FPGA芯片或對應的PROM中。

② 通過微機CCS開發界面編寫控制內部DSP核運行的程序,完成程序啟動初始化、測試激勵程序編譯、開發驗證IP及系統需要的程序。

③ 通過DSP仿真器以實時的方式進行軟硬件協同驗證過程中的管理控制,通過編寫及測試程序的加載、運行、調試,實現對DSP核單步操作、連續運行等;通過設置正確中斷服務程序、設置斷點、觀測DSP核內部寄存器及SoC配置寄存器值等分析DSP核運行及操作IP情況。

④ 通過不同的控制程序驅動運行相應功能IP模塊及整個系統工作運行,驗證IP功能及不同IP之間的交互和總線競爭。

在驗證過程中可以根據IP功能及SoC系統特性使用示波器觀測引腳信號,利用Chipscope軟件抓取內部信號來判斷邏輯關系及系統運行的準確性,驗證DSP核、SoC系統及相應IP功能;驗證系統各模塊間的相互操作、片上系統內的數據相互流通功能;驗證所有IP集合協同運行情況;驗證整個系統的正確性。具體驗證流程圖可參見圖3。

3SoC系統及IP模塊功能驗證

對SoC系統及內部IP功能模塊進行驗證,需要首先驗證FPGA軟件平臺及硬件平臺的正確性,才能在CCS環境下編寫控制DSP的程序以驗證SoC系統設計及各個功能模塊的正確性。CCS編程器與FPGA硬件平臺連接正確后,可通過下載編寫控制DSP內核的程序,驗證DSP運行正確性,并通過編寫控制其他IP邏輯模塊驗證SoC系統內部交互及IP邏輯設計。其中主要進行了下面幾種功能模塊劃分及其驗證,通過驗證功能模塊也進一步驗證了SoC系統及片上總線等設計的正確性。

3.1DSP核的驗證

通過CCS開發界面對DSP內部寄存器進行讀寫操作并觀測DSP內部寄存器的變化以實現驗證DSP的功能,分別對DSP內部的Timer、GPIO、中斷寄存器等進行讀寫及功能驗證,并通過DSP控制其他各類寄存器以驗證DSP核的正確性。

3.2EMIF及片上儲存設備的驗證

利用DSP能夠正確讀寫片上存儲器設備及支持各類讀寫操作,對片上存儲設備進行驗證。為了驗證EMIF接口,在FPGA工程里對EMIF I/O口進行綁定約束使其與SRAM存儲器子板進行正確的連接,通過DSP對EMIF空間寄存器的控制,使DSP能夠正確地對連接在EMIF外的SRAM進行各類型的讀寫操作,可驗證EMIF接口設計。

圖3 基于DSP的SoC系統的FPGA驗證流程圖

本SoC系統中設計的EMFI接口模塊可以連接4個外部存儲空間CE0~CE3。通過ISE工具使用Xilinx Virtex-6芯片的FPGA IP core例化4個寬度為32位、深度為64位的SRAM,并且將它們連接到CE0~CE3空間接口上。在CCS中,初始化CE0~CE3空間接口,對各空間前16個地址寫數據,之后對這些地址進行讀操作。執行單步調試命令,可以成功讀取CE0~CE3空間地址里面寫入的數據。DSP核指令代碼,首先配置全局控制寄存器,選擇DSP提供的系統時鐘,指令代碼寫全局控制寄存器:

*(int*)0x4000a000 = 0x00000000

配置CE0~CE3時鐘寄存器和空間寄存器:

*(int*)0x4000a004=0x00000004;*(int*)0x4000a008=0x00000006;

*(int*)0x4000a00C=0x00000008;*(int*)0x4000a010=0x0000000a;

*(int*)0x4000a014=0xffffffe6;*(int*)0x4000a018=0x1091c226;

*(int*)0x4000a01c=0x30d5c846;*(int*)0x4000a020=0x2251c736;

對各空間前16個地址寫數據,之后對這些地址進行讀操作的DSP核指令代碼:

for(i=0;i<16;i++){

*(int*)(0xC0060000+4*i) = (0x00000600+i);

*(int*)(0xD0060000+4*i) = (0x00000700+i);

*(int*)(0xE0060000+4*i) = (0x00000800+i);

*(int*)(0xF0060000+4*i) = (0x00000900+i);

}

for(i=0;i<16;i++)

{

temp_data = *(int*)(0xC0060000+4*i);

temp_data = *(int*)(0xD0060000+4*i);

temp_data = *(int*)(0xE0060000+4*i);

temp_data = *(int*)(0xF0060000+4*i);

}

運行DSP核指令代碼,觀察CE0~CE3寄存器的值,能夠成功進行讀寫,驗證了EMIF的正確性。

3.3事件捕獲、看門狗等功能模塊的驗證

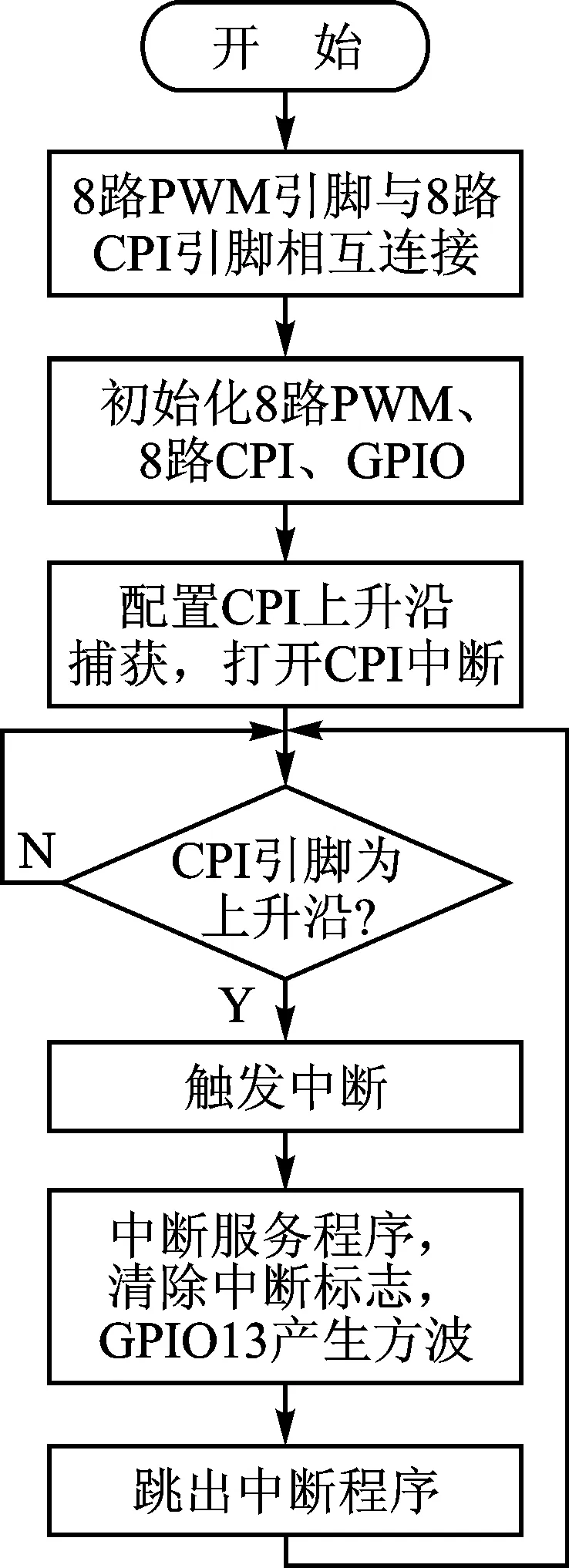

圖4 驗證CPI模塊原理框圖

通過DSP操作控制看門狗邏輯模塊寄存器,看門狗能夠正確運行,并能夠正確影響復位模塊以驗證看門狗IP模塊。通過DSP正確操作CPI等寄存器,使CPI模塊產生中斷并發送至DSP,DSP能夠正確響應中斷信號進行及時處理。為了方便驗證CPI功能,此SoC驗證CPI模塊把PWM產生波輸入到CPI模塊,配置CPI捕獲模式,當CPI模塊輸入有變化時,進行捕獲產生中斷。當發生中斷時,CPI_INT為高電平,當DSP處理后會變為低電平信號。驗證方法原理如圖4所示。

在Chipscope中正確設置觸發條件并通過FPGA編程器及JTAG傳送到PC主機,可觀察其邏輯波形的正確性。CPI中斷事件圖略——編者注,可以看出,CPI_INT6從高電平到低電平的轉換,可說明DSP對CPI中斷事件進行了處理,并正確響應外部中斷。可驗證正確設置CCS配置IP模塊寄存器后,IP硬件模塊能夠正常運行。

3.4PWM、SPI、CAN、UART等外設模塊

通過控制內部寄存器,能夠產生正確的PWM波,分別在示波器及Chipscope上對一些信號進行采集及觀測分析,驗證其正確性,驗證方法和驗證CPI、EMIF相同。測試驗證結果表明其功能正確。其中結合示波器測試PWM波,驗證PWM設計的正確性,另外還使用相同方法驗證SPI、CAN、UART等各IP功能的正確性。

結語

本文以一個DSP處理器控制的SoC芯片的開發與驗證項目為例,介紹了關于FPGA的軟硬件協同驗證方法及過程,搭建FPGA驗證硬件平臺及軟件平臺環境, 并通過軟硬件協同驗證, 在線驗證調試SoC系統中邏輯及功能設計, 并對每個功能模塊進行了驗證分析。通過CCS輸入控制DSP程序進而控制SoC系統及內部IP模塊,具有可觀測性及實時性,實驗結果表明,通過FPGA軟硬件協同驗證系統可以對目標SoC芯片進行功能驗證及性能評估,縮短了基于SoC芯片的應用系統的開發時間,提高了流片成功率,整個驗證平臺及方法具有較高的可靠性。

編者注:本文為期刊縮略版,全文見本刊網站www.mesnet.com.cn。

參考文獻

[1] 李輝,李平.一種嵌入式DSP 核的設計及FPGA驗證[J].微電子學,2008,38(2):302-305.

[2] 王國章,須自明,劉戰,等.SoC芯片驗證技術的研究[J].微計算機信息,2007,23(23):132-133.

[3] 豐玉田,付宇卓,趙峰.大規模SoC 設計中的高效FPGA驗證技術的研究與實現[J].電子技術應用,2006,32(2):110-113.

[4] 李建昌,趙博生,鮑勝榮.基于ARM7TDMI 的SoC 芯片的FPGA 驗證平臺設計[J].電子工程師,2004,30(9):6-9.

[5] 虞致國,魏敬和.基于FPGA的ARM SoC原型驗證平臺設計[J].電子與封裝,2007,7(5):25-28.

[6] 劉朝,萬培元,于忠臣.基于ARM7TDMI的SoC芯片的原型驗證[J].數字技術與應用,2013(12):73-75.

張躍玲(設計師),主要從事數字集成電路設計。

(責任編輯:薛士然收修改稿日期:2015-10-09)

Zhang Yueling1,Zhang Lei2,Wang Jian1,Wang Zhen1

(1.R&D Center in Suzhou,Northern General Electronics Group Co., Ltd.,Suzhou 215163,China;2.63963 Troops)

Abstract:A FPGA verification platform is designed and an effective verification way of SoC is introduced.The basic scheme of the FPGA verification system is shown,and the software and hardware verification platform is introduced.The verification process and method are discussed.Due to the software and hardware co-verification technique,it can verify the SoC system design,the DSP statement,the hardware IP and etc.The experiment results show that the verification platform can verify the SoC design and improve the design efficiency.

Key words:DSP;SoC system;FPGA platform;verification technique

中圖分類號:TN492

文獻標識碼:A