高速模數/數模轉換電路的研究與實現

童旭升

(中國電子科技集團公司第20研究所,西安 710068)

?

高速模數/數模轉換電路的研究與實現

童旭升

(中國電子科技集團公司第20研究所,西安 710068)

摘要:收發信道一直以來都是通信系統的一個重要組成部分。隨著數字化集成電路的發展,高速數字電路逐步代替大部分模擬電路,而收發信道后高速的數模/模數轉換電路顯得尤為重要。詳細介紹了一種通用的高速模數/數模轉換電路的實現方法,并且已經在L波段某型通信系統中應用。

關鍵詞:模數/數模轉換;數字電路;現場可編程門陣列;數字信號處理器

0引言

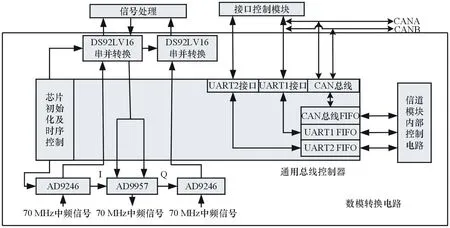

設計一種2路模數轉換和1路正交上變頻數模轉換電路,將射頻部分下變頻得到的70 MHz中頻信號經過AD9246采樣后通過DS92LV16串并轉換為低壓差分信號(LVDS),送往信號處理芯片,將DS92LV16芯片轉換得到的信號送往AD9957,經上變頻和濾波得到70 MHz模擬中頻信號。同時數字信號處理器(DSP)可通過串口和控制器局域網(CAN)總線完成參數控制以及狀態查詢等功能。

1理論基礎

在一般通信系統中,信號的頻率在某一有限的頻帶(fL,fH)上,而且信號的帶寬與信號的最高頻率fH相比要小很多,因此使用奈奎斯特第一采樣定理不再合適,這種情況下采用帶通采樣定理。

帶通采樣定理表述為:設有一個頻率帶限信號x(t),其頻率范圍限制在(fL,fH)范圍內,如果其采樣頻率滿足[1]:

(1)

式中:n能取滿足fs≥2(fH-fL)的最大正整數(0,1,2,…),則用fs進行等間隔采樣所得到的信號采樣值x(nTs)能準確恢復出原始信號x(t)。

對于本系統來說,中頻信號為70 MHz,選擇采樣頻率fs=40 MHz。

2設計實現與驗證

2.1芯片選型

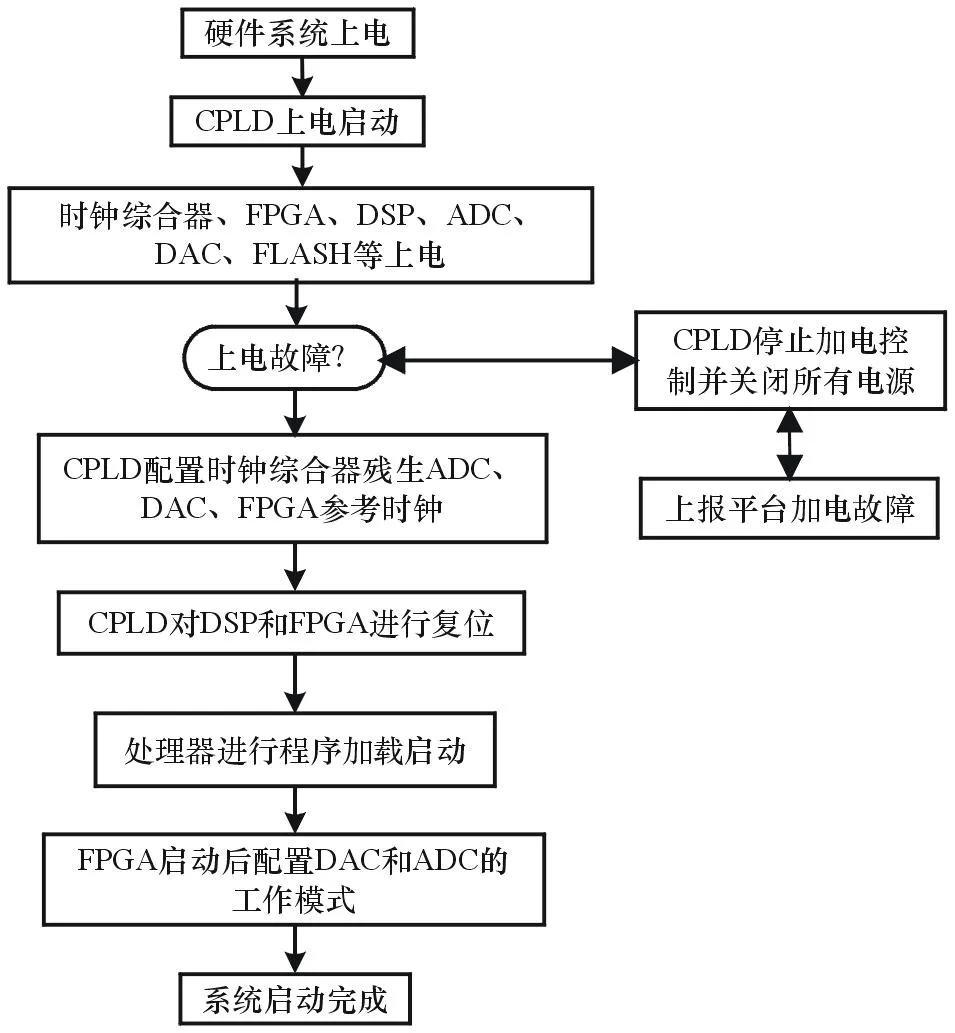

現場可編程門陣列(FPGA)作為核心處理器完成的任務為:數組從AD9246輸出,根絕芯片參考時鐘將數據緩存至雙口隨機存儲器(RAM),并通知DSP收數,將DS92LV16經過串并變換輸出的數據存入雙口RAM,并通知AD9957取數,配置AD9957為正交上變頻模式,根據芯片的參考時鐘將數據輸出給AD9957進行正交上變頻至70 MHz。

圖1 硬件系統啟動流程

模/數轉換器選擇ADI公司的AD9246,該芯片可以在70 MHz中頻時達到71.7 dBc的信噪比(SNR)(72.7 dBFS)以及85 dBc的無雜散動態范圍(SFDR),而功耗在125 MSPS時只有395 mW,帶寬范圍可以達到650 MHz[2]。

數模轉換器采用AD9957,該芯片可以1 GSPS內部系統時鐘(高達400 MHz模擬輸出),數據吞吐速率達到250 MHz I/Q,相位噪聲小于125 dBc/Hz(1 kHz偏移,400 MHz載波),大于80 dB的窄帶SFDR,以及反正弦濾波器和4~252倍的差值范圍。AD9957可以工作在正交調制模式(QDUC)、數/模轉換器(DAC)差值模式以及單頻調制模式。本文將使用的是QDUC正交調制模式,此模式使用直接數字合成器(DDS)和內置的速率差值濾波器。在這種情況下,2個并行速率差值濾波器組支持同向和正交(I/Q)信號的基帶處理,DDS可以提供要由基帶信號進行調制的載波信號。在QDUC模式下,AD9957的數據接口并行地輸入時序交錯式18位I和Q字。一個18位的I字之后是一個18位的Q字[3],以此類推。這樣一個18位的I字和一個18位的Q字共同構成一個內部樣本。數據分配器和格式器對I和Q字進行解交錯處理,以便每個樣本沿著內部數據通路以并行的方式進行傳播。I和Q數據路徑均處于活動狀態;并行時鐘可將I/Q數據輸入同步至AD9957。DDS內核將正交(正弦和余弦)本振信號提供給正交調制器,在這里差值I和Q樣本乘以相應的載波相位并相加,從而產生正交調制的數據流。此數據流通過反sinc濾波器[4]和輸出幅度乘法器,然后施加于14位DAC,從而產生正交調制模擬輸出信號。

DSP通過同步串行總線接收并處理來自其他模塊的系統控制接口控制文件(ICD),并通過FPGA轉換實現對接收和激勵通道的控制指令;通過CAN總線[5]完成模塊狀態回傳、機內自檢(BIT)、程序在線燒寫等功能。

隨著數字信號處理算法的高速發展,其在通信系統尤其雷達、無線電和電子戰領域的應用普遍,現在高速數模/模數轉換已經逐步向射頻端靠近,這就對數模和模數轉換提出更高要求,尤其在更高的采樣速率、位寬和更高的動態范圍[6]。

數模轉換電路原理框圖見圖2。

數模轉換電路實現對射頻電路輸出的70 MHz中頻信號采集、轉發,同時實現對來自信號處理器的基帶波形調制并DA轉換以及和其它模塊的通信(CAN總線與串口通信)。

2.2模數轉換驗證

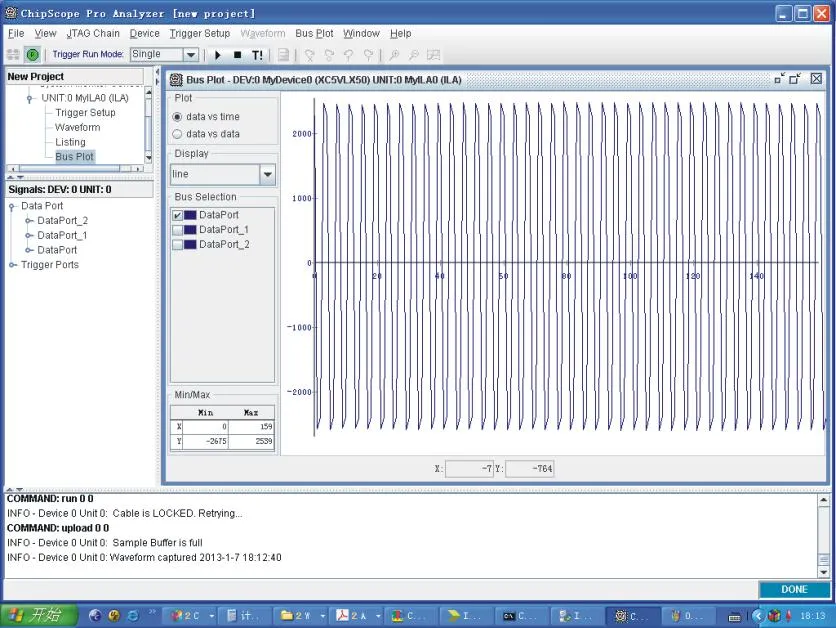

將0 dB的70 MHz模擬中頻輸入到AD9246,FPGA在對AD9246進行配置后可以使用chipscope得到FPGA收到的AD9246經過模數轉換所得數字信號波形,如圖3所示。

將FPGA得到的70 MHz數字信號送給DSP,使用快速傅里葉變換(FFT)后的波形如圖4所示。

2.3模數轉換的驗證

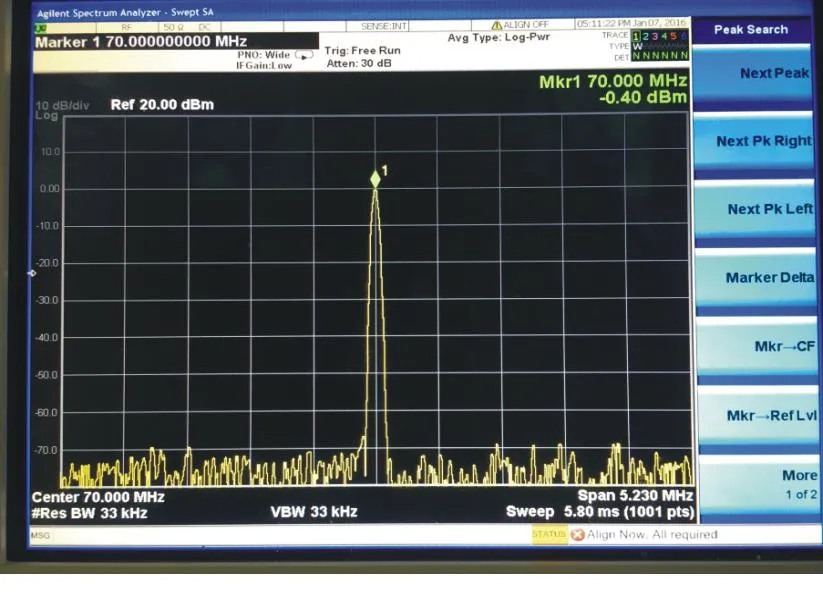

把基帶信號波形通過DSP寫入靜態隨機存儲器SRAM中,FPGA從SRAM中讀出數據并配置AD9957為正交上變頻模式工作在70 MHz,然后從頻譜儀上讀出的波形如圖5所示。

圖2 數模轉換電路原理框圖

圖3 FPGA采樣得到的70 MHz數字信號

圖4 經過FFT變換后的數字信號波形

圖5 AD9957輸出的70 MHz模擬中頻信號

3結束語

本系統實現了對模擬中頻70 MHz信號的數模變換。由FPGA、DSP架構的核心處理器完成AD9957的數模變換、AD9246的模數變換,并通過FFT變換和chipcope采樣對信號進行驗證,目前該系統已經成功地在L波段某型通信系統使用,大大提高了系統的整體性能。

參考文獻

[1]陶玉柱,胡建旺,崔佩璋.軟件無線電技術綜述[J].通信技術,2011,44(1):37-39.

[2]李坤賀,岳曾敬.基于查找表和CORDIC 算法的混合型 NCO 設計[J].兵工自動化,2014,33(3):43-46.

[3]Analog Devices,Inc.AD9957 data sheet[M].Norwood,MA02062 USA:Analog Devices,Inc,2006.

[4]Analog Devices,Inc.AD9246 data sheet[M].Norwood,MA02062 USA:Analog Devices,Inc.2006.

[5]KROUPA V F.Direct digital frequency synthesizers [M].Hoboken NJ:Wiley-IEEE Press,1999.

[6]Andraka R.A survey of CORDIC algorithms for FPGA based computers[C]//Andraka,ray:Proceedings of The 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays.ACM,Monterey,California,USA,1998:191-200.

Study and Realization of High-speed AD/DA Conversion Circuit

TONG Xu-sheng

(The 20th Research Institute of CETC,Xi'an 710068,China)

Abstract:The transmit/receive channel is an important part of communication system all along.Especially with the development of digital integrated circuit (IC),the analog circuit is replaced by high speed digital circuit step by step,so the high speed analog to digital/digital to analog (AD/DA) conversion circuit after transmit/receive channel becomes more important.This paper introduces a general realization method of high speed AD/DA conversion circuit,and the system has been already applied to a L-band communication system.

Key words:analog to digital/digital to analog conversion;digital circuit;field programmable gate array;digital signal processor

收稿日期:2016-02-29

中圖分類號:TN792

文獻標識碼:A

文章編號:CN32-1413(2016)02-0091-03

DOI:10.16426/j.cnki.jcdzdk.2016.02.023