基于FPGA的高速AD7903驅動設計與實現

蘇 銳 合肥工業大學 儀器科學與光電工程學院 安徽合肥 230009

?

基于FPGA的高速AD7903驅動設計與實現

蘇 銳 合肥工業大學 儀器科學與光電工程學院 安徽合肥 230009

【文章摘要】

高速AD采集目前在激光干涉位移測量中起到重要作用,AD采集的速度以及分辨率直接決定了干涉測量的分辨率。本文設計了一種基于FPGA驅動的高速AD7903采集系統,包括硬件以及軟件設計,并最終對采樣數據進行比較,通用性較強。

【關鍵詞】

AD7903;高速采集;FP

引言

隨著電子技術發展,高速數據采集系統對科學研究以及工業生產有著重要的作用,其中高速AD就是實現數據采集的主要方式之一。本文使用全差分雙通道AD7903實現數模轉換,該芯片最高采樣率1Msp,采用串行數據接口,FPGA提供采樣時序控制。在設計過程中,首先使用Modelsim仿真,之后在硬件平臺實測,使用singal tap觀測采集的數據。

1 系統硬件設計

AD7903是一款全差分雙通道的高速AD,內部2個ADC采用單電源(VDDX)供電。整個AD外圍電路包括前端運放驅動,參考電壓輸入,電源模塊以及AD7903。其中前端運放選用的是ADA4941,參考電壓選用的是ADR435,圖1是設計的電路前置運放部分的原理圖,主要是為了將單端信號輸入變成差分信號給后端AD使用,電阻取值可以按照信號輸入范圍來確定,本文中信號Vpp=10V,差分信號范圍是0~5V,具體可參考ADI公司的CN0032電路筆記。

圖1 電路前置運放部分原理圖

圖2 3線無繁忙模式時序

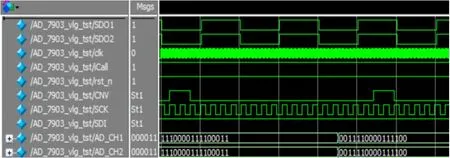

圖3 modelsim仿真時序圖

2 AD7903控制時序設計

AD7903是一款集成多功能串行端口接口(SPI)的器件,并且在使用獨立電源VIOx時,與1.8V、2.5V、3.3V以及5V邏輯電平兼容,本設計采用的是3.3V邏輯電平,VIOx接入的是3.3V。工作模式有CS以及鏈模式2種,本文程序控制使用的是3線無繁忙指示CS模式,使用的是Verilog硬件語言。圖2是3線無繁忙接口時序。

以下是產生CNV,SCK時序部分的Verilog Code

此種模式下,SDI=1,主要控制CNV以及SCK,SCK下降沿依次從SDO讀取數據。圖3是modelsim仿真時序圖。

3 AD7903采集測試結果

將綜合完成的Verilog代碼在JTAG模式下寫入FPGA開發板中,在輸入直流電壓3V時,使用Singal tap查看AD7903的數據采集情況,如圖4所示。

圖4 Singal tap 數據采集

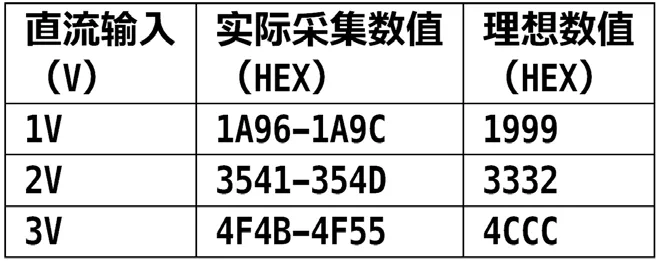

表1是Vref=5V情況下不同直流輸入采集的數據。

表1 AD7903直流電平采集數據結果

4 結論

本文基于FPGA設計了AD7903高速AD的采集系統,涵蓋硬件電路以及軟件編寫,并最終給出了modelsim下的仿真結果以及實際測試的AD采集數據。同時最終的實驗數據表明,整個設計方案有效,且調試靈活,適用范圍廣。

【參考文獻】

[1]何樂年,王憶.模擬集成電路設計與仿真[M].北京:科學出版社,2010

[2]夏宇聞編著. Verilog數字系統設計教程[M].北京航空航天大學出版社,2003

[3]http://www.analog.com/media/cn/ technical-documentation/data-sheets/ AD7903_cn.