基于Cadence的DDR2串擾研究與仿真

董 輝,馬祖杰

(浙江工業大學 信息工程學院,浙江 杭州 310023)

基于Cadence的DDR2串擾研究與仿真

董輝,馬祖杰

(浙江工業大學 信息工程學院,浙江 杭州 310023)

摘要:隨著系統的工作頻率及信號邊沿轉換速率的不斷提高,串擾對于信號完整性的影響日益突出.通過對傳輸線串擾形成機理的分析,使用Cadence仿真軟件對系統中的DDR2 SDRAM的數據線進行串擾仿真,給出了合理處理串擾問題的解決方案.對于數據線的近端串擾和遠端串擾仿真分析,在理論及仿真結果的基礎上,可以通過減小耦合線長度、增大耦合線間距和減小反射等方法降低串擾對于電路的影響.筆者提出了PCB設計中抑制串擾的一些有效措施,對于DDR2 SDRAM的信號完整性設計有一定的指導意義.

關鍵詞:串擾;近端串擾;遠端串擾;耦合

當今,信號頻率日益提高,電路板的面積越來越小,因此信號完整性問題現象也就越發的凸顯出來[1].而在信號完整性的問題中,串擾則是造成其主要的噪聲之一.隨著數字系統的工作速度的增加,布線密度的增加,串擾對于系統所產生的影響越來越嚴重.過大的串擾會嚴重影響系統的性能,造成不可估量的損失[2].伴隨著電子系統時鐘頻率的提高,存儲器技術特別是DRAM技術也得到了飛速發展.目前,DDR2高速內存在嵌入式系統的應用中擔任著中流砥柱的角色.在DDR2的應用中,信號完整性是必須要重點考慮的問題.由于DDR2傳輸速度快,傳輸線較多,由此引發的串擾問題是信號完整性設計中的重點.通過研究串擾的原理,借助cadence仿真軟件對于DDR2走線所產生的串擾問題進行研究,并根據仿真結果提出了幾種抑制串擾的方法.

1串擾形成的機理

串擾源于不同網絡的傳輸及返回路徑間邊緣電場所引起的互容以及邊緣磁場所引起的互感共同作用引起的噪聲干擾[3].串擾會帶來兩個網絡之間的信號完整性問題,在電路中的所有的網絡之間都存在著串擾問題,通常將攜帶噪聲的網絡稱之為攻擊網絡,而把受其他網絡干擾而被動產生噪聲的網絡稱之為受害網絡[4].

串擾分為容性串擾和感性串擾.通常,容性串擾和感性串擾是同時發生的.容性耦合源于攻擊網絡上的電壓產生改變,變化的電壓在受害網絡上引起感應電流進而導致電磁干擾.感性耦合源于攻擊網絡上的電流產生變化,變化的電流在受害網絡上引起感應電壓進而導致電磁干擾[5].這就是串擾產生的物理根源.在容性耦合和感性耦合的共同作用下,將接近受害網絡近端所產生的串擾稱為近端串擾,記為VNE.接近受害網絡遠端所產生的串擾稱為遠端串擾,記為VFE.通過部分簡化的假設,可以得到串擾在理論上的計算公式[6].

近端串擾總噪聲為

(1)

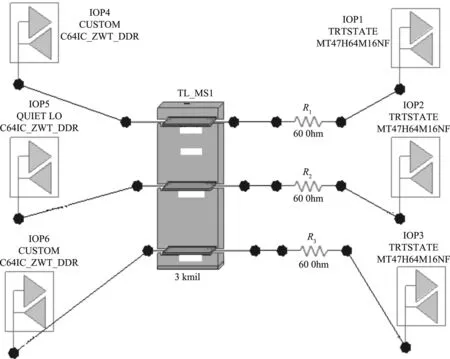

遠端串擾總噪聲為

(2)

其中:CmL為單位長度互容;LmL為單位長度互感;CL為信號路徑上單位長度電容;LL為信號路徑上單位長度電感;v為信號傳輸速度;L為兩條耦合線之間耦合區域的長度;RT為干擾源的上升時間.

互連系統中,所有的主要部件(例如:PCB、封裝、連接器等)都可能產生較大的串擾,從而對系統系能造成損傷[7].由以上分析可知:影響串擾的因素主要包括線間距、耦合長度、干擾源信號頻率、傳輸線阻抗以及反射等,下面將通過仿真對比研究這些因素對于串擾的影響.

2DDR2串擾分析

設計采用兩片型號為MT47H64M16的DDR2 SDRAM,其中每一片的MT47H64M16中包含16 bit數據線,故2片MT47H64M16共有32 bit的數據總線與DSP互連.數據線采用點對點連接的方式,而2片DDR2 SDRAM則共享地址線和控制命令線.

根據DDR2 SDRAM的技術文檔可知:MT47H64M16數據總線的高電平電壓門限值為VREF+0.25,低電平電壓門限值為VREF-0.25,其中VREF為數據線的參考電平(0.9 V).設計要求串擾電壓與噪聲疊加到數據線上以后,不會影響門限電壓對高低電平的判決,由以上計算可得,為不影響對于低電平的判斷,其峰值應小于0.65 V,為不影響對于高電平的判斷,其峰值應大于1.15 V.根據DSP的技術文檔可知,TMS320DM6437與DDR2 SDRAM數據總線所連接的引腳電平類型為SSTL_18,而SSTL_18高電平門限電壓為VREF+0.125,低電平門限為VREF-0.125,其中VREF為參考電平(0.9 V).同樣設計要求串擾電壓與噪聲疊加到數據線上以后,不會影響門限電壓對高低電平的判決,故可知不影響低電平判斷的峰值應小于0.775 V,不影響高電平判斷的峰值應大于1.025 V[8].

3仿真分析串擾

3.1建立串擾仿真模型

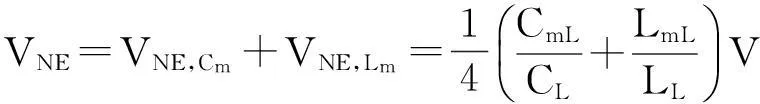

采用Cadence公司的SigXplorer信號完整性仿真軟件對DDR2 SDRAM的數據線的串擾進行仿真.首先獲取器件MT47H64M16和TMS320DM6437的IBIS模型,并利用Cadence公司的Model Integrity將IBIS模型轉換成DML模型.然后提取MT47H64M16的數據線與DSP引腳相連的實際拓撲結構進行仿真.通常相鄰最近的兩條攻擊網絡對于受害網絡產生的噪聲最嚴重,一般只考慮受害網絡與兩條臨近的攻擊網路之間的耦合,就可以包括總噪聲值的95%[9].故給出三平行傳輸線串擾模型如圖1所示.

圖1 三平行傳輸線串擾模型Fig.1 Three parallel transmission line crosstalk model

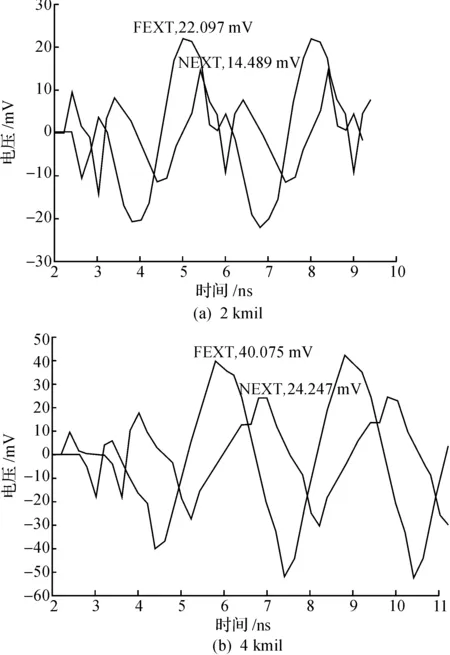

3.2耦合長度對串擾的影響

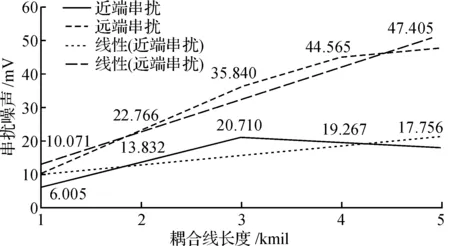

由式(2)可知:信號的耦合長度與傳輸線的遠端串擾成正比關系,即耦合長度越長,傳輸線的遠端串擾越嚴重.圖2為耦合間距為10 mil情況下不同的耦合線長度的仿真結果,圖3為串擾噪聲與耦合線長度的關系曲線.

圖2 耦合長度Fig.2 The coupling length

由圖2可見:當線間距固定以后,串擾噪聲與耦合線的長度為正比例關系.當信號的耦合線長度增加時,信號所受到的遠端串擾總噪聲急劇增加.圖3表明串擾噪聲在耦合線長度小于3 kmil時的值較小,當耦合長度達到3 kmil時,串擾噪聲的值急劇增加.由式(2)可知:耦合線的長度對于遠端串擾的影響較大,所以在滿足設計條件的情況下,要盡量控制平行走線的長度,以此達到減小串擾噪聲的目的.

圖3 串擾噪聲與耦合線長度關系曲線Fig.3 Crosstalk noise and coupling curve

3.3耦合線間距對串擾的影響

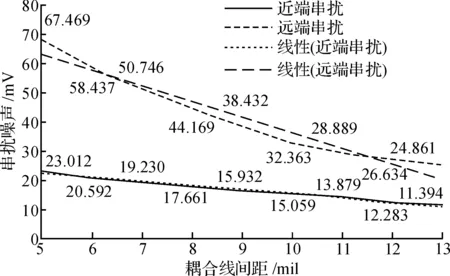

由式(1)可知:串擾噪聲與互感和互容值的大小有關,而互感和互容值隨著耦合線的間距增大而減小,故當其他條件不變時,串擾噪聲與耦合間距有關.圖4耦合線長度為3 000 mil時不同的耦合線間距的仿真結果,圖5為串擾噪聲與耦合線間距的關系曲線.

圖4 耦合線間距Fig.4 The coupling line spacing

由圖4可得:串擾噪聲隨著耦合線間距增大而減小,尤其對于遠端串擾的影響是巨大的.在其他因素不變的條件下,耦合間距增大一倍,串擾幅值約減小一倍.減小串擾噪聲的有效方法包含適當增大導線之間的間距,當導線之間的間距大于等于線寬的兩倍時,可以保證達到最壞情況下的串擾噪聲值控制在5%以下[10].由圖5可得:當布線空間較小時,可以采用2 W原則,當耦合線間距滿足2 W原則時,串擾的噪聲下降較多,可以滿足系統的設計要求.

圖5 串擾噪聲與耦合線間距關系曲線Fig.5 Crosstalk noise and coupling curve

3.4反射對串擾的影響

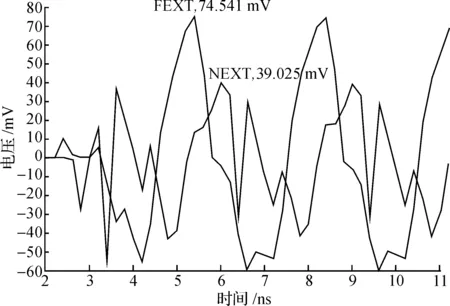

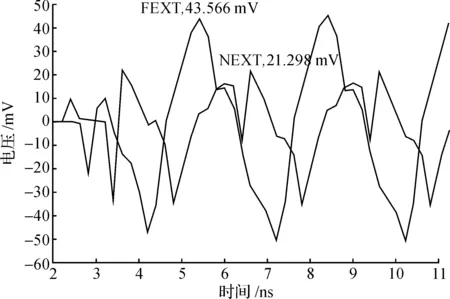

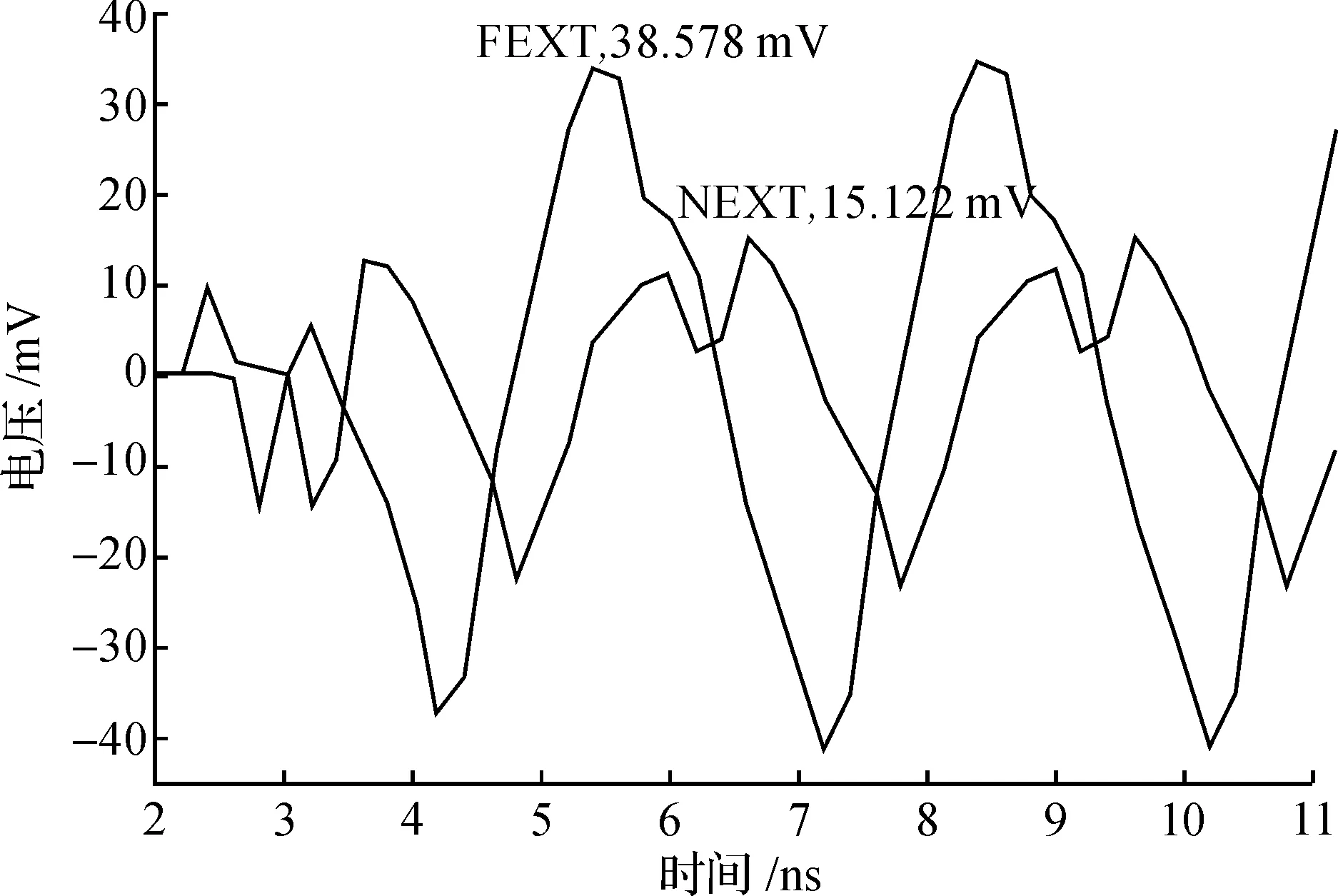

分別對于攻擊線及受害線采取都未端接電阻、僅攻擊線端接、僅受害線端接及攻擊線和受害線都端接電阻的情況下進行仿真,研究反射對于串擾的影響,圖6~8為不同端接情況下串擾噪聲的仿真結果.

圖6 都未端接Fig.6 All are without impedance matching

圖7 被干擾源未端接Fig.7 Victim line without impedance matching

圖8 全部串聯60 Ω電阻Fig.8 All series 60 Ω resistance

由圖6~8仿真結果可知:當未采取任何端接時,傳輸線上由于阻抗不匹配會引起反射問題,此時反射最大,串擾也是最大.當受害線與攻擊線都端接時,傳輸線實現了阻抗匹配,此時反射最小,系統串擾最小.

4結論

對DDR2 SDRAM互連線之間的串擾問題進行研究,理論分析了一些參數對于串擾的影響,通過Cadence公司的SigXplorer仿真軟件對PCB整板進行布線后仿真,根據仿真分析的結果可得減少串擾的一般規則:在布線空間允許的條件下,盡量加大相鄰走線之間的線間距,減小平行走線的長度;相鄰信號層的走線盡量垂直,以減小相鄰層的耦合;加入端接匹配電阻可以減小串擾的幅度;減小信號層與電源層或地層之間的介質厚度可以有效減小串擾;布線空間允許的條件下,對于高速信號提供包地可以減小兩條信號線間的耦合,進而減小串擾.

參考文獻:

[1]李勝朝,張江鑫.高速電路中時序問題的分析和處理[J].浙江工業大學學報,2009,37(5):499-502.

[2]郭德亮,郭淑琴,鮑衛兵.基于突發光信號的高速數據采集系統的設計與研究[J].浙江工業大學學報,2010,38(1):46-48.

[3]張松松,劉飛飛.高速電路板級信號完整性設計[J].電子·電路,2013,26(10):105-109.

[4]田廣錕,范如東.高速電路PCB設計與EMC技術分析[M].2版.北京:電子工業出版社,2008.

[5]李勝朝.基于Cadence的信號完整性設計及其在嵌入式系統中的應用[D].杭州:浙江工業大學,2009.

[6]DOUGLAS B. Signal integrity issues and printed circuit board design[M].劉雷波,趙巖,譯.1版.北京:機械工業出版社,2005.

[7]STEPHEN H H,HOWARD L H. Advanced signal integrity for high-speed digital designs[M].張徐亮,鮑景富,張雅麗,等譯.1版.北京:電子工業出版社,2011.

[8]安平凹,尹達一.CMV2000高速大面陣信號處理和完整性仿真分析[J].應用科技,2015,42(3):1-6.

[9]董輝,盧建剛,黃豪佑.Cadence高速PCB設計與仿真分析[M].5版.北京:北京航空航天大學出版社,2006.

[10]ERIC B. Signal Integrity:simplified[M].李玉山,李麗平,侯彥賓,等譯.2版.北京:電子工業出版社,2005.

(責任編輯:劉巖)

Research and simulation of DDR2 crosstalk based on the Cadence

DONG Hui, MA Zujie

(College of Information Engineering, Zhejiang University of Technology, Hangzhou 310023, China)

Abstract:With the increase of the operating frequency and the signal edge conversion rate, the influence of crosstalk on signal integrity is becoming more and more prominent. Through the analysis of the formation mechanism of the transmission line crosstalk, the Cadence simulation software is used to simulate the crosstalk of DDR2 SDRAM in the system, It gives a reasonable solution to the problem of crosstalk process. Based on the simulation analysis of the near-end crosstalk and far-end crosstalk of the data line, it can be concluded that the influence of crosstalk on the electric circuit can be reduced through reducing the coupling line length, increasing the spacing of coupling line, and reducing reflection. At the end of this paper, some effective measures to restrain crosstalk in PCB design are proposed. It will have some guidance for the design of signal integrity of DDR2 SDRAM.

Keywords:crosstalk; near-end crosstalk; far-end crosstalk; coupling

收稿日期:2015-11-19

作者簡介:董輝(1979—),男,浙江永康人,副教授,研究方向為嵌入式系統技術,E-mail:hdong@zjut.edu.cn.

中圖分類號:TN972

文獻標志碼:A

文章編號:1006-4303(2016)03-0266-04