一種L波段數(shù)字接收機(jī)的直接射頻采樣研究

戎喆希

【摘 要】隨著現(xiàn)代集成電路的發(fā)展,高速串行JESD204B協(xié)議及高速ADC令射頻直接采樣成為可能。本文對(duì)L波段數(shù)字接收機(jī)的直接射頻采樣進(jìn)行研究,基于新型ADC器件AD9625,提出與支持JESD204B軟核的FPGA協(xié)同工作的設(shè)計(jì)方案,在硬件設(shè)計(jì)不發(fā)生改變的條件下,分別支持在ADC內(nèi)進(jìn)行下變頻、抽取、濾波或在FPGA內(nèi)部進(jìn)行此項(xiàng)工作。兩種方式均屬數(shù)字處理,在處理不同回波信號(hào)時(shí)可通過(guò)軟件進(jìn)行調(diào)整。

【關(guān)鍵詞】射頻采樣;AD9625;JESD24B;L波段

【Abstract】With the development of modern integrated circuits, high-sped serial protocol JESD204B and high-speed ADC make direct RF sampling possible. In this paper the L-band direct RF sampling of digital receiver is studied. Based on new devices AD9625, the design conceptual came up. The ADC collaborates with FPGA which contains JESD204B core. The DDC, decimation and FIR can operate either in ADC or in FPGA without any change on the hardware. Both methods belong to the digital processing. It can be adjusted by software when deal with differential RF echo.

【Key words】RF sampling; AD9625; JESD204B; L-band

0 引言

L波段是頻率在1-2GHz的無(wú)線(xiàn)電電波波段,L波段接收機(jī)廣泛應(yīng)用于成像雷達(dá)、氣象雷達(dá)、探測(cè)雷達(dá)等系統(tǒng)中。傳統(tǒng)的超外差式接收機(jī)經(jīng)過(guò)一次或兩次下變頻,將射頻信號(hào)轉(zhuǎn)換為中頻信號(hào),之后用ADC對(duì)中頻信號(hào)進(jìn)行采樣。采樣過(guò)后的數(shù)據(jù)進(jìn)入FPGA內(nèi)部進(jìn)行后續(xù)處理。在濾波、低噪聲放大、混頻等過(guò)程中,模擬器件的不穩(wěn)定易導(dǎo)致I、Q兩路的幅相不一致,影響采樣結(jié)果。同時(shí)這些器件占用了大量的印制板版面,極大阻礙了接收機(jī)小型化的發(fā)展。

隨著射頻采樣技術(shù)的發(fā)展,用于數(shù)字T/R組件的射頻ADC發(fā)展成為必然。如采用TI公司的ADC083000進(jìn)行高速采樣[1]之后,通過(guò)四路多路輸出選擇器輸出每路8bit數(shù)據(jù)進(jìn)入FPGA,在FPGA內(nèi)進(jìn)行數(shù)字下變頻、正交變換、低通濾波等操作。本文提出了一種L波段數(shù)字接收機(jī)的直接射頻采樣設(shè)計(jì),利用先進(jìn)的ADC器件實(shí)現(xiàn)在數(shù)據(jù)進(jìn)入FPGA前完成數(shù)字下變頻、正交變換及低通濾波功能,通過(guò)JESD204B協(xié)議完成數(shù)據(jù)傳輸。此種方法不僅降低了輸出數(shù)據(jù)速率要求,也減小了FPGA內(nèi)部資源的占用。

1 數(shù)據(jù)采集方案

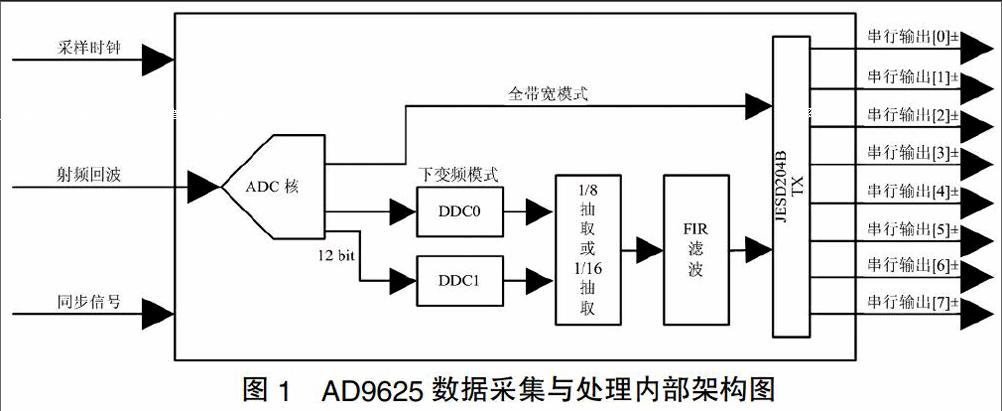

本文采用ADI公司生產(chǎn)的新型ADC器件AD9625,該芯片量化位數(shù)12 bit,采樣頻率高達(dá)2.5GSPS,差分模擬輸入1.1Vp-p,3.2GHz全功率模擬輸入帶寬,并且集成了兩路數(shù)字下變頻轉(zhuǎn)換器(DDC)、數(shù)控振蕩器(NCO)和FIR濾波器,支持高速6或8通道JESD204B串行輸出[2]。AD9625數(shù)據(jù)采集與處理內(nèi)部架構(gòu)圖如圖1所示。射頻回波經(jīng)ADC內(nèi)核進(jìn)行流水線(xiàn)采樣后,有兩種工作模式可以選擇。一種是經(jīng)過(guò)一級(jí)下變頻,抽取和濾波的下變頻模式。另一種是不經(jīng)過(guò)任何處理,直接通過(guò)ADC的發(fā)送器輸出的全帶寬模式。

1.1 下變頻模式

AD9625的兩個(gè)DDC中的調(diào)諧器由獨(dú)立的頻率合成器和正交混頻器組成,此時(shí)模擬信號(hào)已經(jīng)被提取為數(shù)字信號(hào)。本文以2.5GSPS采樣為例,10 bit頻率合成器支持1024個(gè)離散的調(diào)諧頻率,從-1.2499GHz到+1.2500GHz,步長(zhǎng)為2500/1024=2.44MHz。這樣1GHz~1.25GHz內(nèi)的回波可以在ADC內(nèi)搬移到零頻附近或任意想要的頻率。振蕩器的相位和頻率可在內(nèi)部寄存器0x132和0x131中設(shè)置。混頻之后的數(shù)據(jù)由12bit增加到13bit。為了降低復(fù)雜度并實(shí)現(xiàn)低時(shí)鐘速率,DDC采用8倍抽取多相融合濾波器,第一級(jí)濾波器級(jí)的降速系數(shù)是8,它在每個(gè)時(shí)鐘周期從混頻模塊接收8個(gè)13位樣本。抽取濾波器級(jí)工作在2.5GHz/8=312.5MHz,并與抽取后的采樣速率相等。經(jīng)過(guò)抽取后的縮放和舍入,數(shù)據(jù)位數(shù)增加到16bit。1/8抽取的濾波器帶寬為-120MHz到+120MHz。這之后的數(shù)據(jù)即可傳遞到發(fā)送器輸出。在對(duì)內(nèi)部寄存器相應(yīng)地址進(jìn)行配置后才可以使用第二濾波器級(jí),它額外實(shí)現(xiàn)2倍的降速系數(shù),由此得到總共1/16抽取。兩步抽取之后的采樣率156.25MHz,為了便于物理設(shè)計(jì),該模塊以250MHz的速率工作。抽取濾波器的帶寬為-60 MHz到+60MHz。

對(duì)于1GHz~1.25GHz的回波,ADC采樣的數(shù)據(jù)經(jīng)過(guò)1/8抽取,再經(jīng)過(guò)8B/10B編碼送發(fā)送端,使用8線(xiàn)傳輸模式,數(shù)據(jù)傳輸線(xiàn)速率為2.5G×16÷8×10÷8÷8=781.25Mbps

8條通道總計(jì)6.25Gbps。若經(jīng)過(guò)1/16抽取,數(shù)據(jù)傳輸線(xiàn)速率為:

2.5G×16÷16×10÷8÷8=390.625Mbps

8條通道總計(jì)3.125Gbps。

1.2 全帶寬模式

當(dāng)下變頻模式的工作過(guò)程或處理結(jié)果不能滿(mǎn)足設(shè)計(jì)需求時(shí),可以啟用全帶寬工作模式。經(jīng)過(guò)ADC內(nèi)核采樣過(guò)的信號(hào)不加處理的傳遞到發(fā)送器端。全帶寬模式要考慮印制板的數(shù)據(jù)承載能力以及后續(xù)數(shù)據(jù)流處理算法。ADC芯片的12 bit樣本可按寄存器配置加入控制位或補(bǔ)齊尾碼組成16 bit,組成一幀后按8B/10B編碼送發(fā)送端。按發(fā)送端8線(xiàn)傳輸模式,線(xiàn)速率為:

2.5G×16×10÷8÷8=6.25Gbps

2 樣系統(tǒng)硬件設(shè)計(jì)

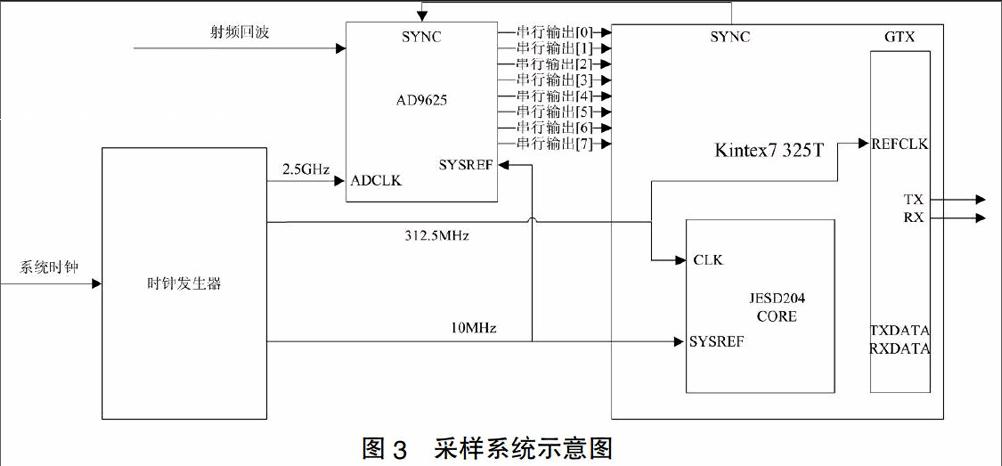

本設(shè)計(jì)中,F(xiàn)PGA選用Xilinx公司的Kintex7系列325T芯片。為了保證在全帶寬模式下接收機(jī)也能正常工作,將ADC的高速串行輸出接入FPGA的GTX。Kintex7系列325T芯片最多含有16個(gè)GTX接口,最高可達(dá)單線(xiàn)12.5GBPS的傳輸速率,可以滿(mǎn)足設(shè)計(jì)需要。基于FPGA構(gòu)建采樣系統(tǒng)示意圖如圖3所示。SYSREF信號(hào)用于使ADC的輸出端到FPGA的輸入端之間產(chǎn)生確定性的延遲[3]。SYNC信號(hào)用來(lái)啟用代碼組同步和初始lane同步(ILAS)狀態(tài)以完成JESD204B協(xié)議下的高速串行傳輸。

3 采樣系統(tǒng)軟件設(shè)計(jì)

FPGA通過(guò)JESD204B核完成接收任務(wù),如圖4所示,在配置界面設(shè)置接收/發(fā)送器的通道數(shù),SYSREF采樣沿、AXI4時(shí)鐘以及JESD204 PHY等參數(shù)。設(shè)置好之后,編程輸出合適的SYNC脈沖信號(hào),所有的同步、確定幀頭和數(shù)據(jù)收發(fā)的工作都由IP核來(lái)完成[4]。

在FPGA和ADC同步完成之后,通過(guò)SPI方式配置AD9625。AD9625提供多種靈活的輸出測(cè)試模式,首先將0x61寄存器的[5:4]位配置為01,令10 bit JESD204B測(cè)試數(shù)據(jù)進(jìn)入ADC的發(fā)送器,確認(rèn)FPGA端接收數(shù)據(jù)無(wú)錯(cuò)誤,保證發(fā)送鏈路層工作正常。然后將0x61的[5:4]位配置為00,補(bǔ)全后的16 bit JESD204B測(cè)試數(shù)據(jù)進(jìn)行組幀、加擾、8B/10B編碼后通過(guò)發(fā)送端輸出。確認(rèn)FPGA端接收數(shù)據(jù)無(wú)錯(cuò)誤,保證應(yīng)用層工作正常。最后配置0x0D,令12 bit ADC測(cè)試數(shù)據(jù)輸入ADC內(nèi)核,測(cè)試ADC轉(zhuǎn)換器工作是否正常。所有測(cè)試完成之后,即可對(duì)工作信號(hào)進(jìn)行采樣處理。除此之外,為了防止ADC的輸入長(zhǎng)時(shí)間處于飽和狀態(tài),配置快速檢測(cè)閾值,通過(guò)觀察快速檢測(cè)位調(diào)整回波輸入功率。也可以通過(guò)配置JESD204B相關(guān)寄存器,令A(yù)DC工作在下變頻模式或全帶寬模式,修改DDC量及增益、發(fā)送數(shù)據(jù)格式等。

4 結(jié)束語(yǔ)

本文設(shè)計(jì)了一種L波段的射頻采樣平臺(tái),在同樣的硬件條件下,分別可以通過(guò)ADC或FPGA完成下變頻、抽取和濾波的功能。對(duì)于和AD9625類(lèi)似的芯片都可以采用本文中的思路進(jìn)行設(shè)計(jì)。

【參考文獻(xiàn)】

[1]黃杰文,李楊,禹衛(wèi)東.直接射頻采樣的L 波段星載SAR 數(shù)字接收機(jī)設(shè)計(jì)[J].中國(guó)科學(xué)院研究生院學(xué)報(bào),2010.27(4):486-491.

[2]AD9625Datasheet.Analog Device,2014[Z].

[3]JEDEC STANDARD. JEDEC solid state technology association,2012.1[Z].

[4]JESD204 v6.1 LogiCORE IP Product Guide. Xilinx. April 1,2015[Z].

[5]陳洋,俞育新,奚俊.基于JESD204B 協(xié)議的相控陣?yán)走_(dá)下行同步采集技術(shù)應(yīng)用[J].雷達(dá)與對(duì)抗,2015.32(2):38-48.

[責(zé)任編輯:王偉平]