基于FPGA與ML7204的音頻編解碼設計*

吳 偉 張 禹

(中國電子科技集團公司第二十八研究所 南京 210002)

?

基于FPGA與ML7204的音頻編解碼設計*

吳偉張禹

(中國電子科技集團公司第二十八研究所南京210002)

摘要通信系統中的語音編解碼多基于DSP來實現,采用相應的DSP硬件設計及軟件算法,可以較方便地實現多路語音處理。而在某些小型的G.729格式的通信系統中,采用硬件編解碼的模式,結合FPGA來協同設計,可以將語音編解碼更為方便地應用在通信系統的終端設備中,大大減少了設備設計的復雜度。

關鍵詞編解碼; G.729; 音頻處理; PCM

Class NumberTN95

1引言

在通信系統中,需要將通信雙方的模擬信號通過數字化方式進行傳輸、交換,然后送達對方再將數字信號轉換為模擬信號。在這一過程中,由于系統帶寬的限制,需要對數字化以后的信號進行編碼,以減少帶寬的占用,在語音通信系統中,常采用G.729的編解碼方式。在部分產品的開發設計中,利用ML7204硬件編解碼器(code and decode, CODEC)配合現場可編程門陣列(Field-Programmable Gate Array, FPGA)設計,實現了實時與可靠的數據傳輸,充分控制了研發風險,有效降低了設計成本,縮短了產品開發周期。

2ML7204簡介

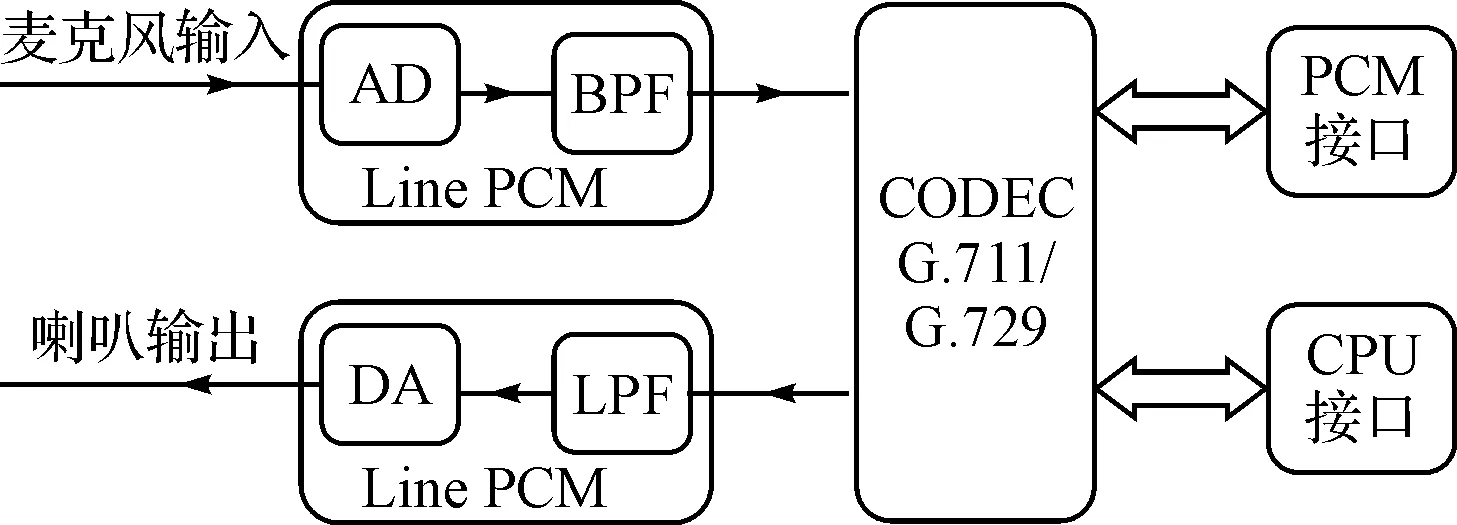

ML7204是OKI公司基于網絡電話(Voice over Internet Protocol,VoIP)的場景應用開發的一款面向中小型系統的模塊,芯片支持雙路G.711-A/μ的編解碼或者單路G.729-A編解碼。其內部信號處理的流程如下:模擬音頻信號通過模擬數字轉換器(Analog to Digital,AD)進入CODEC,由數字帶通濾波器處理后生成16bits線性脈沖編碼調制(Pulse Code Modulation,PCM),進入語音編碼模塊進行G.711&G.729編碼,然后在接收Buffer中緩存生成的數字語音包;從上級接口進入發送Buffer的數字語音包,送達語音解碼模塊進行G.711&G.729解碼,然后通過數字低通濾波器,通過數字模擬轉換器(Digital to Analog,DA)還原為模擬信號。信號處理流程如圖 1所示。

另外,ML7204還提供了許多面向語音業務的附加功能,包括回聲抑制,頻移鍵控(Frequency-Shift Keying,FSK)、雙音多頻(Dual Tone Multi-Frequency,DTMF)和話音(TONE)的生成與檢測等。

圖1 CODEC內部處理流程框圖

3硬件系統設計

硬件系統的設計采用了FPGA做處理芯片來完成ML7204的初始化配置及后續的數據收發等工作。

ML7204的控制接口為通用異步總線接口,可由中央處理器(Central Processing Unit,CPU)或者其他控制器進行訪問。一般通過地址映射的方式,將CODEC內部寄存器交由控制器讀寫控制,從而將系統需要的模式、 功能一一配置, 完成相關功能,同時收發語音數據。也可采用PCM接口來收發語音數據,以方便和多通道緩沖串行接口(Multi-channel Buffering Serial Port,McBSP)等上級接口互聯。

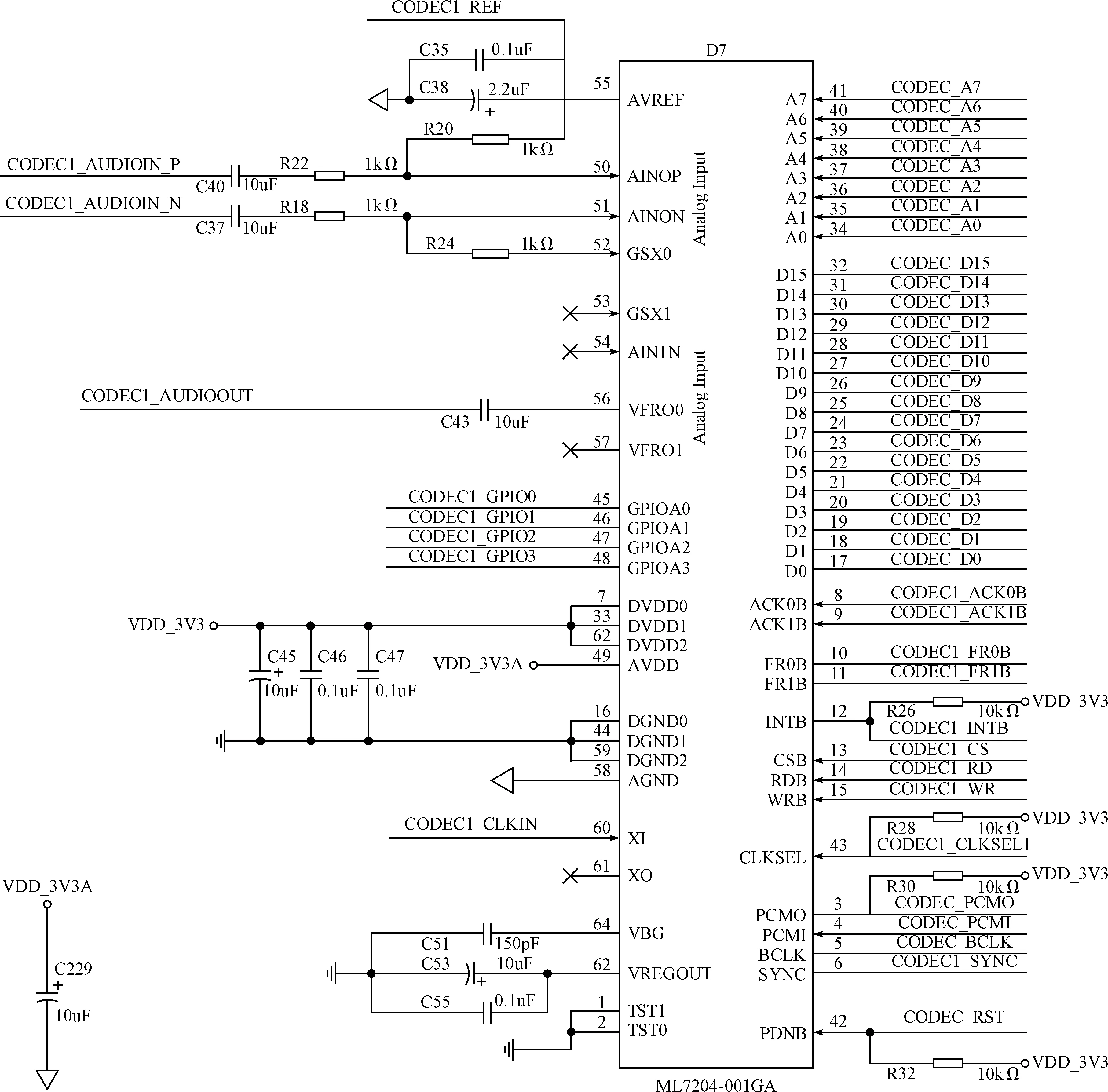

硬件設計上,模擬與數字部分的電源、地線是分離的。在模擬部分,語音輸入信號為差分信號,通過10uF電容進行交流耦合,并采用模擬信號的地線引腳AVREF和1kΩ電阻網絡對信號進行整流,以提高其信噪比。音頻信號輸出為單端信號,也采用10uF電容隔斷直流分量;數字信號部分,根據硬件管腳的定義,先進行工作模式硬件配置,然后將異步總線的16位數據、8位地址及控制線,PCM接口的信號線等連接至FPGA的輸入輸出(Input and Output,IO)管腳,完成FPGA與CODEC的硬件互聯。ML7204的硬件設計如圖2所示。

圖2 ML7204硬件原理圖設計

4軟件系統設計

為完成底層模擬信號與上層數字信號的轉換,通過Verilog硬件描述語言設計FPGA程序來實現對ML7204的控制,其中FPGA為主機,ML7204為從機。

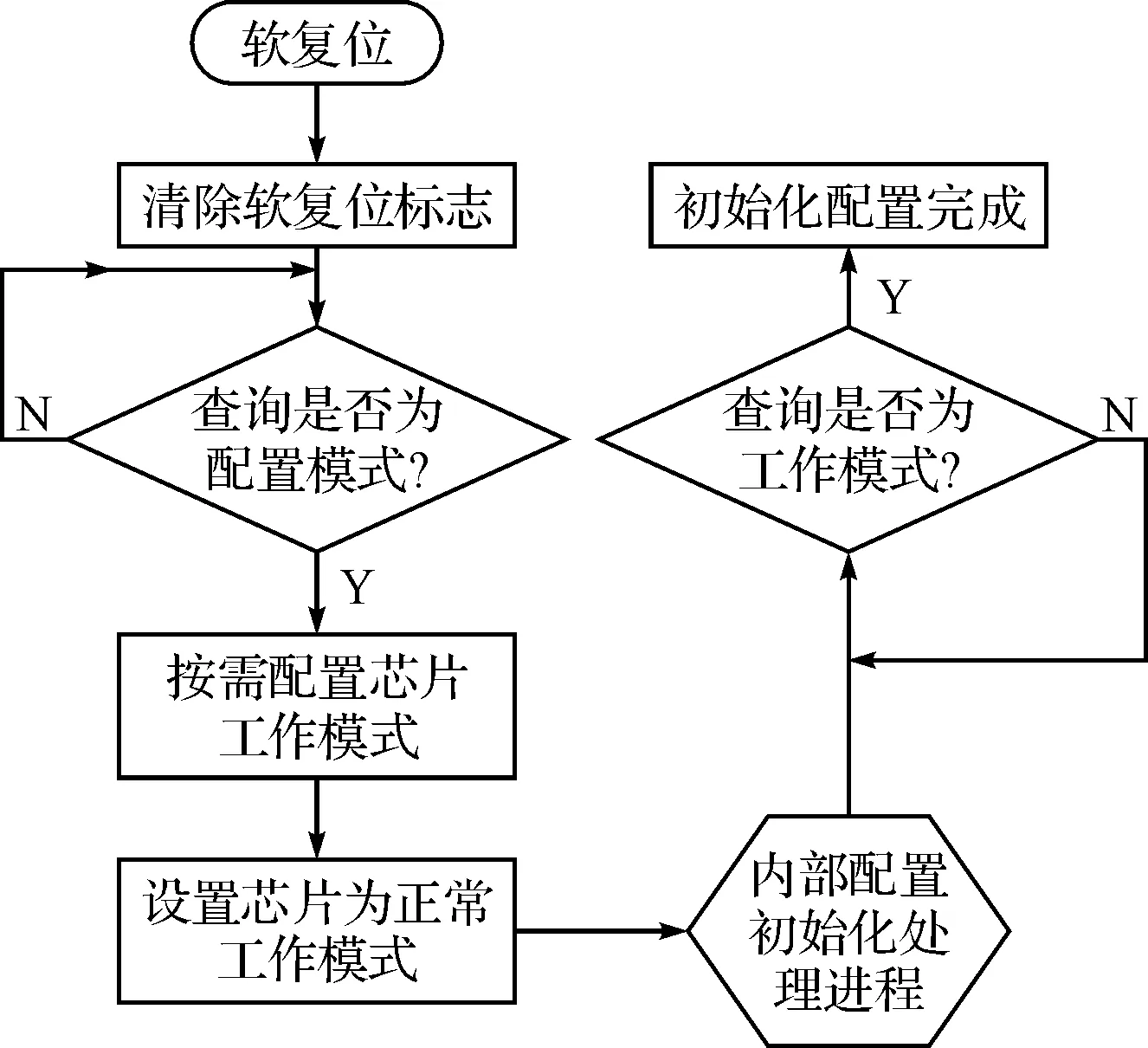

首先,對ML7204進行初始化配置。ML7204內部含有CR0-CR47等基本的控制寄存器以及通過CR寄存器的功能擴展所映射的內部數據空間。CODEC初始化所用的寄存器,除了CR0、CR5用來配合相關的延時、查詢等操作以控制芯片時序邏輯外,還需要將CR13、CR31、CR23以及CR10按照功能寫入配置字。上述寄存器對應著編解碼格式和幀時長、信號路徑的控制、編解碼器工作使能和語音輸出使能等功能控制。

在本次的設計中,依次配置如下:采用G.729-A率編解碼,10ms一幀的工作模式;規劃音頻0通道的模擬輸入信號傳遞路徑;使能CODEC-A編解碼器,關閉CODEC-B模塊;使能音頻0的模擬輸出信號,關閉音頻1的模擬輸出信號。該部分的配置僅僅是實現芯片最基本編解碼功能,拓展的功能還需添加其他寄存器或內部隨機訪問存儲器(Random Access Memory,RAM)區配置。

ML7204的初始化流程如圖3所示。

圖3 硬件CODEC軟件配置流程圖

其次,經過上述對寄存器的配置,CODEC芯片已經正常工作,并開始收發語音數據。當編碼器從模擬端收到數據,開始編碼并緩存10Bytes后,接收Buffer給出滿標志,此時芯片的FR0引腳拉低,FPGA采集到該標志后,執行主機接收數據操作;當Buffer從總線接口收到的10Bytes數據,完全發送給解碼器后,發送Buffer給出空標志,驅動FR1引腳拉低,此時FPGA采集到該標志,執行主機發送數據操作。

為更簡明便捷地驅動CODEC工作及后續功能擴展,設計了FPGA的狀態機,并逐層封裝了信號驅動和數據處理的底層操作。在頂層狀態機的設計上,除去為狀態機基本流程而設計的初始化態和空閑態以外,還分為功能調度、信息處理和底層驅動三大應用部分。

功能調度態的功能為:整合外部程序模塊產生的信息,適時調整調度優先級,產生信號量,從而控制FPGA完成狀態機在頂層狀態的遷移,并提供下一級狀態機跳轉方向。優先級的動態調整算法由程序的其他模塊處理。部分程序偽碼如下

mode_sched:

if((schd ==idle) && (work_seq!= null)) /*判斷是否有新的調度請求*/

mode_ status<= mode_proc;

else

mode_ status <= mode_schd;

case(schd_order)/*執行調度,根據動態調度算法產生的優先級進行響應,并給后一級狀態信息量賦值,選擇處理類型*/

order_pri1:

work_seq<= CODEC_initial;

信息處理態的作用是:結合CODEC芯片的初始化流程、數據收發流程設計數據的傳遞方式組合。狀態機執行到該運行態,通過上層傳遞過來的信號量去選擇何種處理類型。處理類型分為CODEC_initial,CODEC_busy,CODEC_idle,CODEC_halt,DATA_send,DATA_recv等。以初始化進程CODEC_initial狀態為例,部分程序偽碼如下:

mode_proc:

case(work_seq)

CODEC_initial:

case(CONF_seq)

CONF_seq1:

codec_cs<= CHIP_csX;

codec_addr <= CODEC_crX;

codec_sdata <=CONF_data;

work_mode <= mode_drv;

bus_ type<= BUS_wr;

CONF_seq <= CONF_seq2;

底層驅動態接收上層狀態機傳遞過來的異步總線控制參數,通過時序邏輯控制,完成數據讀寫的操作,控制時序分為BUS_rd和BUS_wr,通過CODEC_BUS_outen信號來控制總線的三態門。操作完畢后,返回上一級狀態機,即信息處理態。總線控制時序相對簡單,本文不再細述,關鍵在于和狀態機的各級遷移信號結合,并逐層封裝起來,給上層狀態機邏輯模塊調用。

另外還需說明一點的就是先入先出存儲器(First In First Out,FIFO)的設計。系統在G.729音頻格式,10ms幀長時,每次中斷產生10Bytes數據,而在G.711格式,20ms幀長時,每次產生160Bytes。由于CPU調度、底層驅動資源分配等問題,在某些情況下,尤其是在多路CODEC并行工作,CPU負荷加重時,會導致數據的丟失和時延的增大。為充分降低語音的時延和誤碼率,提高數據傳輸的效率,本次設計采用FIFO進行數據緩存,同時設計算法適時調整優先級,以保證語音的傳輸質量。根據上文的配置,在CODEC側每10ms就會有一個語音數據幀產生,10Bytes,同時拉低FR0信號。狀態機在通過各級功能調度后,最終實現該功能的部分偽碼如下:

CONF_seq4:

if(fifo_num_cnt CONF_seq <= CONF_seq5; else CONF_seq <= CONF_seq8; CONF_seq5: codec_cs<= CHIP_csX; codec_addr <= CODEC_crX; codec_sdata <=CONF_data; work_mode <= mode_drv; bus_ type<= BUS_wr; CONF_seq <= CONF_seq6; CONF_seq6: fifo_recv_cnt <= fifo_recv_cnt+1; if(fifo_recv_cnt == 0) rxfifo_ery1<= codec_rdata; if(fifo_recv_cnt == 2) rxfifo_wq1<= 1; if(fifo_recv_cnt == 3) rxfifo_wq1<= 0; if(fifo_recv_cnt == 4) fifo_recv_cnt<= 0; CONF_seq<= CONF_seq7; CONF_seq7: fifo_num_cnt<= fifo_num_cnt + 1; CONF_seq <= CONF_seq4; CONF_seq8: fifo_num_cnt<= 0; CONF_seq<= CONF_seq1; work_status<= mode_schd; FIFO采用了FPGA自帶的IP核,配置為16Bit位寬,256-words深度。在IP核例化時,讀寫接口時鐘分別根據FPGA主狀態機時鐘,FPGA與CPU接口控制時鐘來選定,同時FIFO的數據、控制接口對接到FPGA相應狀態機的模塊。 當然上述的程序模塊只描述了最基本的模塊實現和相互之間的應用關系,在實際的產品工程化中,還牽涉到硬件CODEC更進一步配置,模塊調度動態調整算法以及PCM接口模塊的程序融合等設計。 5結語 FPGA由于并行處理,實時性高,所以在某些對時延較為敏感的場合尤為適用。本次設計并沒有像以前的產品案例中,加入FPGA軟核來工程實施,而是采用了Verilog語言來開發,這樣對底層邏輯控制較好,適當優化數據通路后,能夠在一定程度上提高數據吞吐率,降低延時。對某款設計支持6路CODEC的產品進行測試,以20ms,G.711-A的SIP系統為例,理想實驗室環境下,話音時延約為50ms;在音頻質量測試子項中,系統的總諧波失真(Total Harmonic Distortion,THD)為-40dB左右。 另外在低成本應用場合,可能僅僅需要處理1到2路音頻數據,且也不牽涉到混頻算法,數字信號處理器(Digital Signal Processor, DSP)多路編解碼的優勢并沒有得到充分發揮,因此在高性價比設備設計,相關算法技術開發人員不足卻需要快速推出市場應用等場合,本次基于硬件CODEC的設計尤為適用,并已在產品應用中產生了較好的經濟效益。 參 考 文 獻 [1] 楊曉東,鄭樹強.語音編碼在IP調度系統中的應用研究[J].計算機網絡,2014(6):61-63. [2] 張忠慧,方元.語音編碼方案客觀評價[J].計算機應用,2014,34(S1):265-267. [3] 于增貴.ITU-T 8kbps語音編碼標準介紹[J].通信技術,1997(4):62-65. [4] 金靜,張天騏,萬義龍等.TETRA與G.729語音編碼算法的比較研究[J].電視技術,2013,37(15):168-172. [5] 楊貴新,谷志峰.G.729語音編碼算法研究及基于DSP的實現[J].單片機及嵌入式系統應用,2012(5):9-12. [6] 郭俊利.數字集群通信系統的接入分析與容量估算[J].無線電通信技術,2014,40(1):14-17. [7] 金輝,陳后金,孫江波.VoIP語音編解碼器的實現與優化[J].北京交通大學學報,2005,29(2):85-87. [8] 李志國,李喬.車載話音集中控制器中VoIP網關技術實現[J].指揮信息系統與技術,2012,3(2):61-65. [9] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008:166-192. 收稿日期:2016年1月2日,修回日期:2016年2月11日 作者簡介:吳偉,男,工程師,研究方向:嵌入式系統的軟硬件設計,通信網和以太網接入設備。張禹,男,碩士,工程師,研究方向:模擬電路、電源技術研究,高速A/D、D/A。 中圖分類號TN95 DOI:10.3969/j.issn.1672-9730.2016.07.017 Speech CODEC Design Based on FPGA and ML7204 WU WeiZHANG Yu (The 28th Research Institute of China Electronics Technology Group Corporation, Nanjing210002) AbstractSpeech CODEC in voice communication system is usually processed by DSP. Designing DSP hardware circuitry and software arithmetic will solve speech of multi-channels more conveniently. However, in some G.729 format, low-cost information systems, a module of hardware CODEC cooperating with FPGA will realize Speech CODEC more easily in the communication terminal designing and reduce the complexity of embedded system engineering. Key WordsCODEC, G.729, speech process, PCM