基于DE0的測溫系統的設計*

聶 云 劉昌華 鄒 翰 王 慧

(武漢輕工大學數學與計算機學院 武漢 430023)

?

基于DE0的測溫系統的設計*

聶云劉昌華鄒翰王慧

(武漢輕工大學數學與計算機學院武漢430023)

摘要使用DE0開發板以及一個溫度傳感器DS18B20,來實現溫度的采集與顯示。介紹了溫度傳感器DS18B20的接口原理和操作時序,闡述了系統組成的硬件電路和軟件設計。使用EP3C16F484C6作為主控芯片,使用Verilog HDL硬件描述語言設計狀態機,根據單總線協議完成FPGA對DS18B20溫度傳感器的復位、數據讀、數據寫的操作,完成測量溫度的功能。并將測量的二進制溫度數據轉換為BCD碼,通過數碼管顯示。利用Quartus II 13.0軟件自帶的邏輯分析儀Signal Tap II進行仿真。

關鍵詞DE0開發板; DS18B20傳感器; 單總線協議; Verilog HDL

Class NumberTP391

1引言

溫度控制已被廣泛應用于生活各個領域,如在軍工、食品、農業生產等方面。在這些領域對溫度的要求很高,如果溫度超出規定范圍,會造成很多不利于生產的影響。DS18B20是美國DALLAS半導體公司生產的1-Wire系列的高精度數字溫度傳感器,溫度測量范圍為-55℃~+125℃,可設置9位~12位A/D轉換精度,最小的分辨率為0.0625℃。單總線協議是Dallas公司的專利,與其他通用的串行數據通信方式不同,它只用一根信號線,傳輸時鐘和數據,傳輸數據時是雙向口。具有很多優點,例如節省接口資源、便于在總線上擴展多個傳感器等。結合FPGA器件強大的并行處理能力、功耗低等優點,所以選擇FPGA與DS18B20結合來實現該測溫系統[1]。

本設計采用Altera公司的Cyclone III系列芯片EP3C16F484C6和DALLAS公司的DS18B20[9]組成的測溫系統,DS18B20采集被測物體的溫度,FPGA通過讀取單總線的數據,最后把溫度數據傳送給數碼管顯示。該測溫系統硬件電路簡單,應用范圍廣泛,易于擴展,有廣闊的應用前景。

2數字溫度傳感器DS18B20

2.1DS18B20的內部結構

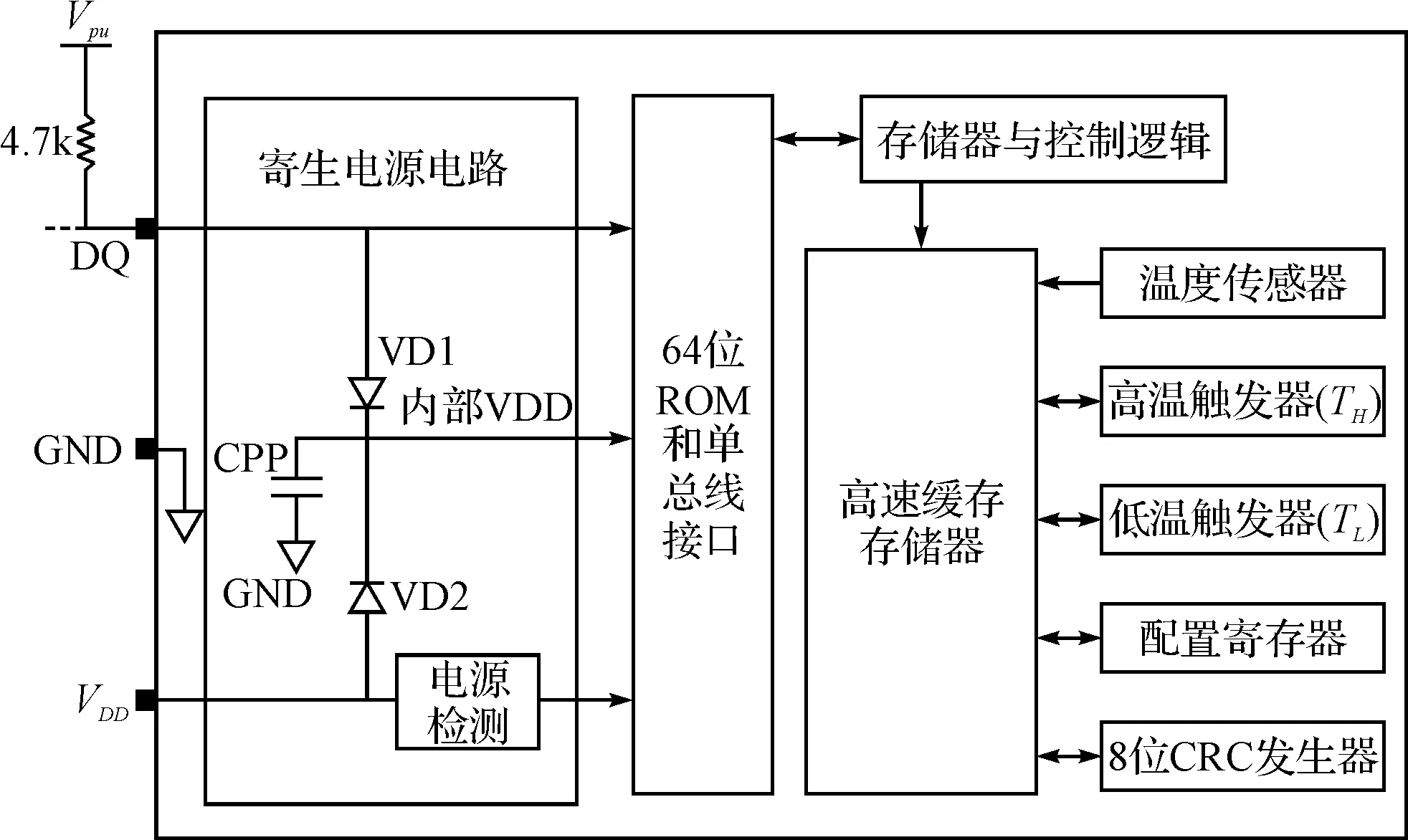

DS18B20內部結構如圖1,主要由下面幾個部分組成:64位ROM、溫度傳感器、非揮發的溫度報警器TH(高溫)和TL(低溫)、配置寄存器、暫存寄存器(SCRATCHPAD)、存儲器與控制邏輯。DQ為溫度傳感器與外部器件傳輸數據與時鐘的引腳。其中64位ROM中有64位序列號(8位產品家族編號、48位ID號、8位CRC),該序列號是出廠前刻好的,而且每個DS18B20的序列號是不同的。

圖1 DS18B20內部結構圖

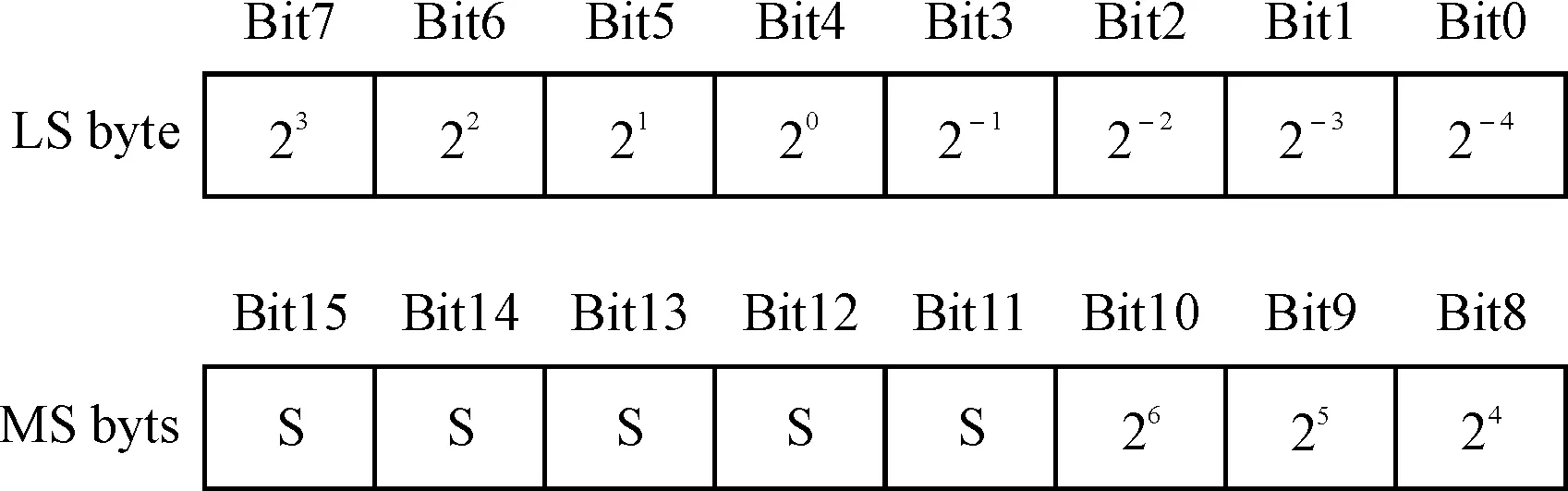

DS18B20加電后,處在空閑狀態。溫度傳感器的操作分為啟動溫度轉換和讀取溫度兩個過程。在啟動溫度轉換階段,當DE0向其發出Convert T[44H]命令后開始模數轉換,轉換完后,溫度數據以二進制補碼存儲在溫度寄存器中,溫度寄存器格式如圖2。

圖2 溫度寄存器格式

LS byte存儲溫度的低8位,MS byte存儲溫度的高8位,高8位中的前5位都為符號位,說明溫度的正負狀態,當溫度為正值時S為0,溫度為負值時S為1[2]。

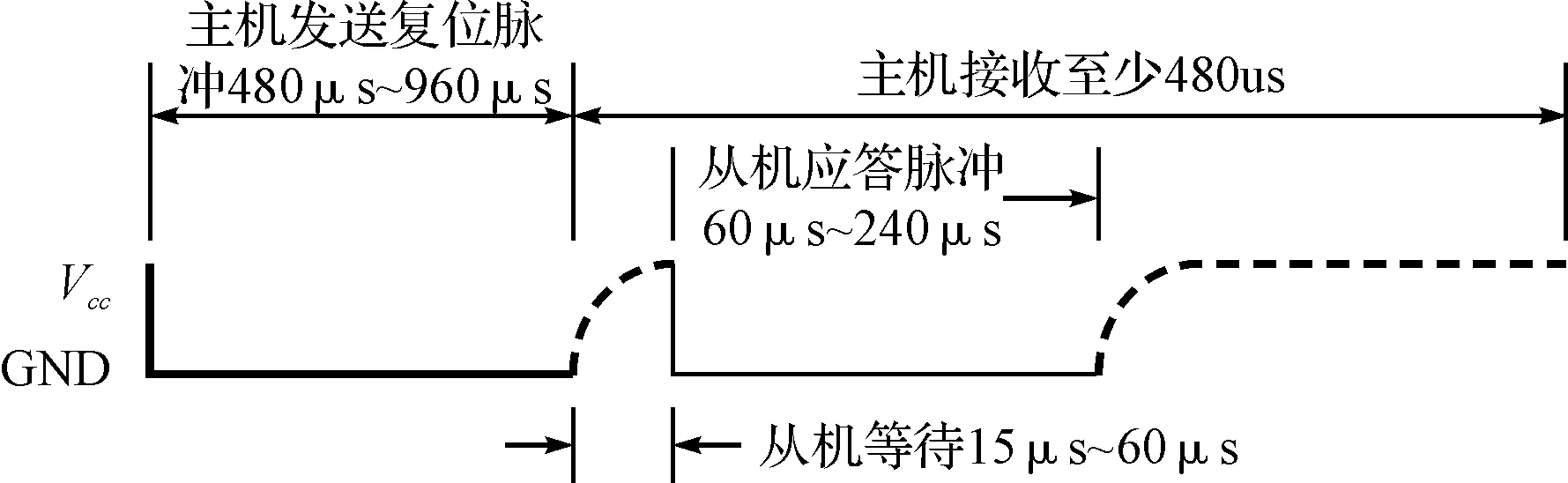

表1為DS18B20溫度/數據的對應關系表,該表給出的溫度范圍為-55℃~125℃。DS18B20在上電復位時,溫度寄存器的初始值是85℃。

2.2DS18B20的操作時序

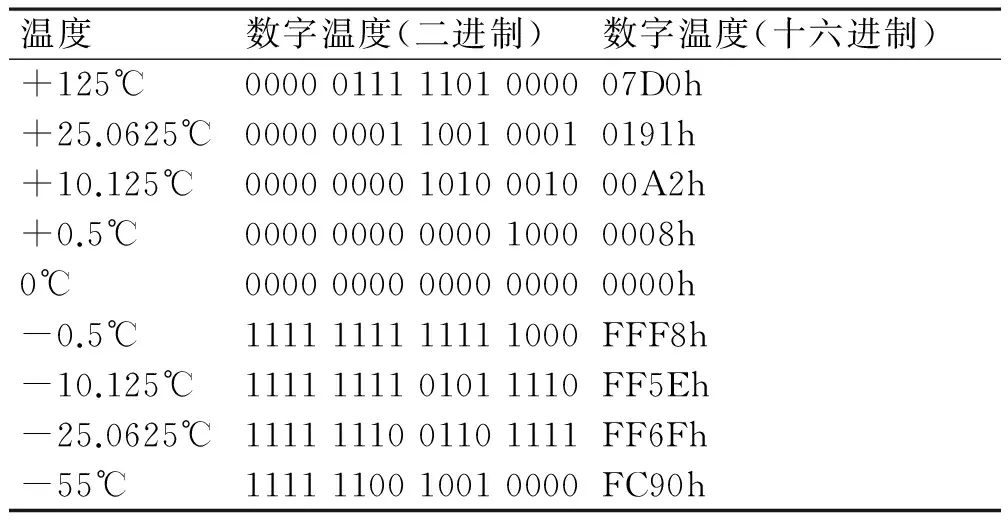

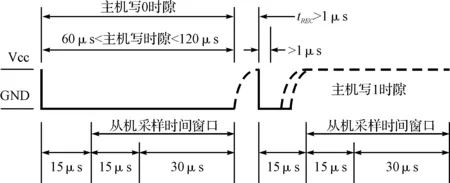

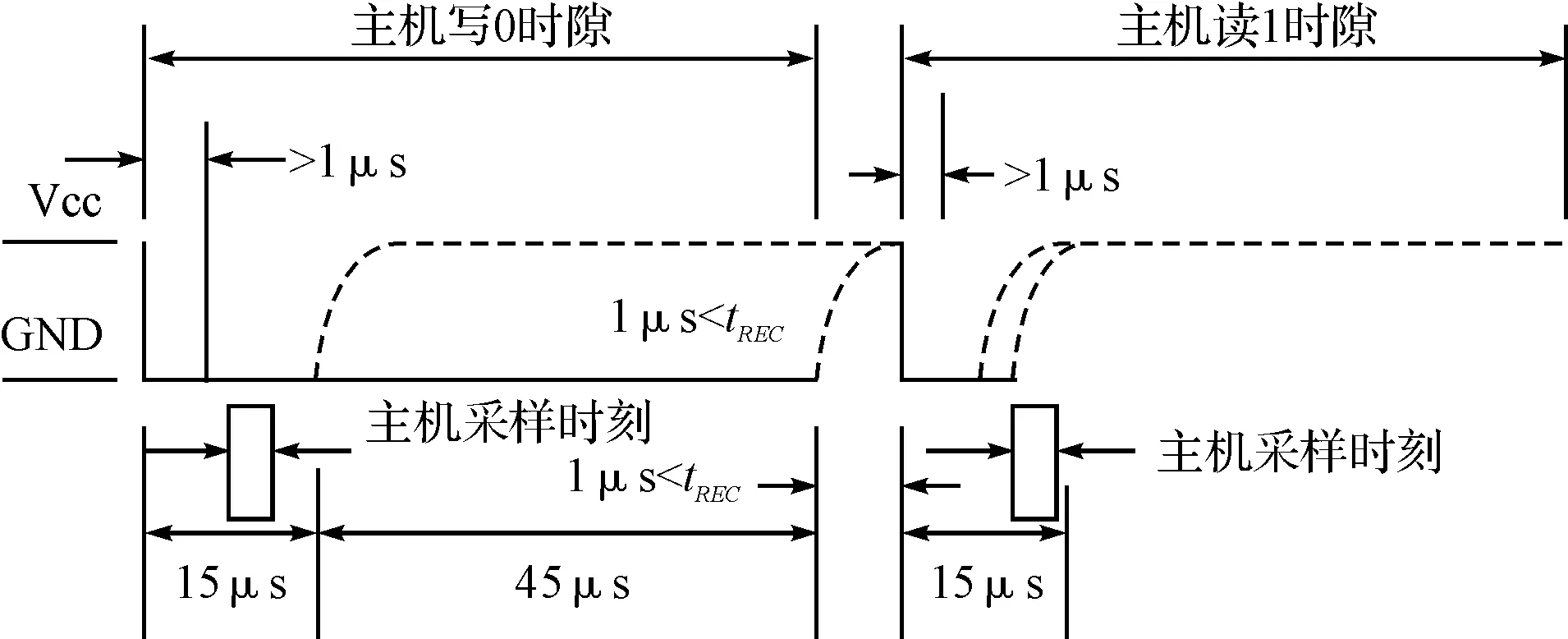

圖3為DS18B20操作的初始化時序,圖4為寫操作時序,圖5為讀操作時序。單總線協議器件嚴格按照時序進行操作。本文用Verilog HDL硬件描述語言[3]編寫有限狀態機程序,由主控芯片發出同步信號,發送命令和數據都是以bit為單位,而且是以低位在前高位在后的形式。

表1 DS18B20溫度/數據的關系

圖3 傳感器初始化時序

FPGA在開始時刻發送一復位脈沖(最短為480μs的低電平信號),經過480μs~960μs的低電平之后釋放總線并進入接收狀態[4],DS18B20在檢測到總線的上升沿之后,等待15μs~60μs,接著DS18B20發出響應脈沖(低電平持續60μs~240μs),如圖3中黑粗線所示。

當寫入命令到DS18B20時,DE0將數據總線從高電平拉至低電平后,就產生寫時間隙。如圖4,拉低總線15μs內應將數據位送到總線上[5]。DS18B20在開始時刻后15μs~60μs間對總線進行采樣,若采樣的電平為低電平,則寫入的位是0;若為高電平,則寫入的位是1。連續寫2位間的間隙應大于1μs,每寫一位的時隙至少為60μs。

圖4 傳感器寫時

當從DS18B20讀取數據時,DE0把數據總線從高電平拉至低電平并保持1μs,然后釋放總線。來自DS18B20 的輸出數據在下降沿后15μs有效。在讀取數據結束時I/O引腳應拉回到高電平,沒讀取一位的時隙至少為60μs,如圖5。

圖5 傳感器讀時

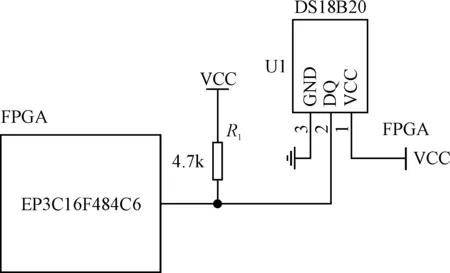

3DE0與DS18B20的連接

DS18B20支持寄生電源供電,在總線為高電平時,DS18B20的內部電容會總線上獲得電荷;在總線為低電平,內部電容可以供電。但在溫度變換期間,I/O引腳電流較大,如果在該I/O引腳上保持高電平,會對FPGA芯片引腳造成很大壓力。所以使用VCC引腳接外部電源,DS18B20的數據線與DE0開發板的GPIO 0口的GPIO0_D0口連接,如圖6所示[6]。

圖6 DS18B20與DE0的連接電路圖

4軟件設計

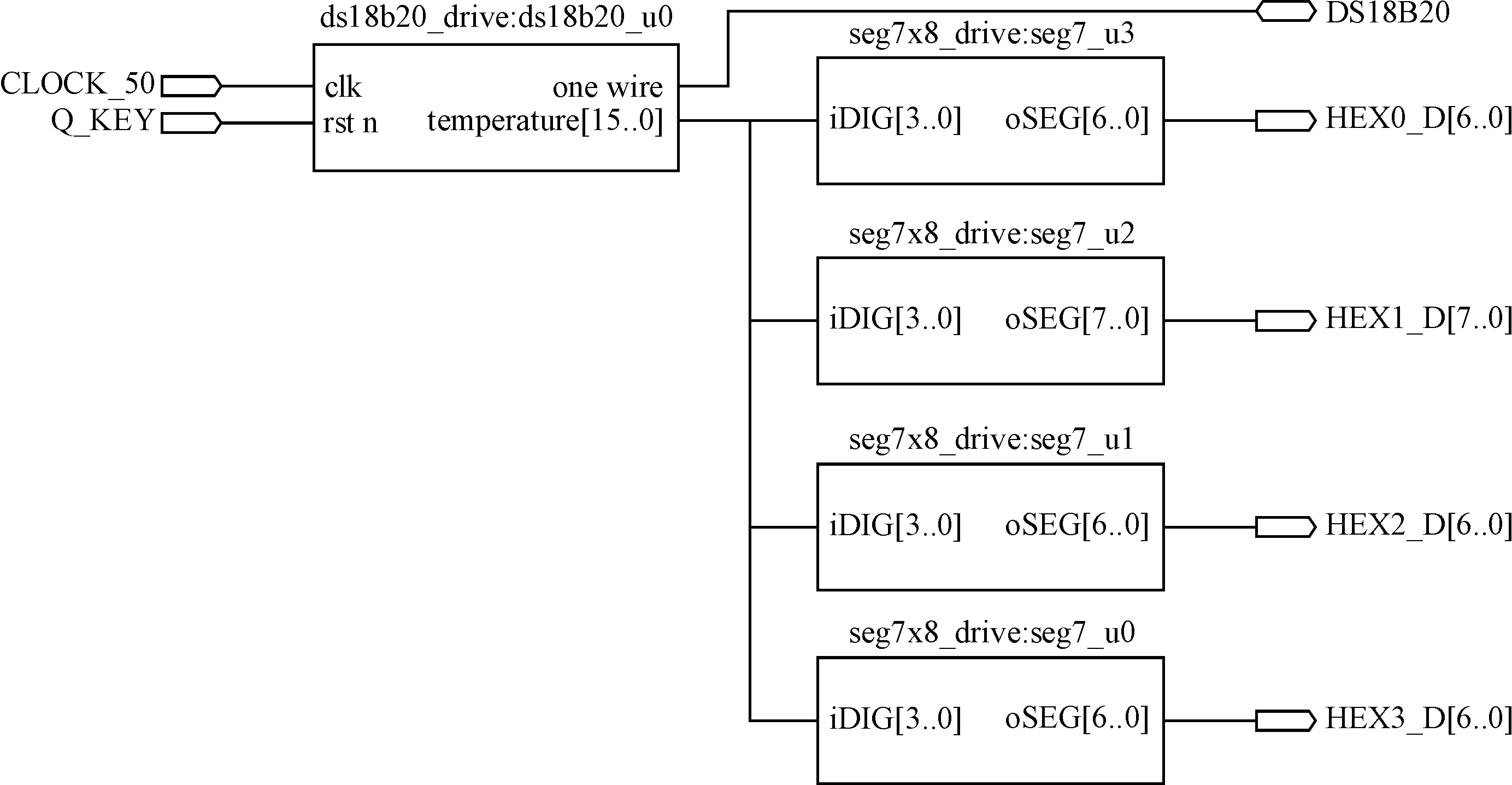

根據系統的要求,將軟件設計分為三個模塊,包括DS18B20的驅動模塊、數碼管顯示模塊、溫度顯示頂層模塊。利用Verilog HDL語言[7]在Quartus II13.0開發平臺上完成程序設計。其RTL圖如圖7所示。

圖7 測溫系統的RTL電路圖

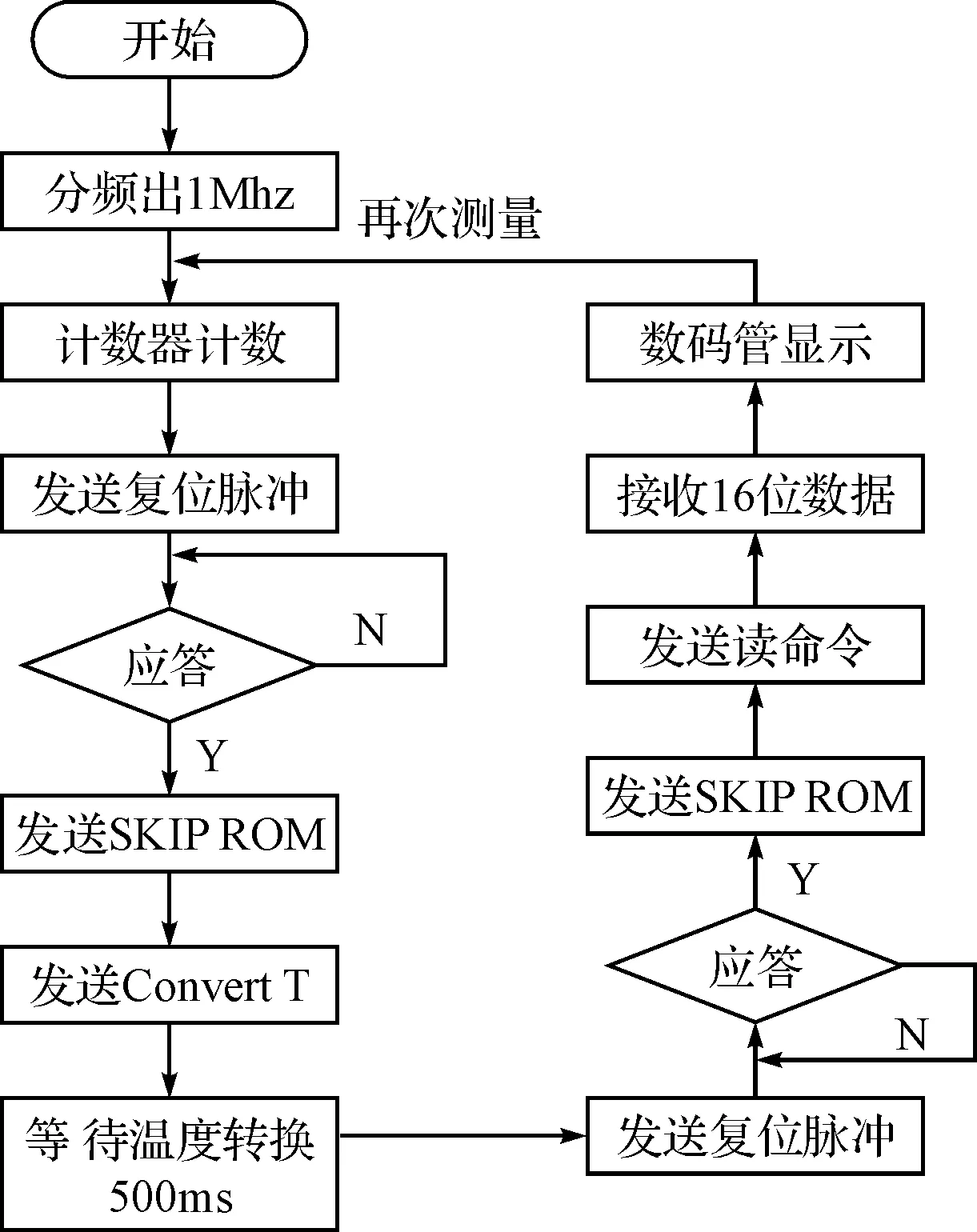

單總線協議通信器件,其硬件電路簡單,相對的軟件設計過程比較復雜。 通過對DS18B20功能的分析可知,DE0與DS18B20組成的測溫系統軟件流程圖如圖8所示。

圖8 測溫程序流程圖

軟件設計過程分為啟動溫度轉換、讀取溫度、顯示溫度三個過程。前面兩個過程都是從復位DS18B20開始。由于單總線協議對時序要求非常嚴格,分頻出1Mhz的頻率為了方便計數器計數。系統只用到一個溫度傳感器,SKIP ROM為跳過ROM命令,不需要讀取64位序列號來確定從機地址。

4.1DS18B20的驅動模塊

本設計使用的目標芯片是EP3C16F484C6[8],全部軟件功能在Quartus II13.0平臺上實現,使用了Verilog HDL語言編寫各個模塊的程序。DS18B20的驅動模塊電路圖符號如圖9所示, 該模塊有四個端口:clk是由開發板的50 MHz系統時鐘分頻得到的1MHz的時鐘信號;rst_n是低電平復位信號線;one_wire是與DS18B20的雙向接口;temperature[15…0]是16位的溫度數值輸出。DS18B20的驅動模塊利用狀態機將DS18B20的單總線協議描述出來,完成了初始化時序、讀時序、寫時序。

圖9 DS18B20的驅動模塊

以下是對采集的溫度數據進行處理的Verilog代碼,形成一定的線性關系。

Wire [15:0] t_buff = temperature_buff& 16'h07FF;

assign temperature[3:0] = (t_buff[3:0] * 10) ? 4;

// 小數點后一位

assign temperature[7:4] = (t_buff[7:4] >= 10) ? (t_buff[7:4] - 10) : t_buff[7:4]; // 個位

assign temperature[11:8] = (t_buff[7:4] >= 10) ? (t_buff[11:8] + 1) : t_buff[11:8]; //十位

assign temperature[15:12] = temperature_buff[12] ? 1 : 0; // 正負位

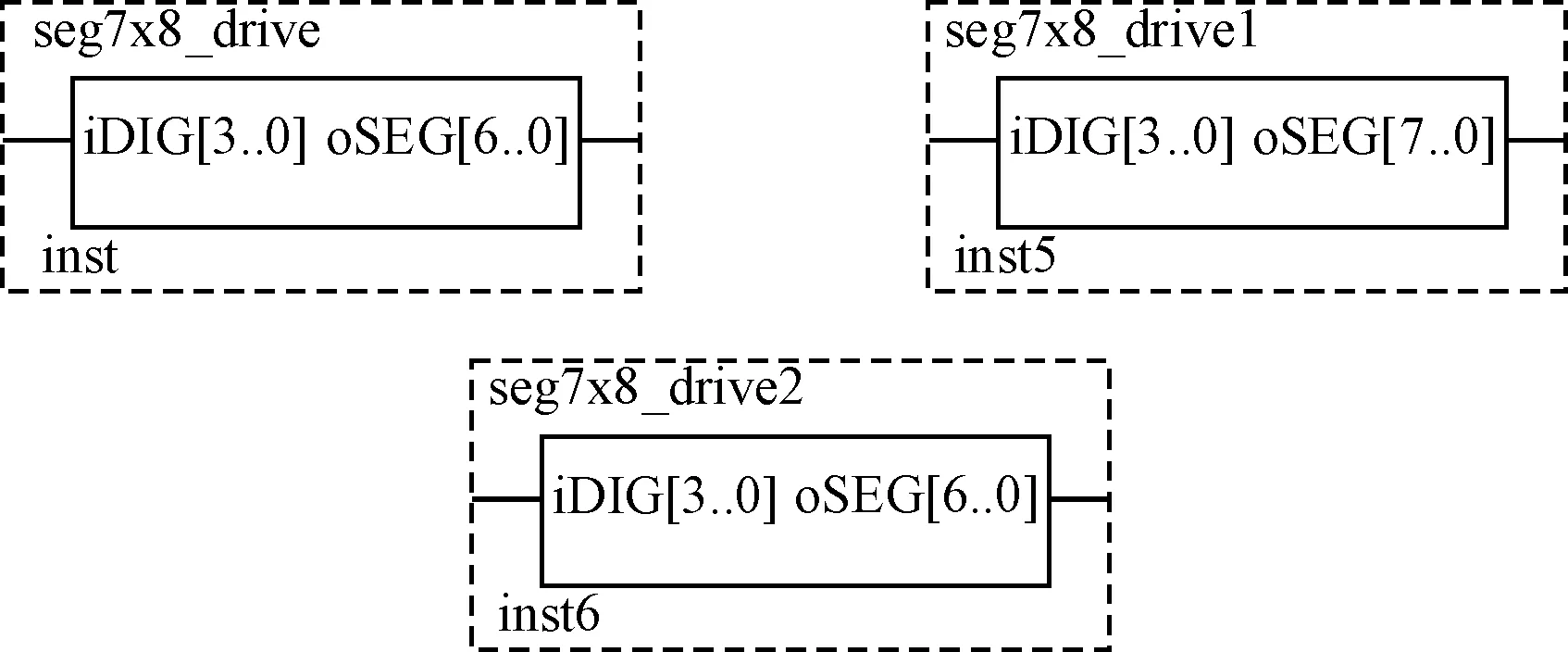

4.2數碼管顯示模塊

該系統采用四位數碼管來顯示采集的溫度值。DS18B20采集到溫度數據是二進制數據,一共有16位。高5位共同作為符號位,用S表示,當溫度為正時S為0,溫度為負值時S為1;低11位是數據位,與符號位組成12位的溫度數據。第一位數碼管表示溫度的正負狀態,如果溫度為正,則數碼管顯示熄滅狀態,如果溫度為負,則數碼管顯示’-’。第二位數碼管表示溫度的十位的值,第三位數碼管表示溫度的個位的值,該數碼管的dp位為小數點,為常亮狀態,第四位數碼管表示溫度的小數點位的值。根據系統設計的要求,分別設計了三個不同的數碼管譯碼模塊。第二位和第四位數碼管調用seg7x8_drive譯碼電路,第三位數碼管調用seg7x8_drive1譯碼電路,第一位數碼管調用seg7x8_drive2譯碼電路。三個數碼管顯示模塊如下圖10所示。

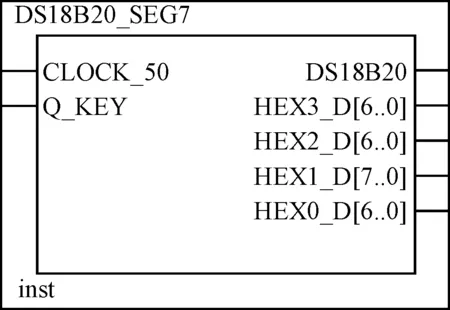

4.3溫度顯示頂層模塊

該模塊為系統設計的頂層模塊,在該模塊中定義了與外部硬件連接的輸入輸出引腳,依次調用DS18B20驅動模塊和數碼管顯示模塊,實現16位帶符號的溫度值在數碼管上顯示。該模塊的電路符號如圖10。

圖10 數碼管顯示模塊

該模塊中定義的輸入輸出引腳如下:

module DS18B20_SEG7(

inputCLOCK_50,// 板載50MHz時鐘

inputQ_KEY,

inoutDS18B20,

inputSW,

output[6:0]HEX3_D,

output[6:0]HEX2_D,

output[7:0]HEX1_D,

output[6:0]HEX0_D);

圖11 溫度顯示頂層模塊

5調試與結果分析

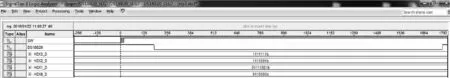

Signal Tap II[10]是Quartus II13.0軟件自帶嵌入式邏輯分析儀,該分析儀用于調試FPGA,并進行片內信號分析的一個重要工具,本設計在進行溫度數據采樣和捕獲信號時,通過JTAG端口進行數據傳輸,采用Signal Tap II邏輯分析儀進行數據處理,驗證該系統設計的邏輯功能是否正確。

邏輯分析儀的基本步驟如下:

1) 打開Signal Tap Ⅱ編輯窗;

2) 調入待測信號;

3) 相關參數設置。首先設置采樣時鐘;其次設置采樣深度;最后設置觸發條件;

4) 下載、啟動并查看數據。

經過上述步驟,程序下載到DE0后,用Signal Tap II抓取各個端口的數據并觀察其結果如圖12所示。

通過對各部分軟件的設計,用Quartus II 13.0軟件進行Verilog HDL語言的程序編譯,調試結果顯示沒有錯誤后,就可以將此程序燒寫進目標芯片里面,數碼管顯示如圖12所示結果,Signal Tap II的仿真結果顯示HEX3_D:1111111b,HEX2_D:1111001b,HEX1_D:01111001b,HEX0_D:0110000b,經數碼管譯碼后應該顯示:11.3℃,由于是正溫度,HEX0_D為熄滅狀態,與數碼管的顯示結果一樣。通過Signal Tap II的仿真和在數碼管顯示的結果可以驗證,該測溫系統實現了預期的目的。

圖12 Signal Tap II調試圖

6結語

本文用DE0開發板搭建硬件開發平臺,使用EP3C16F484C6 為主控芯片,DS18B20以單總線的方式與主控芯片連接,組成測溫系統。從DS18B20的操作步驟和時序出發,用Verilog HDL硬件描述語言編寫有限狀態機程序[11],實現對DS18B20的控制。該接口實現了DS18B20與DE0的通信,并可以將該接口做成IP核,嵌入到其它溫度控制系統中。實驗結果表明,該系統可以穩定的運行。該測溫系統還可以靈活地添加多個溫度傳感器,實現多路溫度測量系統,實時地感知不同環境下的溫度,實現多路傳感器數據的信息融合,該系統實時性高,可靠性高,有廣闊的應用前景。

參 考 文 獻

[1] 鄭麗娟,王梅,王寧.基于FPGA的多路溫度采集系統設計[J].通信電源技術,2015,32(2):47-49.

[2] 王春玲,王美紅.基于DS18B20的小環境測溫控制的FPGA實現[J].泰山學院學報,2014,36(3):10-16.

[3] 胡同花,周維龍.溫室大棚多點溫度采集系統的設計與實現[J].電子設計工程,2014,22(13):87-90.

[4] 于京,呂殿基.基于FPGA的測溫系統的設計[J].內蒙古大學學報,2011,42(5):576-580.

[5] 仁愛鋒,羅豐.基于FPGA的嵌入式系統的設計[M].西安:西安電子科技大學出版社,2014:30-58.

[6] 劉昌華.EDA技術與應用—基于QUARTUS II與VHDL[M].北京:北京航空航天大學出版社,2010:47-60.

[7] 夏宇聞.Verilog數字系統設計教程[M].北京:北京航空航天大學出版社,2008:166-175.

[8] Altera公司.DE0用戶手冊,2010.

[9] DALLAS公司.DS18B20數據手冊.

[10] 潘松,黃繼業.EDA技術實用教程[M].北京:科學出版社,2010:110-127.

[11] 王曉磊,李宏生.基于有限狀態機的數字溫度傳感器控制系統設計[J].艦船電子工程,2010:30(12):182-185.

收稿日期:2016年1月7日,修回日期:2016年2月19日

基金項目:國家科技計劃項目(863計劃)(編號:2013AA100302);武漢輕工大學2013研究生創新基金(編號:2013cx007)資助。

作者簡介:聶云,女,碩士研究生,研究方向:嵌入式FPGA設計。劉昌華,男,副教授,碩士生導師,研究方向:計算機網絡及應用、嵌入式FPGA設計。鄒翰,男,碩士研究生,研究方向:嵌入式技術。王慧,女,碩士研究生,研究方向:軟件開發。

中圖分類號TP391

DOI:10.3969/j.issn.1672-9730.2016.07.033

Design of Temperature Measurement System Based on DE0

NIE YunLIU ChanghuaZOU HanWANG Hui

(School of Mathematics and Computer Science, Wuhan Polytechnic University, Wuhan430023)

AbstractA DE0 development board and the temperature sensor DS18B20 is used to achieve the collection and display of temperature. It introduces the interface principle and operation sequence of the sensor and demonstrates the hardware circuit system composition and software design. By means of EP3C16F484C6 as the master chip, Verilog HDL hardware is used to describe language design state machine, which complete the FPGA’s operation about resetting, data-reading and data-writing on the DS18B20 temperature sensor according to the 1-wire protocol to finish temperature measurements. It also converts measured the binary temperature data into BCD code through digital tube display and use thes logic analyzer Signal Tap II of the Quartus II 13.0 software to simulate.

Key WordsDE0 development board, DS18B20 sensor, 1-wire protocol, Verilog HDL