新型通用電子產(chǎn)品測量控制設(shè)備設(shè)計

宋芑

新型通用電子產(chǎn)品測量控制設(shè)備設(shè)計

宋芑

(甘肅長風(fēng)電子科技有限責(zé)任公司 甘肅蘭州 730070)

電子產(chǎn)品在研制生產(chǎn)過程中不斷換代升級,要求其測量控制設(shè)備具備同步換代條件,本文論述用軟件實現(xiàn)上位機(jī)人機(jī)界面和FPGA控制程序,可以方便更改軟件提升測量控制設(shè)備的通用性,不斷持續(xù)改進(jìn)產(chǎn)品性能同時提升產(chǎn)品測量控制能力和產(chǎn)品測試效率,提高產(chǎn)品質(zhì)量能力。

電子對抗;測量控制;改進(jìn);觸控一體機(jī);通用性

引言

當(dāng)今社會電磁環(huán)境日益復(fù)雜,電子對抗已經(jīng)成為現(xiàn)代戰(zhàn)爭必不可少的組成部分。電子對抗技術(shù)的不斷發(fā)展,需要大量新型對抗電子產(chǎn)品的不斷研制生產(chǎn),其測量控制設(shè)備也要求具備不斷換代升級的條件。但是大量陳舊測試控制設(shè)備由模擬電路及硬件控制器件組成,不具備產(chǎn)品升級換代的條件。

1 項目背景

陳舊測試控制設(shè)備其電平輸出由單刀雙擲開關(guān)控制;時序脈沖產(chǎn)生由施密特觸發(fā)器或定時器電路組成,其脈沖寬度由電路外圍外接電阻和電容決定,其計算為τ=0.7RC;其他控制部分也由門電路或其他硬件模擬電路產(chǎn)生。這樣的測量設(shè)備產(chǎn)品功能單一,硬件更改困難,無通用性;其測量控制只能手動操作,會造成:

(1)測試設(shè)備通用性差,功能單一,升級困難,浪費(fèi)嚴(yán)重;

(2)測試設(shè)備只能手動操作測試,效率低下;

(3)測試數(shù)據(jù)為手工人為填寫,數(shù)據(jù)易更改,產(chǎn)品性能無法保證。

因此需要研制新型通用電子產(chǎn)品測量控制設(shè)備滿足不斷發(fā)展的電子產(chǎn)品需求。

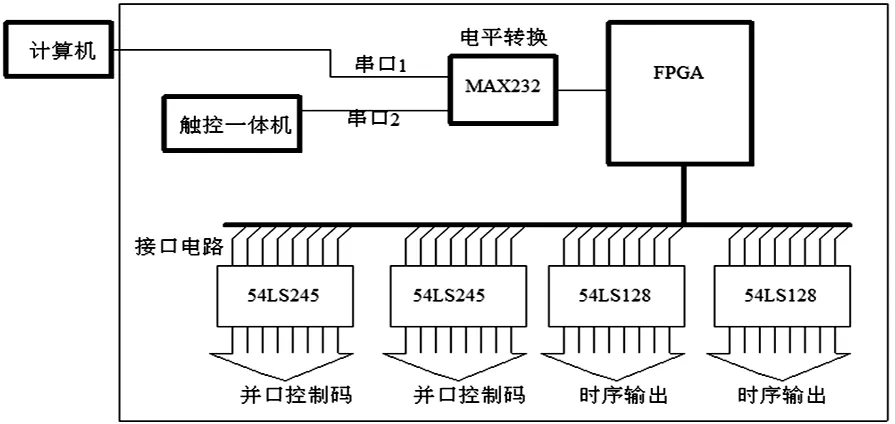

2 新型通用測試控制設(shè)備的設(shè)計

新型通用測試控制設(shè)備主要屏棄陳舊設(shè)備的局限性,采用上位機(jī)和FPGA處理芯片,利用上位機(jī)良好的人機(jī)界面發(fā)出串口信息,F(xiàn)PGA處理芯片接收串口命令,F(xiàn)PGA依據(jù)串口命令字輸出電子產(chǎn)品所需的并口控制碼和時序控制脈沖。系統(tǒng)實現(xiàn)框圖如圖1。

2.1 觸控一體機(jī)

圖1 新型通用測試設(shè)備

觸控一體機(jī)采用內(nèi)置ARM920T高速處理器內(nèi)核的LJD-eWin7S,其是一款基于WindowsCE操作系統(tǒng)下的控制平臺,基于EVC或是Visual Studio 2005來開發(fā),使用的語言可以用BASIC,C#或是VC++;其特點如下:

(1)接口豐富,帶 USB HOST、USB DEVICE、SD 卡等功能。

(2)采用低功耗32位高速ARM芯片方案,ARM920T核心,400MHz主頻。

(3)系統(tǒng)內(nèi)存為SDRAM 64MB、NAND FLASH 64M。

(4)高清晰真彩數(shù)字屏,可直接支持四線電阻式觸摸,精確方便。

(5)帶 2路標(biāo)準(zhǔn)RS232、1路RS485。

(6)支持揚(yáng)聲器、背景音樂、觸摸聲音控制、報警聲音控制、開關(guān)機(jī)聲音控制等功能。

2.2 串口收發(fā)接口電路

觸控一體機(jī)輸出串口電平為±12V,而FPGA接口電平為TTL,需要在觸控一體機(jī)輸出串口和FPGA接收接口之間增加串口收發(fā)接口電路MAX232A芯片,MAX232A芯片主要功能是電平轉(zhuǎn)換和驅(qū)動,其將上位機(jī)±12V串口電平轉(zhuǎn)換為TTL電平供FPGA使用,而且也可以將FPGA輸出的TTL串口轉(zhuǎn)換為±12V供上位機(jī)使用。

2.3 FPGA芯片

FPGA芯片選用ALTRA公司的CycloneII系列EP2C8,采用Verilog語言進(jìn)行編程,主要特點如下:

(1)為低成本優(yōu)化的架構(gòu);

(2)Cyclone II器件采用TSMC90nm低K絕緣工藝,具有很高的性能和極低的功耗;

(3)器件提供多達(dá)8256個邏輯單元(LE),可以用來實現(xiàn)復(fù)雜的應(yīng)用;

(4)嵌入式存儲器:基于M4K存儲器塊,提供多達(dá)16588bit的嵌入式存儲器;

(5)嵌入式乘法器:提供多達(dá)18個18×18bit乘法器;

(6)支持2個可編程鎖相環(huán);

(7)182個最大用戶I/O腳;

(8)FPGA芯片外圍接TTL電平驅(qū)動芯片74LS245或74LS244,時序控制脈沖通過54LS128,此芯片具有長線驅(qū)動功能,可提高脈沖信號的帶負(fù)載能力。

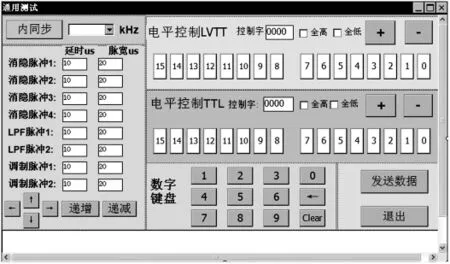

2.4 上位機(jī)測試界面設(shè)計

上位機(jī)觸控一體機(jī)采用Visual Studio 2010來開發(fā),此界面具有良好人機(jī)交互,脈沖參數(shù)可方便設(shè)置,電平控制分為TTL和LVTTL,可方便實現(xiàn),在不同系統(tǒng)能夠簡便更改程序,完成多型號電子產(chǎn)品測試。上位機(jī)測試界面如圖2。

圖2 上位機(jī)測試界面

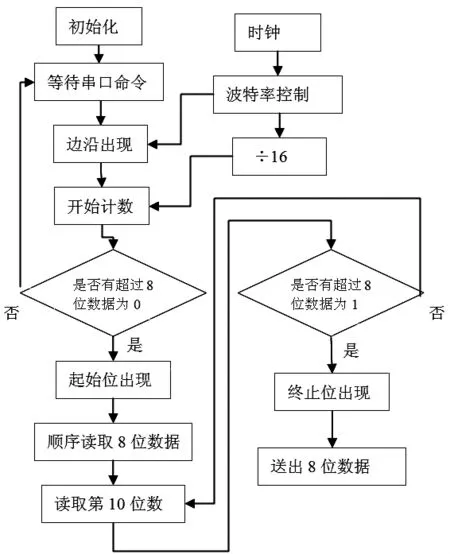

2.5 FPGA軟件設(shè)計

FPGA芯片采用Verilog語言進(jìn)行編程,其接收串口命令,依據(jù)上位機(jī)串口波特率,F(xiàn)PGA采用波特率的16倍采樣率對串口采樣,當(dāng)串口命令發(fā)送時,有觸發(fā)邊沿出現(xiàn),計數(shù)器采樣數(shù)有8位為低電平,則認(rèn)為是起始位出現(xiàn);延時8位開始采樣數(shù)有8位為低電平或高電平,則認(rèn)為數(shù)據(jù)0或1;按上述方法計數(shù)8位后,若采樣數(shù)有8位為高電平,則認(rèn)為是終止位結(jié)束,完成數(shù)據(jù)讀取。其設(shè)計流程圖如圖3。

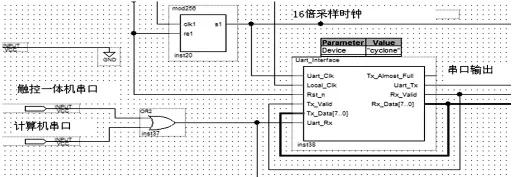

具體實現(xiàn)程序如圖4。

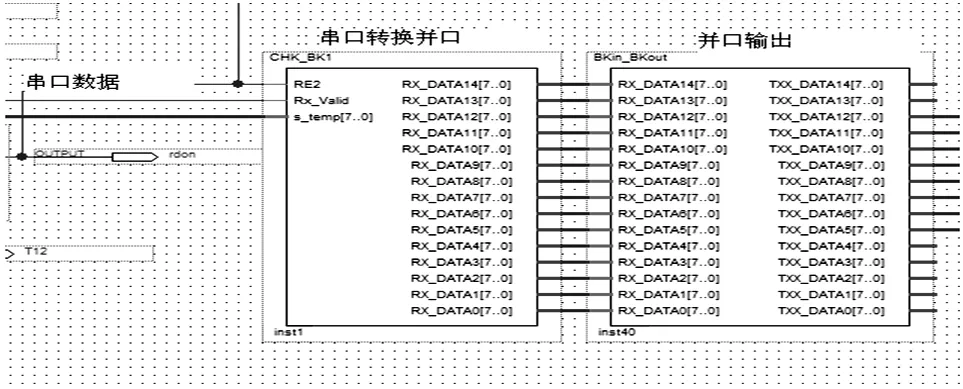

當(dāng)數(shù)據(jù)讀取后,每讀取一位數(shù)據(jù),則將數(shù)據(jù)順序賦值給每一位并口。具體實現(xiàn)如圖5。

通過以上論述和實踐,上位機(jī)和控制FPGA控制均有軟件程序?qū)崿F(xiàn),不同的電子產(chǎn)品測量均可更改程序軟件,即可實現(xiàn)多種型號電子產(chǎn)品測量;而且,上位機(jī)由計算機(jī)控制此測試控制設(shè)備,有方便實用性,提高產(chǎn)品質(zhì)量和可靠性。

3 結(jié)束語

綜上所述,通過對測試控制設(shè)備的升級改造,新型通用測試控制設(shè)備的通用性大大增加,電子產(chǎn)品測試能力不斷提升,并且還能實現(xiàn)計算機(jī)外控,若再實現(xiàn)對信號源、頻譜儀、示波器等儀器儀表控制,能完成對電子產(chǎn)品的自動測試,提高了生產(chǎn)效率,為公司生產(chǎn)帶來良好的效益!

[1]王彥.基于FPGA的工程設(shè)計與應(yīng)用.西安電子科技大學(xué)出版社.

圖3 FPGA軟件設(shè)計流程圖

圖4 數(shù)據(jù)讀取實現(xiàn)

圖5 串口轉(zhuǎn)換并口程序

[2]鄭阿奇,彭作民.Visual Basia.NET程序設(shè)計教程.機(jī)械工業(yè)出版社.

TN06

A

1004-7344(2016)27-0309-02

2016-9-11

宋 芑(1975-),女,甘肅蘭州人,工程師,本科,研究方向為電子工程。