閃電定位儀的通信接口設計

田新興,嚴 飛,劉銀萍

(南京信息工程大學 信息與控制學院,江蘇 南京 210022)

閃電定位儀的通信接口設計

田新興,嚴 飛,劉銀萍

(南京信息工程大學 信息與控制學院,江蘇 南京 210022)

文章主要開展閃電定位儀通信接口設計的工作。首先,研究以Altera FPGA為核心的控制器,主要用于數據采集系統及數據流的處理過程;其次,針對閃電定位儀通信接口設計要求,細化通信協議;最后,通過在FPGA上編程實現將采集到的閃電數據傳輸到上位機,配合LabView上位機波形分析軟件對單次閃擊信號進行特征分析。

閃電定位;通信接口;FPGA

閃電定位儀是一種監測雷電發生的氣象探測儀器。目前,國家閃電定位網采用的ADTD型閃電定位儀,其探測過程是在天線上感應出回擊的南北向和東西向磁場信號以及電場信號,并直接送到信號處理板,兩路磁場信號信道完全對稱。信號處理板對三路信號分別進行前置放大,低通濾波,積分放大,濾波,差分變換等技術處理,輸出干凈的磁場波形和電場波形[1]。

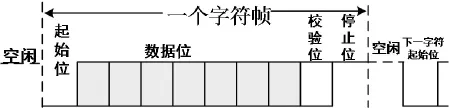

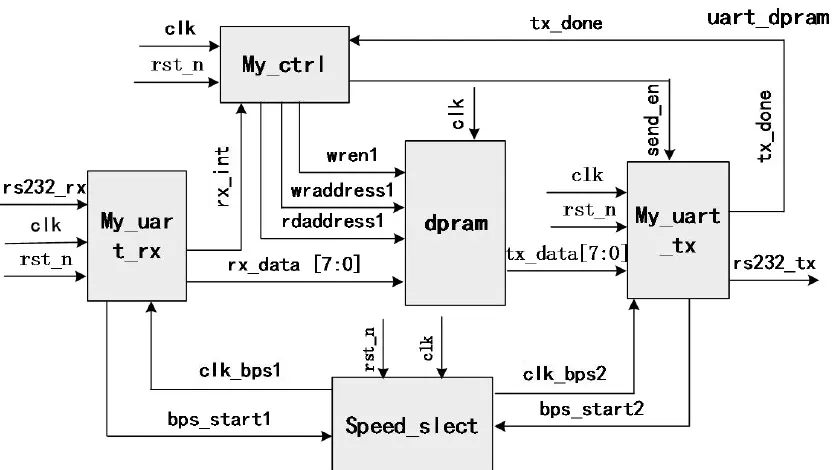

閃電定位儀采集到的波形信號最終要輸出到上位機,與上位機通信。本文以FPGA為控制核心,設計閃電定位儀與上位機的通信接口,可以充分利用FPGA資源將數據按照協議傳輸。異步通信,可實現全雙工收發。數據格式如圖2所示,一個數據幀包括起始位,數據位,奇偶校驗位和停止位。

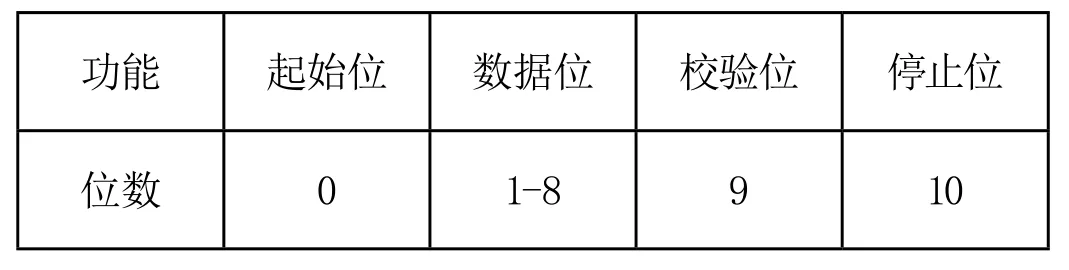

串口傳輸數據一般是一幀數據11位(見表1),也可以無校驗位。

表1 數據位功能

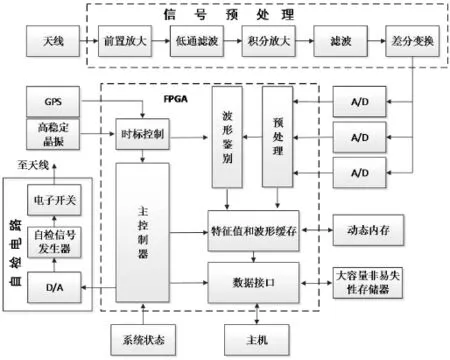

1 系統結構

閃電定位儀系統構架如圖1所示,基本結構組成有:信號預處理,FPGA,自檢電路,天線,GPS等。利用GPS全球定位系統的同步授時和可編程邏輯器件提供高精度的同步時間標記,多臺定位儀可以得到雷電脈沖到達個站之間的時間差,進而確定閃電的位置[2]。天線接收到閃電信號后經信號預處理電路去除噪音和毛刺等部分,經過A/D轉換為數字信號,然后在FPGA內處理并鑒別接收到的信號是否是閃電波形。如果滿足閃電波形的特征,則將采集到的數據緩存到內存中。本系統的關鍵部分是FPGA處理并鑒別數字信號,提取特征值,本文主要工作是將處理后的最終結果傳輸至上位機的通信接口。

2 數據接口

2.1UART的工作原理

圖1 閃電定位儀系統構架

UART是一種串行數據總線,用于

圖2 數據幀格式

在串口的總線上“高電平”為默認狀態,當一幀數據開始傳輸時必須先拉低電平,這就是第0位的作用。第0位過后就是有意義的8個數據位,最后的兩位是校驗位和停止位。

另外,串口傳輸的另一個重要參數就是“波特率”。在微觀上“波特率”就是串口傳輸中“一個位的周期”。

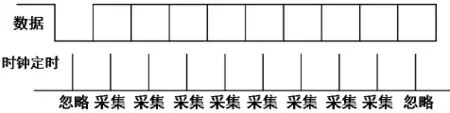

閃電信號經A/D轉換后,my_uart_rx以設定好的波特率采集信號,如圖3所示。根據奈奎斯特采樣定理,在A/D信號轉換過程中,采樣頻率fs.max大于信號中最高頻率fmax的2倍時,采樣后的數字信號會完整地保留原始信號中的信息。一般實際應用中保證采樣頻率為信號最高頻率的5~10倍,常用的波特率有9600 bps和115200 bps[3]。

圖3 數據采集時序

因為現實環境中存在各種電磁干擾,導致數據的起始部分不穩定,所以,一般在數據中間部分采樣。如圖4所示,在輸入一幀數據時,當my_uart_rx檢測到rs232_rx由高電平跳變到低電平,向speed_select發送bps_start信號,然后speed_select模塊在每一個時鐘上升沿計數。假設時鐘為50MHz,波特率為9600bps,每位為1/9600秒,需要計5208個周期(計數5208),要在中間采樣所以計數滿2604并且bps_start為1,方可產生clk_ bps信號。

對于第0位數據,采取忽略態度,只需采集接下來的8位數據,最后校驗位(可以無校驗位)和停止位,也采取了忽略的操作。串口傳輸數據的起始是“從最低位開始,到最高位結束”[4]。整體系統的硬件邏輯框結構如圖4所示。

圖4 硬件邏輯框

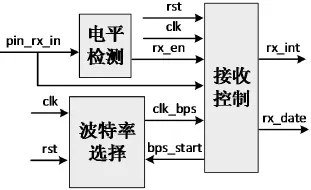

2.2接收模塊設計

當電平檢測檢測到接收引腳(pin_rx_in)電平由高變低時,接收控制部分向波特率選擇模塊發送開始計時信號(bps_start),波特率模塊在時鐘周期的上升沿計數,當計數滿時向接收模塊發送脈沖(clk_bps)。接收到clk_bps后,將pin_rx_in的數據緩存到寄存器reg[0]-reg[7],然后通過rx_date[7∶0]發送到RAM中。圖5為接收部分的示意圖。

圖5 接收模塊

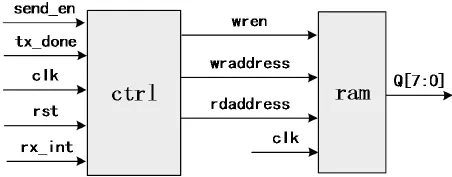

2.3RAM模塊設計

接收模塊接收完整數據后向RAM控制模塊發送rx_int信號,使控制模塊控制RAM的wren(寫使能)信號置位,并輸出寫地址信號,rx_date[7∶0]存儲到wraddress的地址。之后,每收到rx_int信號時要使wraddress=wraddress+1,在新的地址寫入接收到的新數據,如圖6所示。

圖6 控制模塊和RAM模塊

2.4控制模塊

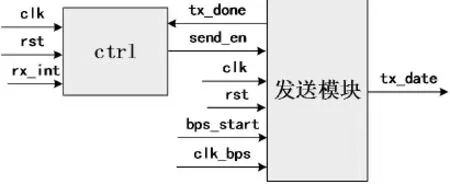

將接收模塊發送的rx_int信號作為RAM寫入使能信號,并控制wraddress寫地址自增,將發送模塊的tx_done信號和send_en信號分別作為讀地址變換信號和發送模塊發送數據的使能信號。當發送模塊發送出去一幀數據后,讀地址rdaddress自增,然后send_en置1,發送使能。

2.5發送模塊設計

RAM接收數據后,控制模塊向發送模塊發送一個發送使能(send_en)信號,讀取讀地址rdaddress內的數據到寄存器Q[7∶0],傳送給發送模塊,發送模塊在波特率模塊的控制下發送數據到PC,發送完一幀數據后向控制模塊發送一個發送完成信號,tx_done和send_en信號均為高電平時,方可發送下一幀數據,如圖7所示。

圖7 數據發送模塊

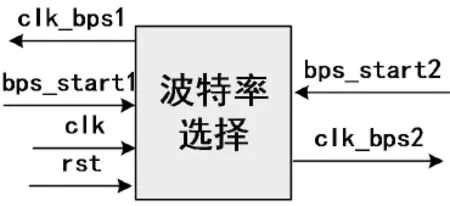

2.6波特率選擇模塊

當芯片晶振為50MHz時,波特率為9600bps,發送一位的時間是1/9600s。即計數1/9600×50M=5208,根據數據采集的原則,當計數不滿2604或超出2604但不到5208時繼續計數,達到2604且bps_start=1時輸出信號,計數滿5208時清零,如圖8所示。

圖8 波特率選擇模塊

3 系統驗證

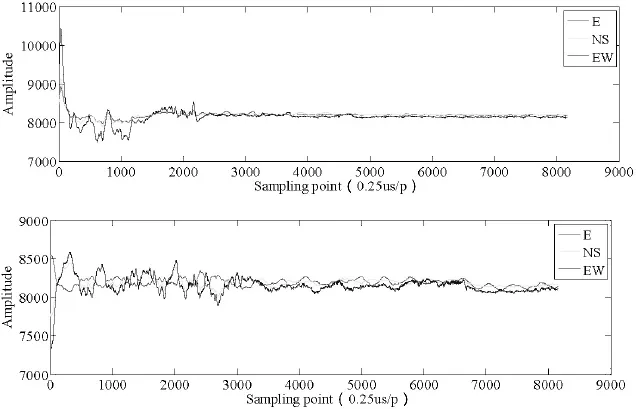

真實的大氣放電現象的復雜多變的,主要包括對地放電,云層內部放電,云對云放電[4]。圖9為捕獲到的閃電波形

圖9 接收到的閃電波形

圖,包括閃電觸發后的南北向磁場信號,東西向磁場信號和電場信號。從波形可以明顯看出閃電波形的不規律性,可以由接收到的信號的場強和脈沖電磁波傳播規律推算出雷擊電流大小,以便用于后續研究。

4 結語

閃電定位儀對天線接收到的信號進行前置放大,低通濾波,積分放大等處理,經過模數變換后,FPGA對其進行鑒別、分析,提取出相應的特征點。本文開展的閃電定位儀通信接口設計的工作,可以有效地將之前處理后的波形特征信息傳輸至上位機,實現基于FPGA的雷電數據采集、數據處理和數據上傳的功能。本設計還可以借助GPRS的數傳模塊,實現遠程通信,將多站點雷電數據傳輸至服務器,以實現基于時差算法的閃電定位。

如今,4G數傳模塊的發展趨于成熟,下一步的工作將秉承現有的傳輸協議,使系統不僅能傳輸處理后的特征點信息,還將實現數據的低延時全波形傳輸,其對有效分析閃電的發展過程有重要意義。

[1]黃志興.ADTD型閃電定位儀的日常使用和維護[J].氣象水文海洋儀器,2015(2):112-113.

[2]肖坤峰,孫秀斌,楊崧令,等.基于FPGA的雷電定位系統高精度時標設計[J].電子技術應用,2013(11):50-52.

[3]聶濤,許世宏.基于FPGA的UART設計[J].現代電子技術,2006(2):127-129.

[4]田樂,張勇.基于FPGA實現異步串行通信[J].現代電子技術,2013(13):71-73.

[5]譚涌波.《雷電學原理》課程建設與發展[J].教育教學論壇,2015(33):202-203.

[6]RAKOV V A,MALLICK S,NAG A,et al.Lightning Observatory in Gainesville(LOG),Florida:A review of recent results[J]. Electric Power Systems Research,2014(113):95-103.

[7]MURTHA J B, SKINNER II W H.Lightning detection apparatus and methodology[M].US:US5977762 1999.

[8]RAKOV V A,UMAN M A,RAIZER Y P.Lightning:Physics and Effects[J].Physics Today,2006(57):63-64.

Lightning of Communication Interface Design

Tian Xinxing, Yan Fei, Liu Yinping (Nanjing University of Information Science & Technology Information and Control College, Nanjing 210022, China)

This paper carried out the lightning locator communication interface design work.Firstly,in order to Altera FPGA as the core controller,primarily for data acquisition and processing system data flow; Secondly,lightning locator communication interface design requirements,refine the communication protocol; and finally,by the FPGA programming will be collected the lightning data to a PC,the PC with LabView waveform analysis software for a single strike signal characteristic analysis.

Lightning location; communication interface; FPGA

項目名稱:江蘇省高校自然科學研究面上項目;項目編號:15KJB170010。項目名稱:江蘇省自然科學;項目編號:BK20150903。項目名稱:南京信息工程大學人才啟動基金項目;項目編號:S8113106001。

田新興(1994-),男,河南新鄉,本科。