脈沖電容試驗(yàn)裝置控制系統(tǒng)電磁兼容設(shè)計(jì)

李小亮,董雪峰

(黃河科技學(xué)院 信息工程學(xué)院,河南 鄭州 450063)

脈沖電容試驗(yàn)裝置控制系統(tǒng)電磁兼容設(shè)計(jì)

李小亮,董雪峰

(黃河科技學(xué)院 信息工程學(xué)院,河南 鄭州 450063)

在脈沖電容試驗(yàn)裝置研制工程中,電磁兼容是必須考慮的因素。設(shè)計(jì)中通過采用電磁濾波、信號(hào)隔離、去噪、閥值調(diào)節(jié)電路等措施,并根據(jù)FPGA特性,從芯片的內(nèi)部和外部設(shè)計(jì)兩方面提高了整個(gè)控制系統(tǒng)的抗干擾能力,實(shí)現(xiàn)了電磁兼容設(shè)計(jì),確保了試驗(yàn)平臺(tái)的安全、可靠和穩(wěn)定工作。

脈沖電容FPGA;電磁兼容;抗干擾

電磁兼容性是指一般電氣、電子設(shè)備在共同的電磁環(huán)境中能執(zhí)行各自功能的并存狀態(tài),既要求都能正常工作又要求互不干擾,達(dá)到“兼容”的狀態(tài),任何電子電子設(shè)備或電子系統(tǒng)的設(shè)計(jì)都應(yīng)包括電磁兼容設(shè)計(jì)。

脈沖電容試驗(yàn)裝置主要完成質(zhì)量試驗(yàn)和耐壓試驗(yàn)[1]。控制系統(tǒng)工作環(huán)境惡劣、電路復(fù)雜,主要包括電源電路、信號(hào)處理電路、控制電路、接口電路、顯示電路等模數(shù)混合電路等。為提高控制系統(tǒng)的可靠性,必須采取必要的措施來抑制電磁干擾及優(yōu)化電路硬件和軟件設(shè)計(jì),保證系統(tǒng)穩(wěn)定工作。

1 電磁干擾成因

電磁干擾的形成必須同時(shí)具備3個(gè)要素:即電磁干擾源、傳輸路徑及敏感設(shè)備。干擾源是指產(chǎn)生的干擾的元件、設(shè)備或信號(hào);傳播路徑指干擾從干擾源傳播到敏感器件的通路或媒介;敏感設(shè)備是指容易被干擾的對(duì)象,如微處理器、A/D轉(zhuǎn)換器、D/A轉(zhuǎn)換器、比較器等。

1.1 電網(wǎng)干擾及系統(tǒng)放電干擾

脈沖電容試驗(yàn)控制系統(tǒng)中采用市電供電,電網(wǎng)質(zhì)量直接影響系統(tǒng)工作的穩(wěn)定性。試驗(yàn)中設(shè)備的啟停造成交流電源電壓的短1時(shí)跌落,以及繼電器和試驗(yàn)控制系統(tǒng)中開關(guān)柜的動(dòng)作引起的快速脈沖群等都會(huì)影響到電源電壓的穩(wěn)定性,從而對(duì)控制系統(tǒng)造成干擾;另外,試驗(yàn)系統(tǒng)主要包括質(zhì)量試驗(yàn)和耐壓實(shí)驗(yàn),質(zhì)量實(shí)驗(yàn)要求對(duì) 0.33 μF脈沖電容恒流充電至8 000 V,放電電流達(dá)到8 000 A,測(cè)試頻率為6~8次/1 min,進(jìn)行連續(xù)測(cè)量;耐壓實(shí)驗(yàn)要求脈沖電容充電至12 000 V,保持1 min后,進(jìn)行短路放電,放電電流接近12 000 A[1]。因此,試驗(yàn)過程中接近短路放電會(huì)產(chǎn)生上千伏的浪涌電壓及伴隨火花干擾。

1.2 傳輸路徑

電磁干擾傳輸路徑有兩種方式:一種是傳導(dǎo)傳輸方式;另一種是輻射傳輸方式。對(duì)于脈沖電容試驗(yàn)系統(tǒng),主要包括短路放電構(gòu)成的磁場(chǎng)耦合干擾及經(jīng)過傳導(dǎo)線對(duì)控制電路形成的干擾。

1.3 敏感設(shè)備

試驗(yàn)控制系統(tǒng)主要以FPGA為核心,實(shí)現(xiàn)對(duì)高壓電源、AD采樣控制器、開關(guān)柜、峰值檢波電路、羅氏線圈及各接口、顯示電路的控制。芯片采用CYCLONEⅡ系列的EP2C5T144,其電源模塊采用5 V供電,I/O端口供電電壓為3.3 V,而內(nèi)核供電僅為1.2 V,因此電源電壓的起伏、噪聲的引入都可能會(huì)使得FPGA配置信息出錯(cuò)而導(dǎo)致系統(tǒng)失效,產(chǎn)生嚴(yán)重后果[2]。另外,控制系統(tǒng)中A/D轉(zhuǎn)換器引入的共模干擾信號(hào)、電容短路放電時(shí)峰值采樣引入的噪聲信號(hào)同樣會(huì)引起FPGA產(chǎn)生誤判,影響系統(tǒng)的穩(wěn)定性。

2 采用的抗干擾措施

我們一般采取的抗干擾基本原則是:抑制干擾源、切斷干擾傳播路徑,提高敏感器件的抗干擾性能。

2.1 電源濾波

試驗(yàn)裝置的頻繁啟停、短路放電產(chǎn)的上千伏浪涌電壓會(huì)嚴(yán)重影響電網(wǎng)質(zhì)量,從而影響控制系統(tǒng)的可靠性,因此需在電網(wǎng)輸入端采用變壓比為1:1的隔離變壓器,降低電源雜訊干擾及提高電源信噪比。

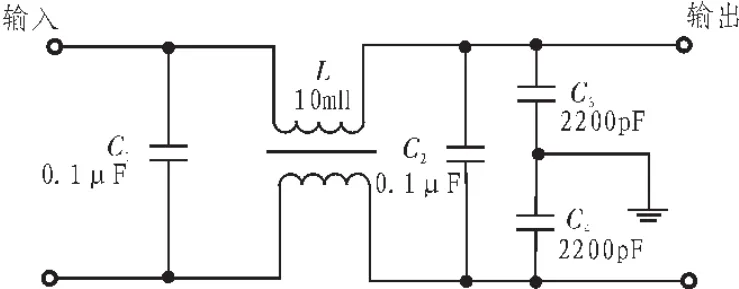

1)電磁干擾屬于射頻干擾,其傳導(dǎo)噪聲頻譜大致為10 k~30 MHz,從形成特點(diǎn)分析分為串摸干擾和共模干擾。電源設(shè)計(jì)中,220 V交流電首先經(jīng)過圖1電磁干擾濾波電路后再經(jīng)DC/DC轉(zhuǎn)換為控制電路提供穩(wěn)定的直流電源。

圖1 電磁干擾濾波電路Fig.1 Circuit of EMI filter

L為共模扼流圈,將兩個(gè)線圈分別繞在低損耗、高導(dǎo)磁率的鐵氧體磁環(huán)上,當(dāng)出現(xiàn)共模干擾時(shí),由于兩個(gè)線圈磁通方向相同,經(jīng)過耦合總電感量迅速增大,因此對(duì)共模信號(hào)呈現(xiàn)很大的感抗,圖1中L的電感量與EMI濾波電路的額定電流關(guān)系如表1所示。C1、C2為差模抑制抑制電容,主要用來濾除串膜干擾;C3、C4為共模抑制電容,跨接在輸出端,中間接地,可有效抑制共模干擾信號(hào)[3]。

表1 電磁濾波電路電感量與電流關(guān)系表Tab.1 Diagram of relationship of inductance and current to EMI circuit

2)在控制電路電源端并聯(lián)一個(gè)10 μF/50 V鉭電容和一個(gè)0.1 μF的高頻、地分布電感陶瓷電容進(jìn)行電源退耦,同時(shí)在每個(gè)芯片電源端口和信號(hào)輸入端口并聯(lián)一個(gè)瞬態(tài)抑制二極管,可吸收高達(dá)數(shù)千瓦的浪涌功率,使兩級(jí)間電壓嵌位于設(shè)定值,有效保護(hù)控制電路免受浪涌電壓和電磁干擾。

2.2 羅氏線圈的抗干擾設(shè)計(jì)

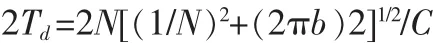

質(zhì)量試驗(yàn)中,為滿足參數(shù)設(shè)計(jì)要求,需使用具有響應(yīng)速度快、頻帶寬、靈敏度高、測(cè)量范圍大、抗電磁干擾能力強(qiáng)等特點(diǎn)的電流傳感器進(jìn)行電流采樣。為此,我們特意設(shè)計(jì)了小型大電流羅氏線圈[4]。線圈制作過程中,很難保證積分阻和線圈的波阻抗匹配,所以在線圈中傳播的電磁波通過積分電阻必然產(chǎn)生反射,反射時(shí)間為電磁波的渡越時(shí)間Td的兩倍。反射會(huì)造成輸出信號(hào)的振蕩,周期為:

其中C為光速,N為線圈匝數(shù),b為骨架外經(jīng),l為線圈等效周長(zhǎng)。應(yīng)要求2Td小于被測(cè)信號(hào)上升時(shí)間。另外,感應(yīng)線圈工作時(shí)相當(dāng)于信號(hào)源,產(chǎn)生的電壓信號(hào)經(jīng)電纜輸入示波器,它的負(fù)載就是積分電阻與同軸電纜,在阻抗不匹配情況下會(huì)造成波的反射,而產(chǎn)生一個(gè)欠阻尼振蕩。因此,設(shè)計(jì)時(shí),使α= 0.5R<<Zr。

2.3 峰值檢波消噪電路設(shè)計(jì)

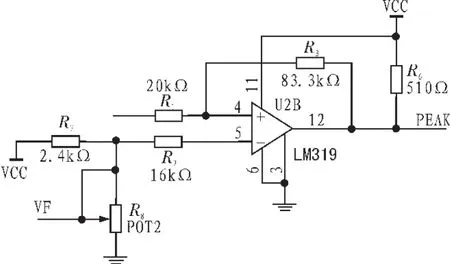

峰值檢波電路中,羅氏線圈將放電電流轉(zhuǎn)換成電壓信號(hào)和8 000 A對(duì)應(yīng)的閥值電壓比較,判斷放電電流達(dá)到8 000 A。而感應(yīng)到的模擬信號(hào)中夾雜的噪聲和干擾易使比較器在閥值附近出現(xiàn)重復(fù)翻轉(zhuǎn),造成系統(tǒng)不穩(wěn)定,因此,電路中采用遲滯比較器設(shè)計(jì)大大提高了電路的抗干擾能力。圖2中,峰值檢波電路LF398的輸出經(jīng)電阻R1加到具有低輸入失調(diào)電壓和偏置電流、高電壓增益、共模抑制好并具有輸入保護(hù)二極管的高速比較器LM319同相輸入端,和反饋電壓一起構(gòu)成比較器的外部滯回電壓,在VF端可根據(jù)需要調(diào)節(jié)閥值電壓值。

圖2 閥值電壓調(diào)節(jié)電路Fig.2 Circuit of threshold voltage regulation

2.4 FPGA內(nèi)部設(shè)計(jì)中的抗干擾措施

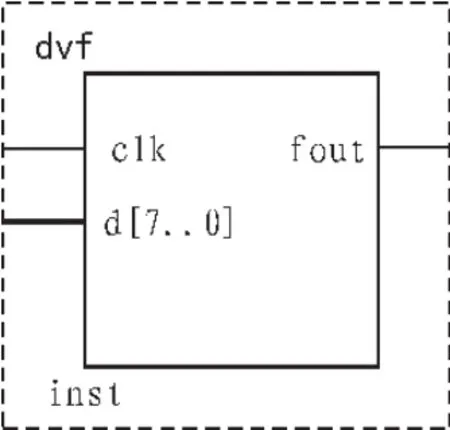

1)在FPGA的控制系統(tǒng)設(shè)計(jì)中,電容的短路放電、手動(dòng)控制按鈕的啟動(dòng)、停止,在瞬間都會(huì)產(chǎn)生電壓的突跳,使得輸入信號(hào)中存在噪聲,從而導(dǎo)致系統(tǒng)的誤動(dòng)作。為避免尖峰干擾信號(hào)及機(jī)械開關(guān)電壓抖動(dòng),采用計(jì)數(shù)器作為數(shù)字濾波電路。方法是將輸入信號(hào)加到計(jì)數(shù)器輸入端,當(dāng)開關(guān)啟動(dòng)或者輸入信號(hào)為高電平時(shí),對(duì)采樣脈沖開始計(jì)數(shù),只有在采樣時(shí)間內(nèi)連續(xù)計(jì)數(shù)到達(dá)足夠次數(shù)時(shí)認(rèn)為信號(hào)有效,否則視為無效。針對(duì)不同的輸入信號(hào)和尖峰干擾,可以設(shè)置不同的采樣時(shí)間,如圖3所示,通過設(shè)置合適的預(yù)置數(shù)D,即可濾除機(jī)械開關(guān)中的電壓波動(dòng)和消除不穩(wěn)定的干擾信號(hào)。

圖3 可預(yù)置數(shù)數(shù)字濾波電路Fig.3 Digital filter circuit of preset data

2)由于信號(hào)在FPGA內(nèi)部經(jīng)過不同的連線和邏輯單元時(shí)產(chǎn)生的延時(shí)不同,同時(shí)信號(hào)的高低電平轉(zhuǎn)換也需要一定的過渡時(shí)間,因此當(dāng)芯片內(nèi)部多路信號(hào)同時(shí)變化時(shí)會(huì)出現(xiàn)毛刺信號(hào)[5]。而這些毛刺信號(hào)可能直接作用到控制電路的時(shí)鐘輸入端、清零端、置位端及質(zhì)量試驗(yàn)計(jì)數(shù)端口,導(dǎo)致系統(tǒng)出錯(cuò),為避免毛刺信號(hào)產(chǎn)生及減小其對(duì)控制電路的影響,可利用D觸發(fā)器鎖存法、冗余項(xiàng)消除法、采樣法、吸收法[6]、VHDL語(yǔ)言描述法、單進(jìn)程Moore狀態(tài)機(jī)等方法消除毛刺信號(hào)。

圖4 改進(jìn)前電流放電波形Fig.4 Waveform of discharge current before improving circuit

圖5 改進(jìn)后電流放電波形Fig.5 Waveform of discharge current after improving circuit

3 結(jié) 論

電磁兼容設(shè)計(jì)是保證是保證試驗(yàn)系統(tǒng)安全、穩(wěn)定工作的重要因素。參照實(shí)際的電磁環(huán)境,采用了隔離、濾波、退耦、建立遲滯回路和FPGA內(nèi)部濾波電路等多種方式,并經(jīng)過多次測(cè)試和改進(jìn),實(shí)現(xiàn)了試驗(yàn)系統(tǒng)的長(zhǎng)期穩(wěn)定可靠工作,圖4和圖5分別為改進(jìn)前后脈沖電容放電波形,比照其結(jié)果,從圖中可明顯看到改進(jìn)后放電電流更大(放電電流變比為1000A: 1V),且波形更為平滑。

[1]李小亮,董雪峰.脈沖電容器質(zhì)量試驗(yàn)及其電路中元件參數(shù)的確定[J].電子設(shè)計(jì)工程,2011(3):172-175.

[2]張惠國(guó),王曉玲,唐玉蘭,等.一種用于FPGA配置的抗干擾維持電路[J].電子學(xué)報(bào),2011(5):1169-1173.

[3]李鵬,何文忠.開關(guān)電源電磁干擾濾波器設(shè)計(jì)[J].激光與紅外,2007(1):79-81.

[4]衛(wèi)兵,卿燕玲,關(guān)永超,等.測(cè)量低頻大電流的自積分羅氏線圈設(shè)計(jì)[J].強(qiáng)激光與粒子束,2010(9):2227-2231.

[5]李濤,高楊英,韓力.FPGA在惡劣電磁環(huán)境下的抗干擾設(shè)計(jì)[J].電子工程師,2004(6):38-40.

[6]馬利,馬技,牛斌.基于FPGA的光電編碼器電路抗干擾設(shè)計(jì)[J].遼寧大學(xué)學(xué)報(bào):自然科學(xué)版,2010(3):244-247.

EMC design of control system of test device of impulse capacitor

LI Xiao-liang,DONG Xue-feng

(Huanghe Science&Techonology College,Zhengzhou 450063,China)

EMC is a necessary factor to be considered in the design&development phase of the test device of impulse capacitor.By using the electromagnetic design of filter,signal isolation,denoising,a threshold adjustment circuit,and according to the characteristics of FPGA,from the internal and external of FPGA chip to improve the anti-interference ability of the whole control system,we realizes the electromagnetic compatibility design,and ensure that the platform is stable and reliable work.

impulse capacitor;FPGA;EMC;anti-interference

TN97

A

1674-6236(2016)04-0134-03

2015-04-16 稿件編號(hào):201504168

鄭州市光電信息技術(shù)及應(yīng)用重點(diǎn)實(shí)驗(yàn)室項(xiàng)目(114PYFZX505)。

李小亮(1983—),男,河南濟(jì)源人,碩士,講師。研究方向:電子通信系統(tǒng)。