基于FPGA的軟X射線CCD驅動電路設計

郝玉婷,韋 飛,冷 雙,李咪咪

(1.中國科學院空間科學與應用研究中心 北京 100190;2.中國科學院大學 北京 100190)

基于FPGA的軟X射線CCD驅動電路設計

郝玉婷1,2,韋 飛1,冷 雙1,李咪咪1,2

(1.中國科學院空間科學與應用研究中心 北京 100190;2.中國科學院大學 北京 100190)

CCD是實現空間軟X射線探測任務的核心部件,E2V公司的科學級CCD42-10 BI AIMO對空間軟X射線探測具有較高的靈敏度、低噪聲水平和高讀出速度,本文針對該款CCD提出了一種基于FPGA的驅動電路設計方案。選用Xilinx公司的XC3S500E作為驅動電路的核心器件,通過VHDL語言對驅動時序進行了硬件描述,采用EL7202作為CCD驅動芯片。仿真與實驗測試結果表明,該設計可以滿足科學級CCD42-10 BI AIMO的驅動電路要求。

軟X射線;CCD;驅動電路;FPGA

空間軟X射線觀測是獲得高溫等離子體溫度、密度、運動速度等重要參數的有效途徑,對研究太陽耀斑爆發及演化過程的加熱機制及其動力學行為具有極其重要的研究價值[1]。科學級CCD由于其體積小、重量輕、噪聲低、分辨率高等優點,近年來在越來越多的空間X射線觀測任務中得到應用。

科學級CCD對驅動電路有著嚴格的要求,它的性能是影響CCD的轉換效率、信噪比特性和系統時間分辨率水平的重要因素。因此,驅動電路的設計是科學級CCD在空間X射線觀測應用中的關鍵問題之一。傳統的CCD驅動時序設計方法主要有單片機驅動法、EPROM驅動法和DSP驅動法等,這些設計方法缺乏靈活性、可移植性差。FPGA邏輯控制電路具有硬件可編程、處理速度快、可靠性高等特點,非常適于CCD驅動時序的設計。文中首先簡單介紹了科學級探測器CCD42-10 BI AIMO的性能和結構,然后在分析了其工作驅動時序的基礎上,提出了一種基于FPGA的科學級全幀CCD驅動電路的設計方案。CCD。此款CCD采用背照式結構,適用于空間X射線觀測,顯著提高了其量子效率[2]。高級反轉模式(AIMO)能夠極大

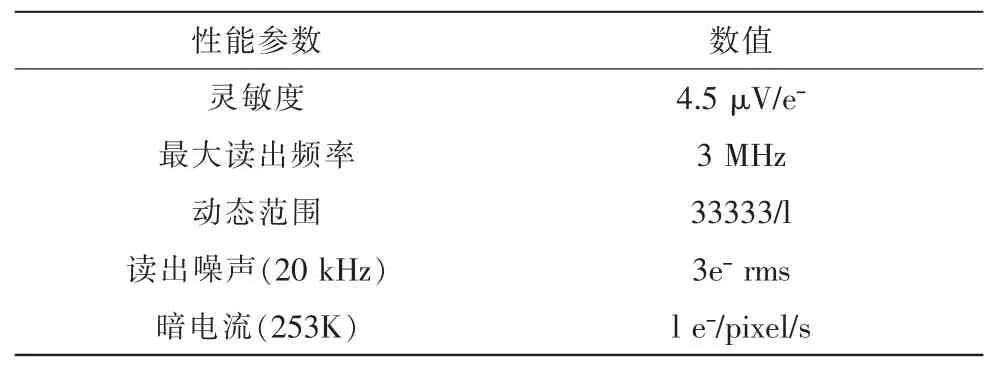

地減少暗電流的產生率,從來源上減小暗電流噪聲,使對CCD的制冷要求降低到一定水平,用半導體制冷的方法就能夠達到制冷要求[3]。其主要的性能參數如表1所示。

表1 CCD42-10 BI AIMO性能參數值Tab.1 Performance parameter of CCD42-10 BI AIMO

1 CCD42-10 BI AIMO芯片

CCD42-10 BI AIMO是英國 E2V公司生產的全幀面陣

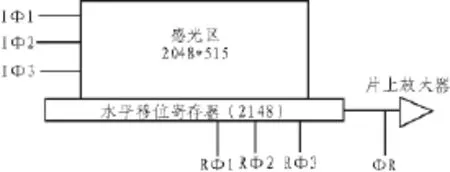

CCD42-10 BI AIMO由感光區、水平寄存器和片上輸出放大器組成,其結構如圖1所示。感光區有效像元數為2 048*515,由行轉移時鐘IΦ1、IΦ2、IΦ3驅動控制。水平移位寄存器被金屬鋁遮蔽不會曝光,由像素讀出時鐘RΦ1、RΦ2、RΦ3驅動,與感光區對應兩邊分別多出50個空像元,用作暗電平參考,以減小暗電流噪聲[4]。片上放大器上需施加復位時鐘ΦR,實現對每個像素讀出前的參考電平復位。

圖1 CCD42-10 BI AIMO結構圖Fig.1 Structure diagram of CCD42-10 BI AIMO

2 驅動時序分析

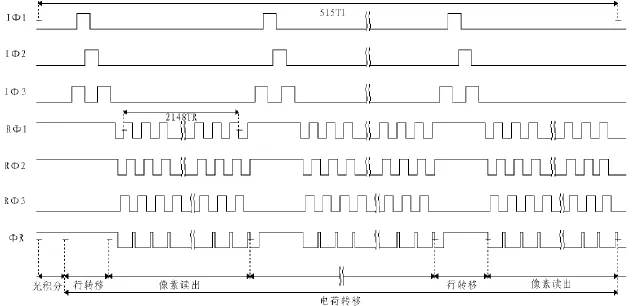

圖2為CCD42-10 BI AIMO的工作時序圖,從圖中可以明顯看出,CCD42-10 BI AIMO的一個工作周期分兩個階段:光積分階段、電荷轉移階段。

光積分階段,感光區的光敏陣列接受外界光源照射產生光電荷。因CCD42-10 BI AIMO采用先進的高級反轉模式技術,在光積分期間,時鐘脈沖IΦ1、IΦ2和IΦ3保持低電平即可控制感光區收集電荷。

光積分結束后進入電荷轉移階段,行轉移和像素讀出交替進行,直至感光區的像素電荷被完全讀出。行轉移是在行轉移時鐘IΦ1、IΦ2、IΦ3的驅動下,將感光區中的感光電荷整行向下轉移一行,位于感光區的最下面一行像素電荷則轉移到水平寄存器中。垂直行轉移過程共需要515個行轉移周期(TI)。在進行行轉移時,像素讀出時鐘RΦ1、RΦ2保持固定的高電平,以形成勢阱收集感光區轉移來的像素電荷;RΦ3則保持固定的低電平,起到像素隔離的作用。

圖2 CCD42-10 BI AIMO驅動時序圖Fig.2 Driving timing diagram of CCD42-10 BI AIMO

每進行完一次行轉移,則進入像素讀出階段。在像素讀出時鐘RΦ1、RΦ2、RΦ3的控制下,將水平移位寄存器中的像素電荷依次轉移,然后在復位時鐘脈沖ΦR的控制下,對每個像素進行參考電平復位,最后通過片上輸出放大器輸出。每一行像素的讀出共需要2 148個像素讀出周期(TR)。

3 CCD42-10 BI AIMO驅動電路設計

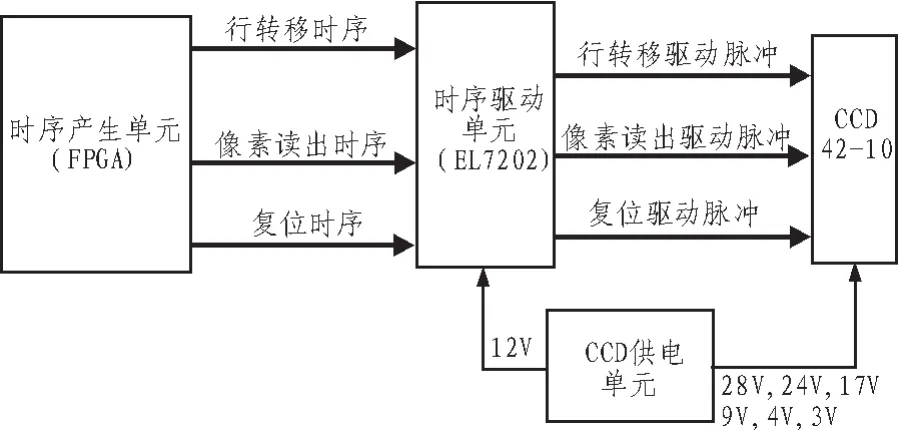

根據前面對驅動時序的分析,如圖3所示,將CCD42-10 BI AIMO的驅動電路分為3個單元進行設計[5]:時序產生單元(FPGA)、時序驅動單元(EL7202)、CCD供電單元。

時序產生單元(FPGA)產生CCD工作所需的驅動時序,然后由驅動芯片EL7202驅動到CCD工作所需的電平值,此電壓由CCD供電單元提供。供電單元還產生CCD傳感器工作必需的偏置電壓。

3.1時序產生單元

選用Xilinx公司生產的Spartan3E系列的XC3S500E型號FPGA,該器件具有豐富的資源,208個接口,500 k系統門,同時還有73 kbit的Distributed RAM和360 kbit的Block RAM,足以滿足此次設計的需求[6]。

圖3 驅動電路結構框圖Fig.3 Driving circuit diagram

在使用VHDL語言編寫程序時,采用自上而下、模塊化的設計方法。選取行轉移頻率為33 kHz,像元讀出頻率為200 kHz,行轉移時序和像素讀出時序占空比均選為50%,復位時序的占空比選為10%。

把驅動時序劃分為3個模塊:行轉移模塊、像素讀出模塊和幀控制模塊。行轉移模塊用于產生CCD進行垂直行轉移所需的驅動時序,包括IΦ1、IΦ2和IΦ3。像素讀出模塊用于產生與水平像素讀出相關的驅動時序,包括RΦ1、RΦ2、RΦ3和ΦR。幀控制模塊用于控制CCD的整個工作過程,包括控制光積分時間、行轉移開始和結束時和像素轉移時序的時間間隔,行轉移次數和像素轉移次數等。每個模塊分別使用有限狀態機實現,然后在頂層文件里使用元件例化的方法調用元件實現驅動時序設計[7]。下面詳細介紹像素讀出模塊的設計,其他兩個模塊不再贅述。

根據驅動時序圖,對像素讀出時序RΦ1、RΦ2、RΦ3和ΦR進行劃分,分為S0-S7共8個狀態,如圖4(a)所示。

圖4 像素讀出時序劃分及狀態機描述Fig.4 Segments and state machine description of pixel readout timing

使用一個有限狀態機來描述像素讀出模塊,如圖4(b)所示。當CCD進行行轉移時,輸出S0狀態的信號;當進行像素讀出時,則連續依次輸出S1-S7狀態的信號,完成一個像素的讀出。 各狀態的跳轉由信號 Rdriver_start和Idriver_start來控制:當Idriver_start為 1時,表明CCD處于行轉移階段,進入S0狀態,輸出行轉移所需要的驅動時序;當Rdriver_start為1時,表明CCD開始準備像素讀出,依次進入S1-S7狀態,不斷循環直至把轉移到水平移位寄存器中的像素完全讀出。

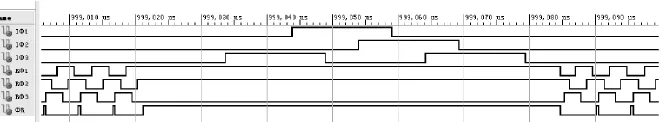

完成對驅動時序的VHDL語言描述后,在ISE 14.2可編程邏輯集成開發環境下,對驅動時序進行仿真,仿真波形如圖5所示,各個驅動時序的相位關系、頻率、占空比等完全符合設計要求。

圖5 時序仿真圖Fig.5 Timing simulation diagram

3.2時序驅動單元

CCD屬于容性負載,對驅動時序信號有著一定的功率要求。CCD42-10 BI AIMO正常工作所需的驅動時序電壓取典型值12V,而FPGA輸出的時序電平只有3.3 V,所以需要驅動芯片將驅動時序信號進行電平轉換。CCD正常驅動時所需的功率,可由下面公式進行計算:

P=C×F×V2

式中:P為功率大小,C為電極等效電容,F為工作頻率,V為驅動時序電壓。CCD42-10 BI AIMO工作時像素讀出所需功率最大,像素讀出引腳等效電容80 pF,驅動時序電壓12 V,取最大工作頻率3 MHz[4]。通過計算,每一相像素轉移驅動脈沖需要的功率為34.56 mW。

根據此計算結果,選用公司的驅動芯片EL7202,它可提供峰值電流2 A,對滿足CCD42-10 BI AIMO功率要求有足夠的裕度。與其他驅動芯片DS0026、ICL7667等相比,EL7202在驅動能力、反應時間、抑制噪聲等各方面表現更為優秀,其上升沿和下降沿變化得更快,更能滿足應用要求。

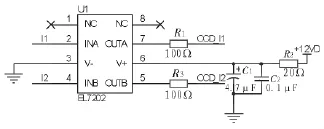

EL7202芯片單電源工作,雙通道輸入輸出。其電路原理圖如圖6所示:V+和V-為供電電壓輸入引腳,分別為12 V 和0 V。供電電壓12 V經過20 Ω的電阻連接到驅動芯片,可防止過沖現象。使用容值為0.1 μF的小電容并聯4.7 μF的鉭電容,減小電源紋波。每個驅動信號經過EL7202驅動后都接有100 Ω電阻,用來調節驅動脈沖的上升沿和下降沿時間,從而滿足CCD驅動信號的要求。

圖6 驅動器EL7202電路圖Fig.6 EL7202 driving circuit

3.3CCD供電單元

CCD供電單元提供給驅動芯片EL7202驅動電平以及CCD42-10 BI AIMO工作所需的各種偏置電壓。CCD42-10 BI AIMO的偏置電壓包括襯底電壓(+9 V)、傾倒漏極(+24 V)、放大器漏極(+28 V)、輸出門極電壓(+4 V、+3 V)和復位管的復位電壓(+17 V)。這些電壓的好壞將直接影響到CCD的電荷轉移效率和輸出信號的信噪比。如果電壓中引入噪聲過大,嚴重的有可能在輸出圖像上產生條紋,所以有必要對這些電壓進行濾波處理,將電壓噪聲降到最低[8]。CCD的偏置電壓所需的電流較小,可以通過調節電阻分壓的方法使用LM117芯片實現,因其電路已經很成熟,在此不再贅述。

4 實驗結果與分析

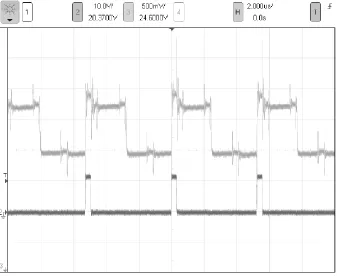

檢測CCD的各種偏置電源正常后,接上CCD42-10 BI AIMO,用示波器對驅動脈沖和CCD的輸出信號進行觀察。圖7中(a)和(b)分別為行轉移脈沖和像素轉移脈沖波形圖。圖8為CCD輸出信號波形。

圖7 行轉移脈沖和像素讀出脈沖Fig.7 line transfer pulse and pixel readout pulse

圖8 CCD輸出信號Fig.8 CCD output waveform

從圖7中可以看出,行轉移脈沖的頻率為33 kHz,像素轉移脈沖的頻率為200 kHz,占空比均為50%,高低電平分別為12 V和0 V,以上驅動脈沖的電平值、頻率、占空比等完全符合設計要求。圖8的CCD輸出波形表明設計的驅動電路可以驅動CCD42-10 BI AIMO正常工作。

5 結 論

使用Xilinx公司Spartan3E系列的XC3S500E型號FPGA芯片,在ISE開發環境下采用硬件描述語言VHDL語言設計出科學級CCD42-10 BI AIMO工作所需的驅動時序信號,并選用高性能的驅動芯片EL7202保證提供給CCD高質量的驅動脈沖信號。仿真與實驗結果表明,此驅動電路設計能夠滿足實際應用要求,可以用來驅動CCD42-10 BI AIMO。

[1]Takako Kato,et al.X-Ray spectral analysis of Yohkoh bragg crystal spectrometer data on a 1992 September 6 Flare:The Blueshift Component and Ion Abundances[J]ApJ,1998,492 (2):822-832.

[2]JanesickJR.Scientificcharge-coupleddevices[M]. Bellingham:SPIE press,2001.

[3]Janesick J.Muti-pinned-phase charge-coupled device[J]. NASA Tech Briefs,1990,14(8):22.

[4]E2V Products.CCD42-10 Back Illuminated High Performance AIMO CCD Sensor Datasheet[EB/OL].[2015-01-09].http:// www.e2v.com/resources/account/download-datasheet/1178.pdf.

[5]常磊,李國寧,金龍旭.基于FPGA的全幀型面陣CCD驅動時序設計[J].光學技術,2006(32):313-316.

[6]Xilinx Products.Spartan3E FPGA Family Datasheet[EB/OL]. [2013-07-19].http://www.xilinx.com/support/documentation/ data_sheets/ds312.pdf.

[7]蔣小燕.EDA技術及VHDL[M].南京:東南大學出版社,2008.

[8]許秀貞,李自田,薛利軍.CCD噪聲分析及處理技術[J].紅外與激光工程,2004,33(4):343-346.

Design of driving circuit of soft X-ray CCD based on FPGA

HAO Yu-ting1,2,WEI Fei1,LENG Shuang1,LI Mi-mi1,2

(1.National Space Science Center,Chinese Academy of Science,Beijing 100190,China;2.Univer Sity of Chinese Academy of Science,Beijing 100190,China)

CCD is the core component for realizing space soft X-ray exploring mission.According to the requirements for space soft X-ray exploring,the scientific CCD42-10 BI AIMO produced by E2V Company has high sensitivity,low noise and high readout speed,and a driving circuit based on FPGA is designed.This design is developed on the XC3S500E hardware platform,using VHDL language to describe the driving timing.The CCD is driven by EL7202 chips.The simulation and testing resultsindicatethattheCCDperformedstably,andthedesignmatchesthedrivingrequirementsofCCD42-10BIAIMO.

soft X-ray;CCD;driving circuit;FPGA

TN386.5

A

1674-6236(2016)03-0094-04

2015-04-16稿件編號:201504166

中國科學院戰略性先導科技專項(XDA04070000)

郝玉婷(1987—),女,江蘇沛縣人,碩士研究生。研究方向:高分辨率低噪聲CCD傳感器讀出系統開發。