無人機圖像壓縮與實時傳輸系統設計

高澤軍,魏本杰,許 睿

(1.中國科學院國家空間科學中心 北京 100190;2.中國科學院大學 北京100043)

無人機圖像壓縮與實時傳輸系統設計

高澤軍1,2,魏本杰1,許 睿1,2

(1.中國科學院國家空間科學中心 北京 100190;2.中國科學院大學 北京100043)

為滿足無人機航拍圖像傳輸對輸入碼率、壓縮率、復雜程度、分辨率大小、數據傳輸實時性等諸多方面的要求,此設計致力于研究一套基于FPGA+兩片ADV212+兩片SDRAM為架構的高性能無人機圖像壓縮與實時傳輸系統。系統采集圖像的原始數據通過FPGA控制進入緩存,之后再由FPGA控制分別進入兩片高速壓縮芯片ADV212。兩片ADV212同時進行壓縮工作,可以極大提高數據的壓縮與傳輸速率。同時,兩片SDRAM作為系統的數據緩存,數據傳輸過程中的可靠性也可以得到保證。實驗結果表明,此系統確保了圖像實時傳輸的高質量,具有良好的工程可操作性和應用價值。

圖像壓縮;系統架構;ADV212芯片;實時傳輸;JPEG2000標準

近些年來,隨著無人機技術的不斷發展,其已經應用到軍事和環境監察等諸多領域[1]。此外,無人機的有效載荷內通常會裝有很多成像設施,這主要用來及時獲取各類圖像信息。另外,由于無人機系統的信息下行信道帶寬通常較短,故信息的傳輸速度往往在很大程度上落后于獲得圖像的速度,如果無人機采集的圖像數據沒有經過壓縮處理就直接傳輸給地面接收站,就會要求發射機能夠傳送大量的數據,并且會占用龐大的信息通道。

結合具體的項目進行分析發現,僅采取提升存儲器容量或提升信道傳輸率的措施并不能夠實現對以上問題的完善解決[2]。而利用數據壓縮方法以減少獲取的信息量,則能夠更加完美的應對這個問題:既能夠減小所需存儲器的容量,這在很大程度上縮小了系統實物的體積也降低實際項目的應用成本,而且又能大量降低傳輸數據量從而達到提高傳輸效率的效果。

針對上述的需求研究,本篇文章以此為基礎設計了一套以JPEG2000編碼芯片——ADV212為主的圖像壓縮處理系統,并且充分利用SDARM以及FPGA有關芯片的技術手段來加強其數據壓縮的穩定性、可靠性,并大大提高其傳輸速率等各方面性能。此系統的關鍵芯片是ADV212,將SDRAM當作數據傳輸的緩存,并通過FPGA對圖像序列進行幀組處理,通過FPGA實現對ADV212的配置和數據流管理。為了防止告訴傳輸過程中出現錯誤而導致數據流失,本設計使用兩片SDRAM作為數據傳輸過程中的緩存,有效地保證了傳輸過程中的數據可靠性[3]。

該系統有著十分快的圖像壓縮速度,壓縮比也是比較高的,同時可以根據規定的比例進行壓縮處理,還具有功耗低,穩定性強的優勢,能夠完美應對無人機圖像對壓縮比、壓縮和傳送的及時性等方面的要求。

1 系統的總體需求分析

根據實際的項目具體需求的提高,本設計對該項目中的無人機圖像壓縮與傳輸部分的總體技術指標分析如下:

1)處理圖像的系統對于數據的傳送速度、數據之間交換的穩定性的要求也是日益增加,這就急需一個比較統一的規定來保證不同的圖像采集卡與相機之間的兼容性。CameraLink不但能夠保證圖像采集卡與相機在高速傳送下的強穩定性,同時在很大程度上減少了客戶的研發成本[4]。CameraLink這個接口利用低差分的信號準則實施信息輸送,相較于傳統接口,具有輸送快、功耗低、不易被擾等優勢。

2)本設計服務的具體項目的任務特征是相機拍攝的圖像視野廣,幀頻比較低,并且圖像是運用到高空偵察上,所以要對適用于該項目的壓縮圖像規定進行論證與選擇。通過諸多分析,最終決定選取JPEG2000準則作為此次設計的圖像壓縮準則。

3)相機采集圖像尺寸為10 M像素,每秒6幀,8 bit,則輸入速率為480Mbps;圖像壓縮芯片數據串行輸出碼速率為4 Mbps;這就要求數據壓縮以及傳輸的時間要保證在1秒/幅,壓縮數據串行輸出的碼率不應該低于4Mbps;為了能夠確保原始圖像進行傳送,串行輸出的速率不應該低于360Mbps[5];根據項目的實際需求,要求恢復圖像與編碼圖像無明顯差異,計算可以得出結論,本設計的壓縮比不能少于25倍。

本設計主要針對是實際工程項目的具體應用,因此,本設計實現的系統能夠滿足以下幾點基本要求:

1)采用JPEG2000標準的圖像壓縮算法并采取專業壓縮芯片以硬件方式實現,在經歷壓縮與傳送之后能保證較好的質量;

2)系統對于圖像進行壓縮和傳輸處理的速度是很快的,壓縮后的傳輸速率完全可以跟上原始數據的采集輸入速率;

3)在一定程度上可以對壓縮比進行合理的調節;

4)簡易的接口,使得系統能夠適用于不同的工作平臺。

2 系統的總體架構設計

根據我們對國內外JPEG2000壓縮方法的詳細調查與研究,研究表明能夠實現該算法的方式主要有以下3個:

1)基于DSP的壓縮算法編程實現方式;

2)基于FPGA的壓縮算法邏輯設計實現方式;

3)基于專業壓縮芯片的實現方式。

但是依據當前的研究情況而言,JPEG2000壓縮算法十分繁瑣,所以,無論在DSP中設計者可以避免繁瑣的底層邏輯時序問題,或選擇把JPEG2000壓縮準則完全復制到PFGA上來,能夠極大的增加并行處理的速度,然而目前的這兩種技術還不夠成熟,算法的工作穩定性也不高,壓縮效果不是很理想,很容易出現問題,十分不利于無人機的高空偵察作業。

綜合利弊,我們直接采用趨于完善的JEPG2000專業壓縮芯片,客戶需要自己去研發底層的邏輯系統,或者去處理復雜繁瑣的壓縮算法的邏輯設計實現難題,設計者僅僅只要考慮壓縮芯片的參數配置來運用有關的功能即可。采用這種類型的壓縮芯片的優點就是技術相當成熟,較好的壓縮性能,比較穩定的工作,另外還具有良好的可操作性。

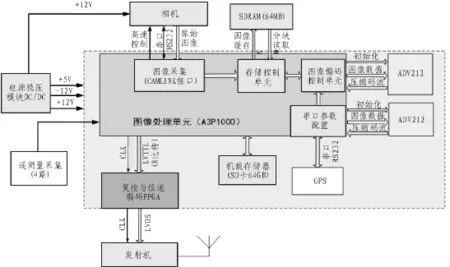

圖像壓縮模塊是本系統的核心設計環節,通過對ADV212和SDRAM的設計,FPGA等芯片共同工作的系統電路的實踐。在FPGA的控制邏輯是由壓縮的圖像壓縮模塊完成,并與外圍電路的通信是通過模塊實現。圖像壓縮模塊用于接收原始圖像數據,將圖像和數據的參數進行分離,然后將圖像分為塊,然后按照預定的格式將壓縮碼流包裝。

所設計的壓縮圖像系統的原理框圖如圖1所示,其電路主要由以下幾部分組成:2片ADV212壓縮芯片,1片FPGA,1片晶振,2片SDRAM,1片同步422串口芯片,3片LDO電源轉換芯片,1片LVDS串口芯片,還有其他TTL與LVDS電平轉換芯片等。

圖1 圖像壓縮傳輸設計原理圖

3 壓縮模塊的傳輸設計

1)Cam link相關硬件電路設計

相機的CameraLink訊號基本包含了高速相機管控訊號、低速串行通信訊號、高速視頻訊號3種訊號。此外,通常情況下,電源并不存在CameraLink連接器內,在電源方面,往往會配置專門的電源接口。2組LVDS訊號均當作圖像收集設備與相機之間的異步通信訊號。

此設計中的串口通信部分包括SerTC與SerTFG兩組信號,他們通過電平轉換芯片與圖像采集模塊電路實現異步通信。這兩組信號傳輸速度最低為9600bps,主要實現了從圖像采集電路模塊的指令信息傳輸到相機和反饋信息,從攝像頭圖像采集模塊。

硬件電路如圖2:相機使用MDR26實現圖像采集卡的接口和LVDS電平轉換接口電路,包括4對LVDS攝像頭數據信號的信號,1對LVDS相機時鐘信號,2雙攝像頭和串行通信信號;FPGA的水平轉換電路和LVDS接口,主要的信號是24 TTL電平數據信號,4個TTL電平數據控制信號,4TTL電平控制信號相機和2 TTL電平的串行通信信號[6]。在串口通信模塊內,驅動器方面主要運用的是SN65LVDS048APW,其把通過相機獲取的SerTC LVDS訊號變換成TTL訊號并傳送到串口。采用驅動芯片SN64LVDS047PW作為接收器將來自串口的SerTFG TTL信號轉變為LVDS信號,并且傳送給相機。相機的控制環節運用驅動芯片SN64LVDS047PW來當做一個接收器,它能夠接收從串口的四組TTL相機發出的控制信號CC1、CC2、CC3、CC4,并且把它們轉化為LVDS信號,在一定程度上對相機實行控制。

圖2 CameraLink接口構造圖

來自于相機的4組LVDS數據信號與一組LVDS時鐘信號在LVDS轉換芯片的驅動下轉換成為24位數據信號從CAMLINKO一直到CAMLINK23,相機的時鐘信號CAMLINKIN_CLK以及4位相機數據的控制信號FVAL,DVAL,LVAL,SPARE。以上的這些控制信號都是十分有效的。輸出的像素數據位依據不一樣的規定會有不一樣的位數,選用德州儀器的SN65LVDS94當作主芯片以達到LVDS轉換的目的。

2)ADV212圖像壓縮

ADV212是一個以JPEG2000標準為基礎的的專用編解碼芯片,適合靜止圖片與視頻的壓縮處理時使用。ADV212的功耗相比同類型的芯片ADV202至少降低了30%[7]。通過不同的內部寄存器配置,ADV212可以在多種模式下工作,適合不同系統對壓縮模式的需求。

該系統由FPGA控制兩片ADV212。圖像數據壓縮為ADV212。壓縮后,該塊的參數被存儲在緩沖區中。由此,此次設計采用ADV212用于實現壓縮的圖像與JPEG2000算法一致,該芯片是實現此配置的主要芯片。

3)FPGA控制

本設計選擇Actel公司的A3P1000芯片,這款芯片具有可達350 MHz的工作主頻,極快的I/O響應速度(<100 ns),700 Mbps的DDR,高速的運行能夠效果能夠完成本系統對于實時傳輸的要求。另外,這款芯片擁有足夠多的I/O口數量,完全能夠滿足本系統對兩片ADV212、CameraLink電平轉換以及其他外設對于數據傳輸或者芯片控制的要求。

FPGA是此系統的核心處理芯片,主要任務就是與外界的其余電路之間進行一個互相之間的通信,同時也負責處理交織、RS編碼、復接問題,最后將數據打包[8],碼流傳輸給發射機,或者,我們也可以將數據存儲入SD卡,以便無人機返回后地面人員取出存儲數據進行再次觀察。

4)SDRAM圖像緩存

本項目采用的高速圖像數據采集模塊產生的圖像原始數據量相當可觀,要做到實時傳輸,那它就對傳輸速率、緩存的空間做出了很強的要求。為了能夠確保圖像數據的可信性以及存儲時的高穩定性,同時也能滿足不同時鐘域之間相互的數據輸送,本設計選擇了ISSI公司的大小為256Mb的SDRAM芯片IS42S16160G作為圖像數據傳輸過程中的中間緩存。通過FPGA來實現對SDRAM的控制,實現原始圖像數據與SDRAM之間的傳入傳出。

圖像壓縮模塊通過FPGA控制SDRAM的讀寫,下行圖像數據緩沖兩SDRAM,然后根據ADV212芯片輸入數據量的圖像子塊,然后讀取圖像的FPGA芯片的高速緩存,等待做圖像壓縮處理。SDRAM用于緩存每個圖像數據,從而能夠確保圖像數據的不丟失。

4 數據傳輸特點

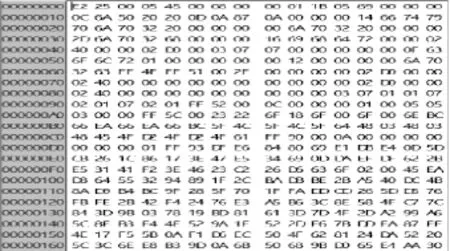

圖3是上位機從SD卡讀取的數據包內容,上位機通過相關軟件,可以將數據包恢復成圖像。

圖3 上位機接收數據圖

在上圖中,左邊一列是數據地址,右邊部分是數據具體內容。E225是本單位數據包固定包頭,隨后是24位時間碼,另外由描述設備狀態、緩存區域大小、數據與類型、包序號、長度域大小、數據域長度和校檢域大小的相關字節共同組成一個數據包。

5 實際圖像處理

圖4是攝像頭從高空拍攝的圖像源圖,圖像采集板將處理后的數據存儲在SD卡中,上位機通過軟件讀取相應數據進行處理,之后還原圖像如圖5所示。由圖4、圖5對比可知,在測試條件較好,比如天氣晴朗,光線充足,可見度較高的情況下,圖像恢復基本無損,恢復圖像也較為清晰。圖6是在可見度相對較差的情況下,在同一地點、同一高度拍攝相同圖像的情況下,由同一攝像頭拍攝之后的恢復圖像。由此可見,圖像采集環境對此系統還是有很大影響的。

圖4 高空拍攝圖像源圖

圖5 高空拍攝圖像處理后

圖6 可見度低下拍攝后的處理圖像

6 結 論

目前本設計中使用了兩片ADV212芯片共同工作的方式,來加強系統對硬件資源的要求,但是受系統的一些實際狀況的限制,此次所設計的系統還是有一些不足與缺點,比如:因為ADV212芯片自身處理狀況的約束,在其工作過程中一次性處理的圖像的尺寸有一定的限制等問題。今后的設計在實際項目應用中可以進一步運用更多的片性能更優的專業壓縮芯片共同工作或者更優秀的壓縮架構設計來達到無人機圖像的實時壓縮與傳輸的目的。

另外,如果無人機上的成像設備采集數據量過大,對數據下行速率提出更高要求,并導致數據壓縮與傳輸速率跟不上相機采集數據的速度[9],本設計的架構也需要適當優化,比如可以考慮加入DSP,來進一步加速數據處理能力。這些問題都是今后系統設計中需要思考解決的問題。

與此同時,此次設計的系統對于系統工作環境以及圖像采集場景之間的適應能力方面還有許多急需完善的地方:我們在高空拍攝圖片會受到天氣、光線強弱、可見度高低和攝像頭質量等相關因素的影響,陰天、霧霾、光線不足等環境因素都會導致我們的圖片處理能力受到明顯影響,這一點在上述文章中已經闡明。以上這些此設計的缺點都是以后急需進一步改良的方面。

[1]于巍巍,馬曉東,孫娟,等.基于多片ADV212芯片的圖像壓縮系統設計[J].空間電子技術,2005(23):15-19.

[2]朱珂.基于JPEG2000的靜態圖像壓縮算法及VLSI實現的結構研究[D].上海:復旦大學圖書館,2004.

[3]鄭成林,龔俊斌,劉福學,等.基于ADV202的無人機序列圖像壓縮系統設計[J].計算機與數字工程,2010(17):22-27.

[4]楊俊,魯新平.基于ADV212芯片的視頻壓縮系統應用設計技術[J].微處理機,2010(4):119-122.

[5]陳根亮.一種基于FPGA的線陣紅外圖像采集與顯示系統[D].合肥:合肥工業大學,2013.

[6]陳根亮.一種基于FPGA的線陣紅外圖像采集與顯示系統:[D].合肥:合肥工業大學,2013.

[7]李天文,趙磊.圖像采集系統的Camera Link標準接口[J].單片機與嵌入式系統,2012(17):31-52.

[8]周云端,何志勇,趙瑞國.基于遺傳算法的加速度控制PID參數自整定研究[J].火箭推進,2012(4):68-71.

[9]李丹,王旭紅,李向前,等.基于控制參數調整的容性逆變器容性深度研究[J].供用電,2015(9):63-68.

Design of system of unmanned aerial vehicles image com pression and real time transfer

GAO Ze-jun1,2,WEIBen-jie1,XU Rui1,2

(1.National Space Science Center,CAS,Beijing 100089,China;2.University of Chinese Academy of Sciences,Beijing 100043,China)

To satisfy requirements of code rate,compression ratio,complexity,resolution ratio,instantaneity of image transmission and input during aerial photographing,this thesis works on designing an effective system of unmanned aerial vehicles image compression and real time transfer which is based on the FPGA,two slices of ADV212 and two slices of SDRAM.In this system,original data of imageswill be transferred into cache,and then transferred into two slices of highspeed compressing chips,ADV212.Two slices of compressing chipswill compress data simultaneously,which willenhances compressing and transmission speed.Experimental results show,two slicesof SDRAM willbe the data-cachingmechanism of system,which will guarantee the reliability during transmitting procedure.With favorablemaneuverability and application value,thisdesign guarantees the high quality of images during real-time transfer.

image compression;system architecture;ADV212 Chip;real time transmission;JPEG2000 standard

TP335.3

A

1674-6236(2016)20-0186-04

2015-10-29 稿件編號:201510225

高澤軍(1991—),男,江蘇江陰人,碩士研究生。研究方向:ARM計算機的航天應用。