基于SOPC的定時器控制數(shù)碼管顯示

王俠,郭海濤

(內(nèi)蒙古大學 電子信息工程學院,內(nèi)蒙古 呼和浩特 010020)

基于SOPC的定時器控制數(shù)碼管顯示

王俠,郭海濤

(內(nèi)蒙古大學 電子信息工程學院,內(nèi)蒙古 呼和浩特 010020)

提出一種控制數(shù)碼管顯示的有效方法,這種方法基于一種特殊的嵌入式系統(tǒng)-SOPC可編程片上系統(tǒng),以SOPC的應用為基礎平臺,利用Quartus II軟件構建硬件系統(tǒng),并利用NiosⅡDES軟件編程,使其運行在DE1上,通過程序的控制使數(shù)碼管顯示,從而實現(xiàn)時鐘的功能。實驗結果表明,基于SOPC的系統(tǒng)環(huán)境下,可以利用定時器控制數(shù)碼管顯示。此外,還可以根據(jù)不同的用戶需求實現(xiàn)不同的功能,方便了對數(shù)碼管的控制,使其控制過程更加簡潔有效。

SOPC;定時器;數(shù)碼管;SOPC Builder

數(shù)碼管是一種半導體發(fā)光器件,對其不同的管腳輸入相應的電流,會使其發(fā)亮,從而顯示出數(shù)字。由于價位低、使用簡單等優(yōu)勢,其在現(xiàn)代工業(yè)控制、醫(yī)療器械及家電領域應用極為廣泛。而隨著顯示數(shù)字位數(shù)的不斷增加,傳統(tǒng)的基于單片機、外部鎖存器和外部譯碼器的設計顯得愈發(fā)的復雜和繁瑣,設計成本也相應的增加,顯示抖動的問題愈發(fā)嚴重。而利用FPGA硬件的并行性操作可以完全消除抖動問題,同時提高設計的可靠性,簡化設計,降低成本,因此對其進行進一步的研究很有必要[1]。

基于FPGA的可編程片上系統(tǒng)SOPC(system on progra mmable chip)技術是當前電子系統(tǒng)設計領域最前沿的技術。SOPC軟核處理器克服了硬核處理器的價格偏高、處理器結構不可更改、無法集成多個處理器等缺陷,具有提升系統(tǒng)的性能、降低集成成本和延長產(chǎn)品的生命周期等優(yōu)勢[2]。定時器是NiosⅡ處理器系統(tǒng)中的一個具有控制啟動、停止和復位等作用的基本單元。

在一個實際系統(tǒng)中,通常需要多個LED數(shù)碼管。多個LED數(shù)碼管不可能同時點亮,動態(tài)顯示指的是多個LED數(shù)碼管的輪流點亮。但其輪流點亮的速度非常快,利用人的“視覺暫留”效應,人眼分辨不出其動態(tài)閃爍,所以在人眼看來數(shù)碼管上顯示的是穩(wěn)定的數(shù)字,在人看來各數(shù)碼管是同時發(fā)光的。用定時器控制數(shù)碼管顯示的原理就是通過在添加組件時配置的定時脈沖來產(chǎn)生中斷,這樣在Nios II DES集成開發(fā)環(huán)境下就可以通過相應的軟件代碼來捕捉定時中斷并記錄數(shù)據(jù),為顯示提供前提。七段數(shù)碼管作為FPGA開發(fā)板上標準的附帶器件,其使用方法已有一套標準,文中針對于DE1(Development and Education Board)提供的七段數(shù)碼管特性設計相應的邏輯模塊,通過SOPC Builder壞境下的用戶邏輯接口工具完成封裝,最后實現(xiàn)在Nios II DES環(huán)境下的使用。

1 SOPC系統(tǒng)介紹

本文主要用到了 SOPC系統(tǒng)的 Nios軟核處理器、Interval Timer定時器和PIO并行輸入/輸出3個主要部件。

1.1 Nios 軟核處理器

單片機、ARM等出廠時處理器固定在芯片上,而Nios II處理器和它們不同,出廠時的FPGA是空白的,里面并沒有處理器,所以Nios II處理器被稱為軟核處理器。Nios II處理器是需要用戶利用軟件進行配置的。Nios II處理器是指令總線與數(shù)據(jù)總線相獨立的哈佛結構、支持32路中斷輸入;與普通處理器不同的是可以自定義指令,這在一些高速數(shù)據(jù)運算中有很大的優(yōu)勢。

1.2 IntervalTimer 定時器

Interval Timer核是SOPC Builder自帶的Nios II基本外設,是avalon總線與外部接口或外部邏輯的連接模塊;Nios II系統(tǒng)可以通過avalon主外設簡單的通過讀和寫控制寄存器以及狀態(tài)寄存器與該核實現(xiàn)通信,從而控制定時器的各種操作。

1.3 PIO 并行輸入/輸出

并行輸入/輸出是Avalon總線的從端外設,提供了通用I/O端口和Avalon總線之間的地址映象接口。這里說的I/O端口既可以與片上用戶其他邏輯相連接,又可以與FPGA的外圍器件相連接。每個PIO核可提供最多32個I/O端口,PIO核可以根據(jù)需要配置成輸入模式,輸出模式及雙向模式,對于輸入模式還可以對處理器產(chǎn)生中斷請求。PIO核是SOPC Builder自帶的IP核,可以很方便集成到Nios II系統(tǒng)中,是常用的Nios II外設之一,其在系統(tǒng)中可以與蜂鳴器,led等外設相連接。

1.4 SOPC系統(tǒng)開發(fā)環(huán)境

SOPC是Altera公司提出的一種靈活、高效的SOC解決方案,是一種新的軟硬件協(xié)同設計的系統(tǒng)設計技術。SOPC系統(tǒng)設計主要包括以32位Nios軟核處理器為核心的嵌入式系統(tǒng)的硬件配置,硬件設計、硬件仿真、軟件調(diào)試等部分[3]。所用的基本軟件有:QuarutsⅡ,SOPC Builder,NiosⅡDES。

2 基于SOPC的數(shù)碼管顯示的硬件實現(xiàn)

2.1 系統(tǒng)硬件結構

基于SOPC的定時器控制數(shù)碼管顯示所用到的組件有Nios II processor,JTAG UART,Interval Timer,System ID Peripheral,HEX_pio,Oh-chip Memory和4個LED(占用28個PIO)。

本設計使用的PIO是與外部的LED數(shù)碼管連接,由于其連接的方式是直接連接,沒有片選,所以我們需要設置4組PIO,用來控制4個數(shù)碼管的顯示,每個數(shù)碼管用7個段選控制,所以我們總共需要28個輸出PIO來控制數(shù)碼管的顯示。

2.2 硬件系統(tǒng)的構建

在SOPC Builder中硬件系統(tǒng)的構建可分為以下幾個步驟:首先,設置時鐘的頻率參數(shù)為25 MHz;其次,添加片內(nèi)存儲器,選擇片內(nèi)存儲器類型為RAM;使用的資源為M4K;數(shù)據(jù)位寬為32,總存儲器大小為12 kbykes;然后添加Nios II處理器,硬件乘法器選擇None,復位向量和異常向量存儲器均選擇前面添加的片上存儲器。更改指令緩存為2 kbyke;配置定時器,更改預置為Full—featured;添加JTAG UART,均選用默認裝置;配置4個7位并行輸出的PIO,數(shù)據(jù)位寬選擇7;最后,自動分配基地址,自動分配中斷優(yōu)先級,生成系統(tǒng)。

2.3 硬件系統(tǒng)的編譯

硬件系統(tǒng)的編譯可分為以下幾個步驟:首先,在新建的Verilog文檔中添加復位程序并保存,并將該模塊例化到頂層文件。復位的內(nèi)容主要是復位外部輸出為低電平有效;復位低電平信號;復位寄存器為低電平有效和異步復位。其次,對系統(tǒng)生成后產(chǎn)生的inst.v文件進行相應的接口例化更改,得到工程頂層模塊代碼;編譯文件并分配管腳;編譯整個工程,生成下載用的*.pof文件;將DE1開發(fā)板與計算機連接好,給開發(fā)板上電;最后,將生成的*.pof文件下載到開發(fā)板中。

3 定時器控制數(shù)碼管顯示的軟件實現(xiàn)

3.1 軟件設計

目前大多數(shù)的FPGA采用硬件描述語言進行設計。本次設計采用Verilog HDL語言在系統(tǒng)級使用,在軟件級采用的是C語言。利用定時器控制數(shù)碼管顯示的軟件程序設計由定義寄存器映射的頭文件和在Nios II系統(tǒng)中的驅動程序組成。

3.1.1 頭文件的設置

基于SOPC的定時器控制數(shù)碼管顯示所用頭文件如下:

#include“system.h”//系統(tǒng)硬件定義頭文件

#include“alt_types.h”//數(shù)據(jù)類型宏定義文件

#include“altera_avalon_pio_regs.h”//PIO外設頭文件

#include“altera_avalon_timer_regs.h”//定時器外設頭文件

3.1.2 程序設計

對于定時器控制數(shù)碼管顯示的程序設計,可分為3個部分分別是初始化系統(tǒng)、中斷函數(shù)和循環(huán)掃描數(shù)碼管顯示。

首先,初始化系統(tǒng)包括定時器初始化和PIO初始化:

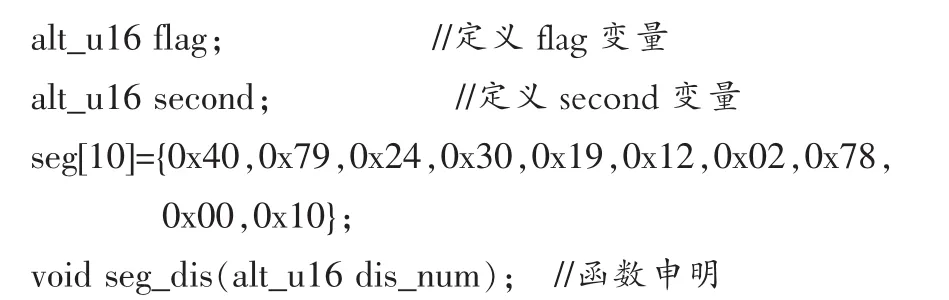

其中,alt_u8 seg[10]是對阿拉伯數(shù)字0到9進行定義,根據(jù)DE1開發(fā)板上有4個數(shù)碼管顯示,可以根據(jù)其不同的設置顯示控制其每一段的亮滅。由于其是共陽極[4],所以為其任意一段提供一個低電平就可以點亮數(shù)碼管,提供一個高電平就可以控制數(shù)碼管不亮。

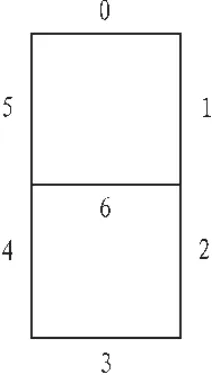

DE1中的七段數(shù)碼管沒有片選,只有位選,這樣我們就可以通過程序來直接控制每一位的顯示,并且4個數(shù)碼管可以同時點亮,再根據(jù)圖1所示的其每一段的位置在數(shù)碼管上的顯示,可以得出阿拉伯數(shù)字的二進制表示。

根據(jù)圖1可以得到:

0的二進制表示為1000000,十六進制表示為0x40;

1的二進制表示為1111001,十六進制表示為0x79;

2的二進制表示為0100100,十六進制表示為0x24;

3的二進制表示為0110000,十六進制表示為0x30;

4的二進制表示為0011001,十六進制表示為0x19;

5的二進制表示為0010010,十六進制表示為0x12;

6的二進制表示為0000010,十六進制表示為0x02;

7的二進制表示為1111000,十六進制表示為0x78;

8的二進制表示為0000000,十六進制表示為0x00;

9的二進制表示為0010000,十六進制表示為0x10。

圖1 七段數(shù)碼管上每一段的位置

本設計的中斷函數(shù)如下:

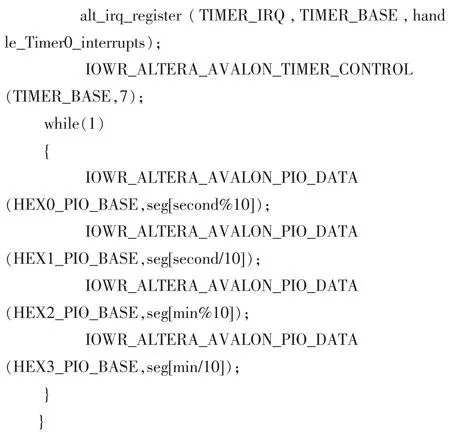

中斷函數(shù)的思路是:定時器中斷默認的周期值是1 ms,如果我們設置中斷函數(shù)中的flag值為1 000,那么正好可以使每次調(diào)用中斷函數(shù)的值為1 s,也就是每次數(shù)碼管顯示的每兩個數(shù)值間隔1 s。

最后,是循環(huán)掃描數(shù)碼管顯示[5],使其實現(xiàn)秒表功能的程序設計:

3.2 軟件實現(xiàn)

軟件開發(fā)過程是實現(xiàn)基于SOPC的利用定時器控制數(shù)碼管顯示的另一個重要組成部分,利用定時器的原理來實現(xiàn)數(shù)碼管的不同實現(xiàn)是本設計的難點,首先需要掌握Nios II DES軟件的使用,并且能夠熟練的操作[6]。本文的軟件開發(fā)過程由以下幾部分組成:

1)在Nios II DES中新建一個 NIOS II Application and BSP from Template工程,

2)對新建的NIOS2軟件進行設置。

3)配置工程的系統(tǒng)屬性。先設置軟件的編譯屬性;再在新生成的工程中添加C源文件,將編寫好的使用定時器控制數(shù)碼管顯示的程序添加到新建文件中;最后,添加利用定時器實現(xiàn)數(shù)數(shù)功能的程序。

4)編譯新生成的工程。

5)將編譯之后的程序運行在開發(fā)板上,查看結果。

4 結論

實驗結果說明根據(jù)SOPC系統(tǒng)的開發(fā)原理,利用Quartus II軟件中的SOPCBuilder開發(fā)工具構建硬件系統(tǒng),在NiosII EDS軟件中通過軟件程序的控制可以實現(xiàn)數(shù)碼管的秒表功能。

文中分為兩大部分,一部分是設計基于SOPC的定時器控制數(shù)碼管顯示的硬件部分,另一部分是利用定時器控制數(shù)碼管顯示的軟件設計。文中利用SOPC系統(tǒng)原理實現(xiàn)了定時器控制數(shù)碼管的顯示,這樣大大提高了設計的便捷性并且提升了數(shù)字系統(tǒng)的性能。根據(jù)不同的用戶需求可以通過軟件編程來實現(xiàn)不同的功能,這樣方便了對數(shù)碼管的控制,是其控制過程更加簡潔有效。

[1]吳厚航.愛上FPGA開發(fā)[M].北京:北京航空航天大學出版社,2011.[2]楊軍.面向SOPC的FPGA設計與應用[M].北京:科學出版社,2012.

[3]YI Wu.Design of embedded web module based on SOPC[C]//國際會議.中國重慶:2012.

[4]邱鋒波.基于FPGA的并行數(shù)碼管顯示控制設計[J].科學技術與工程,2009,9(23):7170-7173.

[5]張行松.LED數(shù)碼管顯示電子鐘PLC程序設計原理[J].黃岡師范學院學報,2011,6(31):54-56.

[6]王銳.基于軟核NiosⅡ的SOPC數(shù)據(jù)采集系統(tǒng)的設計[J].計算機測量與控制,2008,16(8):1199-1201.

Digital tube display controlled by a timer based on SOPC

WANG Xia,GUO Hai-tao

(Electronic Information Engineering College,Inner Mongolia University,Hohhot 010020,China)

Put forward an effective method to control the digital tube display,this method is based on a special kind of embedded system-the SOPC system on programmable chip,on the basis of the application of SOPC,about building a digital system that is controlled by a timer in the Quartus II software,and programming in the Nios II EDS software to make it run in DE1,through the control the digital tube display program,realize the function of clock.Experimental results show that the digital can display by the controlling of timer in the system of SOPC.In addition,you can realize different functions according to different requirements of users,it can convenient for controlling the digital tube,and make it more concise and effective.

System On Programmable Chip(SOPC);timer;digital tube;SOPC Builder

TN141.6

A

1674-6236(2016)15-0162-03

2015-07-26 稿件編號:201507169

內(nèi)蒙古大學高層次人才引進科研資助項目(135123)

王 俠(1990—),女,內(nèi)蒙古烏蘭察布人,碩士研究生。研究方向:嵌入式技術、圖像處理。