高速低功耗SRAM體系結構及設計仿真

趙以誠,周 剛

(中國電子科技集團公司第四十七研究所,沈陽110032)

高速低功耗SRAM體系結構及設計仿真

趙以誠,周剛

(中國電子科技集團公司第四十七研究所,沈陽110032)

提出了一種高速低功耗1M-bit靜態隨機存儲器的體系結構設計,在此體系結構基礎上完成了整體電路架構的搭建。同時,運用Hspice模擬電路仿真工具完成了電路系統仿真。在5V電源電壓下,采用CSMC 0.35μm工藝模型,地址取數時間為15ns,平均動態功耗為100mA,靜態功耗為6mA,實現了靜態隨機存儲器高速、低功耗的良好性能。

靜態隨機存儲器;體系結構;高速低功耗;譯碼器;靈敏放大器;內核

1 引 言

由于現代數字系統需要高速存儲能力,因此越來越高密度的存儲器設計與制造技術被人們所采用,無論是最早的獨立式存儲器,還是發展迅速的嵌入式存儲器,在未來都是集成電路市場中持續增長的部分。

主要針對異步獨立式1M-bit靜態隨機存儲器(SRAM)的體系結構進行了細致的分析與設計。首先提出一種新型的1M-bit SRAM體系結構,然后按照這種體系結構,對整體電路進行搭建,最后完成整體電路的模擬仿真,并分析其波形結果和性能指標,總結后得出結論。

2 1M-bit位SRAM體系結構

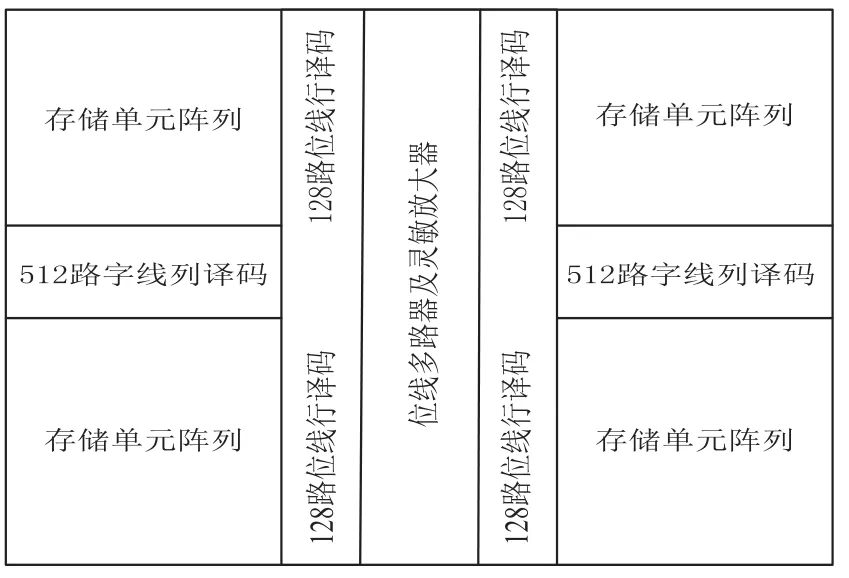

下面設計一種1M-bit SRAM體系結構,采用多層次的譯碼結構,如圖1所示,從而更好地實現并滿足靜態隨機存儲器高速低功耗的特點。

其中包含的存儲單元內核陣列是圖中最大的塊。512路列譯碼器分布在橫向左右兩側,128路位線行譯碼分布在縱向兩側,位線多路器和靈敏放大器放置在內核陣列的中間部分。

其中列譯碼器由一個初級譯碼器和一個次級譯碼器組成,它用來驅動豎直方向穿過陣列的字線。而每一對位線連接一個位線行譯碼器,同時這個譯碼器連接著位線的I/O電路,一般包括靈敏放大器和寫驅動器電路。所有的存儲單元都在水平方向和垂直方向上鏡像排列成規則陣列[1]。

該靜態隨機存儲器的容量一共1Mbit,每次讀寫一個由8bit構成的字節,又由于是八位并行數據輸出,所以可以寫成128K×8bit。由于1M

位的存儲器可以按照下面的等式計算:1Mbit=128×1024×8=27×210×8bit。

圖1 存儲器體系結構

所以,如果能夠完成所有位的隨機寫讀,一共需要17位的地址進行譯碼操作。

由于1M位SRAM容量較大,它的陣列長度和寬度過大,導致了連接存儲單元的橫向字線與縱向位線較長。因為金屬互連導線的RC延遲與長度的平方成正比,所以整體存儲器的訪問時間也與陣列的寬度和高度的平方成正比[2]。同時,隨著陣列的增加,大容量存儲器帶來的導線電容增大,會使得一次讀寫所消耗的功耗過大。如何實現高速低功耗的1M-bit SRAM體系結構設計,是研究的關鍵內容。

設計的存儲器體系結構按照分塊譯碼、列譯碼(字線譯碼)、行譯碼(位線譯碼)三個層次進行劃分,最終有效實現一個字節的讀寫功能操作。

首先進行塊譯碼劃分。通過把存儲器陣列分割成一定數量的小塊,然后利用塊地址譯碼選中需要讀寫的一塊,如此可以顯著降低橫向字線的長度。另外,使用分級譯碼操作后,可以改善字線過長帶來的電阻過大、字線開啟延遲時間過長的問題[3]。

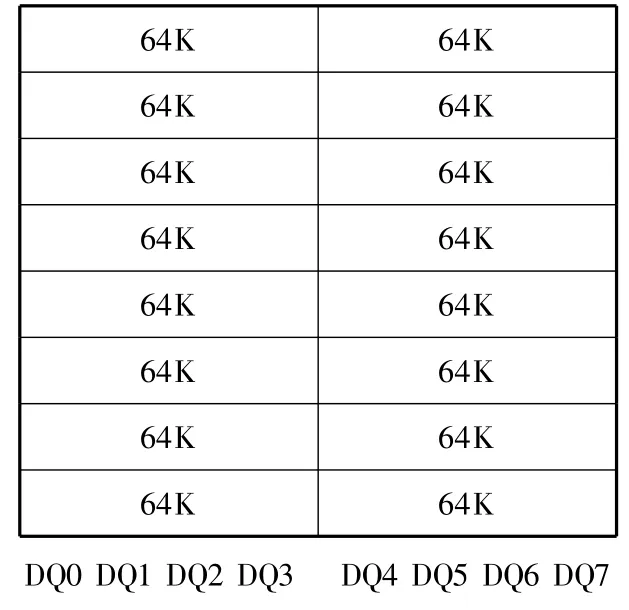

設計中將1M-bit SRAM分成八大塊,每一塊為128K,它由A8、A9、A11三個地址組成的三八譯碼器實現。接著,地址A13將每一塊分成左右2小塊,每一小塊為64K,由此將整個存儲器分成了16小塊,如圖2所示。

圖2 分塊后的SRAM陣列

經過塊譯碼操作后,將一條豎直的長字線分成了8段。這樣,每次讀寫時,僅在某一塊中的字線被開啟,使得分塊后字線上的延遲比原來分塊的延遲降低了64倍。

其次進行列譯碼(字線譯碼)劃分。設計中的列譯碼實質上屬于字線譯碼,以其中一個64K的小塊為例,它在橫向上一共有512列單元,也就是有512根字線[4]。

由于512=29,所以字線譯碼需要9個地址,設計中采用A3-A7,A12,A14-A16地址作為字線譯碼。

因為字線一般用多晶硅制作,并且由于分布的RC寄生參數對信號產生一定的延遲,極大影響了存儲器的讀寫速度,而且上面的大電容也帶來了額外功耗。

為了減少延遲和功耗,設計采用了一種新的SRAM字線分割技術。其核心技術在于用A3-A7,A12,A14等7個地址定義全局字線,總共產生128條全局字線[5]。這128條字線不直接驅動存儲單元,因此比正常字線的電容小得多。余下的兩個地址位A15、A16用于產生實際驅動單元存取管的局部字線,一共產生128×4=512根字線。

由于之前劃分了8個大塊并且使用局部字線對其進行存取,總單元電容減少的最大因數是8。因此,這種設計使得功耗大大減少,同時使字線上的延遲也減小,加快了存儲器的讀寫速度。

最后進行行譯碼(位線譯碼)劃分。設計中的行譯碼實質上屬于位線譯碼,以64K的小塊為例,它在縱向上一共有128對位線,這128對位線又分為8組,每組中包含16對位線。經過位線譯碼的作用,從16對位線中選中一對位線,每一對位線對應1位。如此,8組中同時被選中一對位線連接到靈敏放大器作為輸出,便實現了8位輸出,即一個字節的輸出。

由于16=24,所以位線譯碼需要4個地址,設計中采用A0-A2構成3-8譯碼器,然后再與A10組合成4-16譯碼,最終選中需要讀出的存儲單元位線。

由于一對位線通常用金屬制作,所以它的電阻相對較小,但是隨著金屬線變長變細,它的延遲效應不可忽略[7]。同時,連線和許多連接到它上面的平行存取管的組合電容使每條線上都有一個大的等效集總電容,因此也帶來了額外功耗。

設計中首先采用地址A13將128K分成左右2小塊的64K,目的就是為了將很長的位線分割成左右兩部分,從而減小信號延遲。同時,每兩對位線之間用電源和地的寬金屬線隔離開,減小等效集總電容,如此一來也就減小了額外功耗。

總之,以上采用了分級字線、位線譯碼技術,形成了多層次的譯碼結構,使得它的字線和位線的延遲時間要減小很多,而且最大限度地節約了譯碼時間,降低了陣列功耗,從而實現高速低功耗的1M-bit SRAM的體系結構設計。

3 1M-bit SRAM的整體電路架構

根據以上1M-bit SRAM體系結構的論述,設計出它的具體電路架構,如圖3所示。它的電路結構完全按照SRAM的體系結構進行搭建,主要包括控制電路、地址譯碼電路、存儲單元陣列核心電路、I/O電路四部分,組成整個1M-bit SRAM的體系結構[6]。其中,A<16:0>端口為地址輸入端;DQ<7:0>為數據I/O端口;NCS為片選信號;CE為使能控制信號端;NEW為讀寫控制信號端;NOE為I/O讀控制端。

其中控制電路主要產生讀寫控制信號、I/O控制信號、片選使能信號,以確保電路能夠正常實現功能操作。

地址譯碼電路由地址A<16:0>按照規律組合而成,主要包括2-4譯碼器,3-8譯碼器,4-16譯碼器等等。

圖3 1M-bit SRAM的電路架構

I/O電路指的是輸入輸出電路,設計它時必須考慮到存儲單元設計和存儲器的時序規范,否則存儲器在讀寫時數據會發生錯亂,導致功能失效。

總之,在設計整體電路時,既要保證各個部分電路連接的正確性,又要保證其功能和時序的正確性,這樣才能實現整個電路系統的穩定性。

4 仿真數據與波形

仿真采用csmc 0.35μm工藝模型,采用Hspice仿真工具,工作電壓源為5V。為了能夠更好的觀察仿真結果,本設計只給出TT_25度的波形[7]。

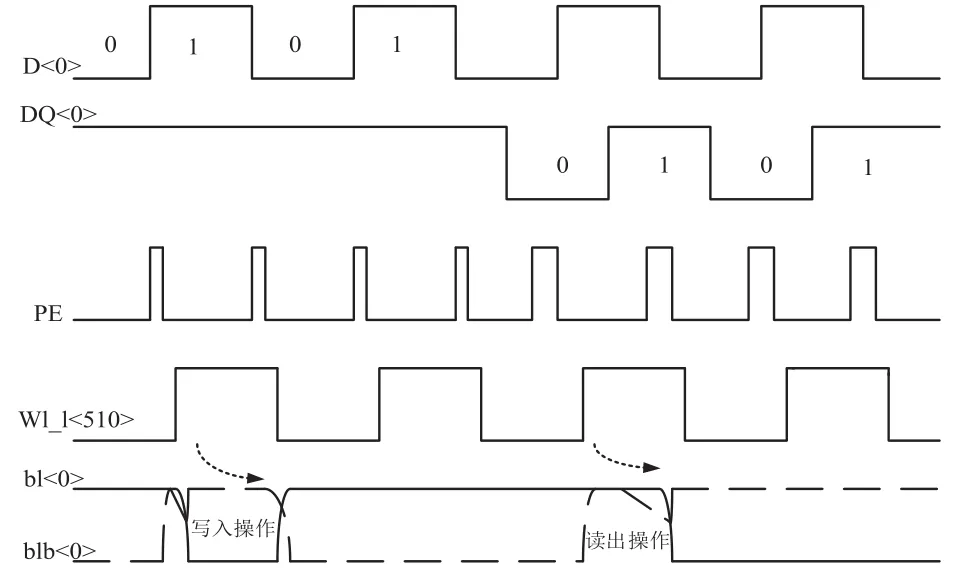

如圖4所示,觀察8個輸入、輸出中的D<0>、DQ<0>,前200ns為寫入數據時間,后200ns為讀出時間。在寫入周期內連續寫入4個數據0101,而在讀出周期內連續讀出4個數據0101,可以看出存儲器的讀寫功能正確。

如果觀察某個1bit存儲單元的讀寫情況,可以通過觀察這個存儲單元的一對位線變化情況即可。

在圖4中,選中了1M-bit SRAM的一條關鍵路徑中的一個存儲單元,分別通過塊譯碼、字線譯碼、位線譯碼來確定這個存儲單元的位置。將地址A<16:0>分別進行組合譯碼,選中第八塊的左半部分;經過字線譯碼,選中第510條字線那一列的單元;經過位線譯碼,選中每一組位線中的第0條位線。所以,需要觀察的目標是一對位線為bl<0>,blb<0>,一條字線為wl_l<510>的那個單元,如此便選中了需要觀察的這個1bit存儲單元。

圖中畫虛線箭頭的部分,分別為這個1bit存儲單元的寫入、讀出操作過程。存儲單元寫入時,blb<0>要完全被拉到低電平,并維持10ns左右,這樣才可以使單元內部的信號翻轉,寫入正確的數據;讀出過程中,由于bl<0>,blb<0>連接到外部的靈敏放大器,所以二者只需有微小的電壓差即可被靈敏放大器識別放大,blb<0>的電平略有下降,但不必完全下降到低電平,這樣便提高了存儲器的讀出速度[8]。

圖4 寫入、讀出功能仿真

5 結束語

提出了一種高速低功耗的靜態隨機存儲器體系結構,并根據這種體系結構,構建了1M-bit SRAM的整體電路架構。利用Hspice仿真工具對整體電路進行模擬仿真,通過觀察電路關鍵路徑中某一個1bit存儲單元的寫入、讀出情況,可以看出設計基本上滿足隨機存儲器的功能、速度、功耗等參數的性能指標。在今后的工作中,根據電路布局,可以完成它的物理版圖設計,進而流片制造出成品。

[1][美]拉貝爾,等著.數字集成電路—電路、系統與設計[M].周潤德,等譯.北京:電子工業出版社,2004.[American]Rabaey,J.M.Digital Integrated Circuits:A Design Perspective[M].Zhourundei Translate.Beijing:Electronic Industry Press,2004.

[2]T Hirose,et al.A 20-ns 4-Mb CMOS SRAM with Hierarchical Word Decoding[J].IEEEJournal of Solid State Circuits,1990,25(5):1068-1074.

[3]T Ootani,et al.A 4-Mb CMOS SRAM with PMOS Thin-Film-Transistor Load Cell[J].IEEE Journal of Solid State Circuits,1990,25(5):1082-1092.

[4]J Chang.Theory of MNOS Memory Transistor[J].IEEE Trans.ElectronDevices,1977,ED-24:511-518.

[5]B S Amrutur,M A Horowitz.Fast Low-Power Decoders for RAMs[J].IEEE Journal of Solid-State Circuits,2001,36(10):1506-1515.

[6]B Prince,Emerging Memories:Technologies and Trends[M].Kluwer Academic Publishers,Boston,MA,2002.

[7]何樂年,王憶,編著.模擬集成電路設計與仿真[M].北京:科學出版社,2008.Helenian,Wangyi,Compile.Analog CMOS Integrated Circuits Design[M].Beijing:Science Press,2008.

[8][美]宋莫康,等著.CMOS數字集成電路—分析與設計[M].王志功,等譯.北京:電子工業出版社,2005.[American]Songmokang.CMOSDigitalIntegrated Circuits:AnalysisandDesign[M].Wangzhigong Translate.Beijing:Electronic Industry Press,2005.

Design and Simulation of System Structure of High Velocity and Low Power SRAM

Zhao Yicheng,Zhou Gang

(The 47th Research Institute of China Electronics Technology Group Corporation,Shenyang 110032,China)

A design of a system structure of high velocity low power 1M-bit SRAM is described in this paper,and the construction of circuit is finished on the basis of system structure.At the same time,the simulation of the circuit system is accomplished by Hspice.In the conditions of 5V and CSMC 0.35μm process model,with the address access time of 15ns,the average dynamic power of 100mW and the static power of 6mW,good capability of low power and high velocity SRAM are carried out.

Static random memorizer;System structure;High velocity low power;Encoder;Sensitive amplifier;Kernel

10.3969/j.issn.1002-2279.2016.05.002

TN603

B

1002-2279(2016)05-0006-03

趙以誠(1984-),男,遼寧沈陽人,工程師,主研方向:集成電路設計。

2016-06-13