基于FPGA的PClE總線DMA傳輸的實現

張鵬泉,褚孝鵬, 曹曉冬,范玉進,汪 振

(天津光電集團公司,300211)

基于FPGA的PClE總線DMA傳輸的實現

張鵬泉,褚孝鵬*, 曹曉冬,范玉進,汪 振

(天津光電集團公司,300211)

為了實現不同應用條件下對高速數據傳輸的不同要求,本文提出一種基于FPGA的PCIE DMA傳輸結構及其實現方法,可以利用不同的工作模式靈活應對不同的高速數據傳輸需求,有效地將上位處理器從數據傳輸工作中解放出來,具有移植性強,傳輸效率高,數據負荷長度靈活等特點。

FPGA;PCLE;DMA傳輸

隨著電子器件運算速度的高速發展,尤其是在寬帶高速信號采集、數據高速存儲、圖像處理等領域,新出現的器件和設備對數據的傳輸速度和帶寬有了更高的要求。PCI Express總線作為第三代I/O總線的代表,能夠通過差分鏈路來提供高性能、高速、點到點的串行雙工數據傳輸,可以對單板上的分層總線結構提供最理想的支持,已經被廣泛應用到計算機與各種外設組件之間的互連領域。

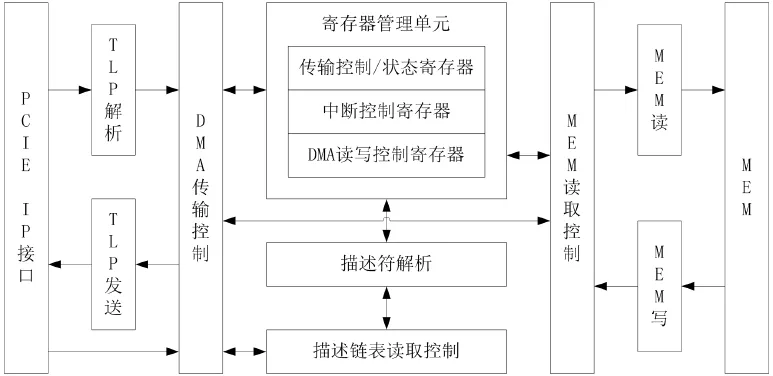

圖1 DMA控制器結構圖

目前,市場上可以使用的PCIE橋接芯片種類較少,且往往受到鏈路寬度的限制,所以單純使用橋片與USB3.0等其它總線相比并不具有明顯優勢。另一方面,目前主流的FPGA供應商均支持PCIE IP核,基于FPGA的設計可增大系統靈活性,穩定性,板卡的速度快,可擴展性強,系統集成度高,所以使用FPGA實現PCIE鏈路成為越來越多開發者的首選。本文提出一種基于FPGA的PCIE DMA傳輸控制器的實現方式,可以靈活適應不同速率、不同鏈路帶寬的IP核設置,具有移植性強,傳輸效率高,數據負荷長度靈活等特點,可以有效地將上位處理器從數據傳輸工作中解放出來,為數據的高速傳輸與高效處理提供了優秀的技術支持。

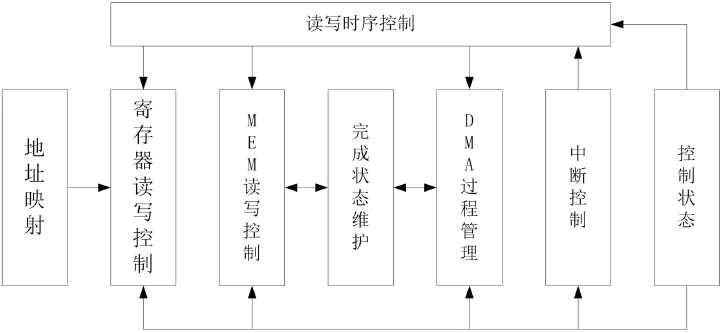

圖2 DMA傳輸控制單元結構圖

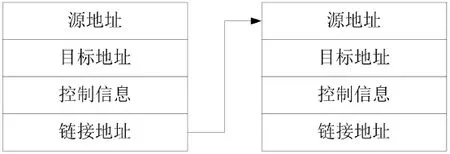

圖3 描述符鏈表結構

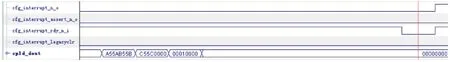

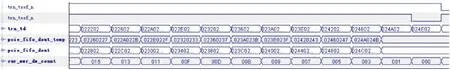

圖4 直接傳輸讀TLP及中斷控制信號

圖5 直接傳輸寫TLP

DMA控制器實現了3種傳輸模式,直接傳輸模式,直接DMA傳輸模式和描述符DMA傳輸模式,其結構如圖1所示。直接傳輸模式由上位處理器直接發起讀/寫TLP,由端點FPGA執行,此種模式適用于數據傳輸量較小的寄存器讀寫或者數據傳輸地址和長度相對度固定的批量數據傳輸。直接DMA傳輸模式由上位處理器發起并提供必要的控制信息,由端點FPGA發起讀/寫TLP,實現數據交換,此種模式適用于傳輸數據的地址和長度相對固定,但需要多次傳輸或數據量較大的情況。描述符DMA傳輸模式則由上位處理器建立描述符,其中包含傳輸地址、長度、方向等信息,然后將描述符組成描述符鏈表,將鏈表的起始地址、長度等信息提供給端點FPGA;端點FPGA則依次讀取鏈表中的描述符,解析后發起讀/寫TLP,完成傳輸操作,直到鏈表結束,此種模式適用于傳輸數據的地址不斷變化,傳輸數據較少且傳輸次數較多的情況。

DMA傳輸控制器的核心處理環節為DMA傳輸控制,其結構如圖2所示,主要功能包括:

1)根據PCIE IP核提供的基址維護一個1KB的控制狀態寄存器地址空間;

2)所有對寄存器地址空間的讀/寫操作均認為是直接讀寫模式,且數據長度固定為1DW;

3)確保讀/寫過程的獨立性;

4)根據寄存器的狀態進行數據傳輸邏輯和時序控制;

5)讀操作中的完成維護。

DMA傳輸控制器的關鍵數據結構為描述符鏈表,其結構如圖3所示。其中,所有地址均采用DW對齊方式,源地址為讀取數據的起始地址,目標地址為存儲數據的起始地址,鏈接地址為下一個描述符的起始地址。在傳輸控制信息中,則包括了以DW為單位的傳輸數據長度,傳輸方向和首尾DW中以字節為單位的數據有效標志位。

根據以上設計思路,由上位處理器發起的直接傳輸讀TLP及其中斷控制信號如圖4所示,直接傳輸寫TLP如圖5所示。

在PCIE×8鏈路條件下,由上位PC機發起,由端點FPGA執行的描述符DMA傳輸模式數據速率測試如表1所示。

如表1所示,在回環測試中數據量一定的條件下,隨著數據報文長度增加,報文數據數量減小,處理器干預傳輸的次數減小,整體的數據傳輸速率呈上升趨勢,且隨著上位處理器的速率提高有進一步躍升。

綜上所述,本文基于FPGA所實現的DMA傳輸控制器,不依賴于特定的FPGA平臺,速率和鏈路帶寬均可靈活配置。同時,可以利用不同的工作模式靈活應對不同的高速數據傳輸需求。目前,該設計已經在多個產品平臺中獲得應用,效果良好。

[1]王齊.PCI Express 體系結構導讀.機械工業出版社.2010.3

[2]劉軍偉.多種高速串行總線的對比研究與分析.電子測試.2016.03

[3]李曉寧,姚遠程,秦明偉.基于PCIe的高速接口設計.微型機與應用,2016,35(1):27~29,32

[4]肖明國 ,董明利,劉鋒,婁小平,祝連慶.基于PCIe總線的數據采集卡設計與實現.計算機測量與控制.2016.24(3)

Implementation of PCIE bus DMA transmission based on FPGA

Zhang Pengquan,Zhu Xiaopeng*,Cao Xiaodong,Fan Yujin,Wang Zhen

(Tianjin photoelectric group company,300211)

In order to realize different application conditions of high-speed data transmission requirements is proposed in this paper a based on FPGA PCIe DMA transmission structure and its realization method,you can use different operation modes of the flexible respond differently to the high-speed data transmission requirements,effectively will host at the processor to be liberated from the data transmission,has strong portability,high transmission efficiency,the length of the data load flexible features.

FPGA;PCLE;DMA transmission

表1 描述符DMA傳輸模式數據速率測試表