基于SoCFPGA同步數據采集系統的設計

楊志芳,胡夢蝶,陳玨,王磊

武漢工程大學電氣信息學院,湖北武漢430205

基于SoCFPGA同步數據采集系統的設計

楊志芳,胡夢蝶,陳玨,王磊

武漢工程大學電氣信息學院,湖北武漢430205

為實現電能質量分析系統多通道數據同步采集的功能,設計一種基于SoCFPGA的同步數據采集系統,采用Altera SoCFPGA為核心硬件平臺,結合ADS8364模數轉換芯片構建了6通道數據同步采集系統.首先,采用軟硬件協同設計方法,使用VHDL對AD轉換控制過程的邏輯進行描述,然后利用FFT核進行數據處理,對測試數據的幅頻特性進行顯示,為后續的諧波分析做準備.仿真結果表明:SoCFPGA實現了對ADS8364的控制以及512點FFT運算.系統使得數據采集硬件結構更加簡單,集成化程度更高,縮短了系統開發周期,能夠滿足數據同步采集的實際需求.

同步數據采集;SoCFPGA;ADS8364;軟件仿真

1 引言

電能是當代社會最為依賴的能源,電能的應用深入到生活中的方方面面,由于電力電子技術的飛速發展,在現代社會中,一些大功率變流、變頻裝置等在電力系統中被廣泛地應用,變頻、變流這些裝置對電網造成非常嚴重的諧波污染,導致電能質量下降,進而會影響到一些高精度自動化儀表的工作特性.因此,開展對電能質量的監測十分重要,同時電能質量問題也是影響電力系統運行和國民經濟發展的關鍵因素.多通道數據采集作為一種計算機從外部實時獲取并處理信息的方法,其重要性不言而喻[1].現有的數據采集方案往往以DSP或單片機作為控制器,用來控制存儲器、ADC(模/數轉換器)和其他的外圍電路的工作.但是由于單片機受到自身的指令周期以及處理速度的限制,還未能達到多通道高速數據采集系統的要求,DSP相對于單片機,能夠實現更高速的數據采集,但是在速度提高的同時,會使得系統的成本相應提高.DSP和單片機的各種功能要依靠軟件的運行來實現,且執行的效率和速度往往不高,軟件的運行時間占用了很大一部分的采樣時間[2].在現有的研究基礎上,設計了一種基于SoCFPGA的同步數據采集系統,FPGA在高速數據采集方面比單片機和DSP要更有優勢,其執行速度快,內部的延時小,控制邏輯均由硬件編程語言來實現,片內時鐘的頻率高,開發效率高.通過仿真驗證了數據采集系統的可行性,可以應用于高速實時數據采集等領域.

2 系統原理

為了滿足質量檢測的需要,對電能質量的關鍵指標加以研究,以Altera公司的SoCFPGA芯片為開發平臺,進行硬件和軟件的設計,實現電能質量分析儀的研制.系統中電壓、電流互感器用來采集電網三相電壓和三相電流數據,經過調理電路后輸送到AD芯片進行模數轉換.SoCFPGA的FPGA子系統主要用來控制AD芯片進行模數轉換并對AD轉換結果進行FFT運算,將AD轉換結果和FFT分析結果送入SoCFPGA的ARM子系統,電能質量的相關參數:三相電壓電流有效值,功率因數,三相電壓電流不平衡度等的計算及電壓瞬變、閃變、諧波分析均在SoCFPGA的ARM子系統中完成[3-4].系統可以對測量數據與分析結果進行本地存儲.系統的測量結果利用MTL2觸摸屏可進行本地顯示及回放.通過配備的以太網接口,與遠程服務器進行通訊,可以實現數據的上傳與遠端保存.本文主要研究的是對獲取的三相電壓電流進行AD轉換以及FFT部分,整體的系統原理框圖如圖1所示.

圖1 系統原理框圖Fig.1System principle block diagram

3 數據采集系統硬件介紹

3.1 SoCFPGA介紹

在數據采集部分中將被測量的電壓、電流數據先分別通過電壓、電流互感器進行采集,然后經過信號調理電路如差分信號放大等將數據送到AD芯片中進行模/數轉換.對于數據采集部分,必須配以一個高速、高精度的CPU(本文中為SoCFPGA的FPGA子模塊),使其具備實時事務處理能力和數據處理能力[5],本系統中用到的SoCFPGA器件在同一個器件中同時集成了處理器和FPGA體系結構,將兩種技術合并起來,系統具有更高的集成度,更低的功耗,節省了電路板面積,其中的雙核ARM Cortex-A9處理器子系統與FPGA子系統之間通信的帶寬大大增加.FPGA子系統能夠高速完成數字信號處理算法及FFT運算、電壓閃變計算等任務,對于6路的LVDS信號采集、調理、濾波、整合可以用FPGA子系統進行并行處理,大大加速了系統的進程[6].通過大吞吐量數據通路(AXI),實現ARM Cortex-A9 MPCore處理器系統和FPGA的互聯,峰值帶寬超過100 Gbps,保證了數據傳輸的連續性,與其他應用處理器相比,功耗大大降低,提高了系統的性能[7].

3.2 ADS8364芯片簡介

本系統選用的A/D轉換芯片型號為TI公司的ADS8364芯片.ADS8364是TI公司生產的一款6通道同步采樣的模數轉換器,具有高速、低功耗的特點,采用的是+5 V供電,而且帶有80 dB共模抑制的全差分輸入通道、6個獨立的模數轉換器,符合本文多路數據采集系統的需要.ADS8364對數據進行轉換的結果是16位,由BYTE、ADD和地址線A2、A1、A0的組合控制來分別設置為直接讀取方式、循環讀取方式以及FIFO方式[8].模擬與數字邏輯電源均采用+5 V供電,數字接口緩沖電源采用3 V~5 V,使其能夠方便地與FPGA進行接口設計. ADS8364工作時序圖如圖2所示.

圖2 ADS8364工作時序圖Fig.2Operational timing chart of ADS8364

3.3 數據采集系統設計原理

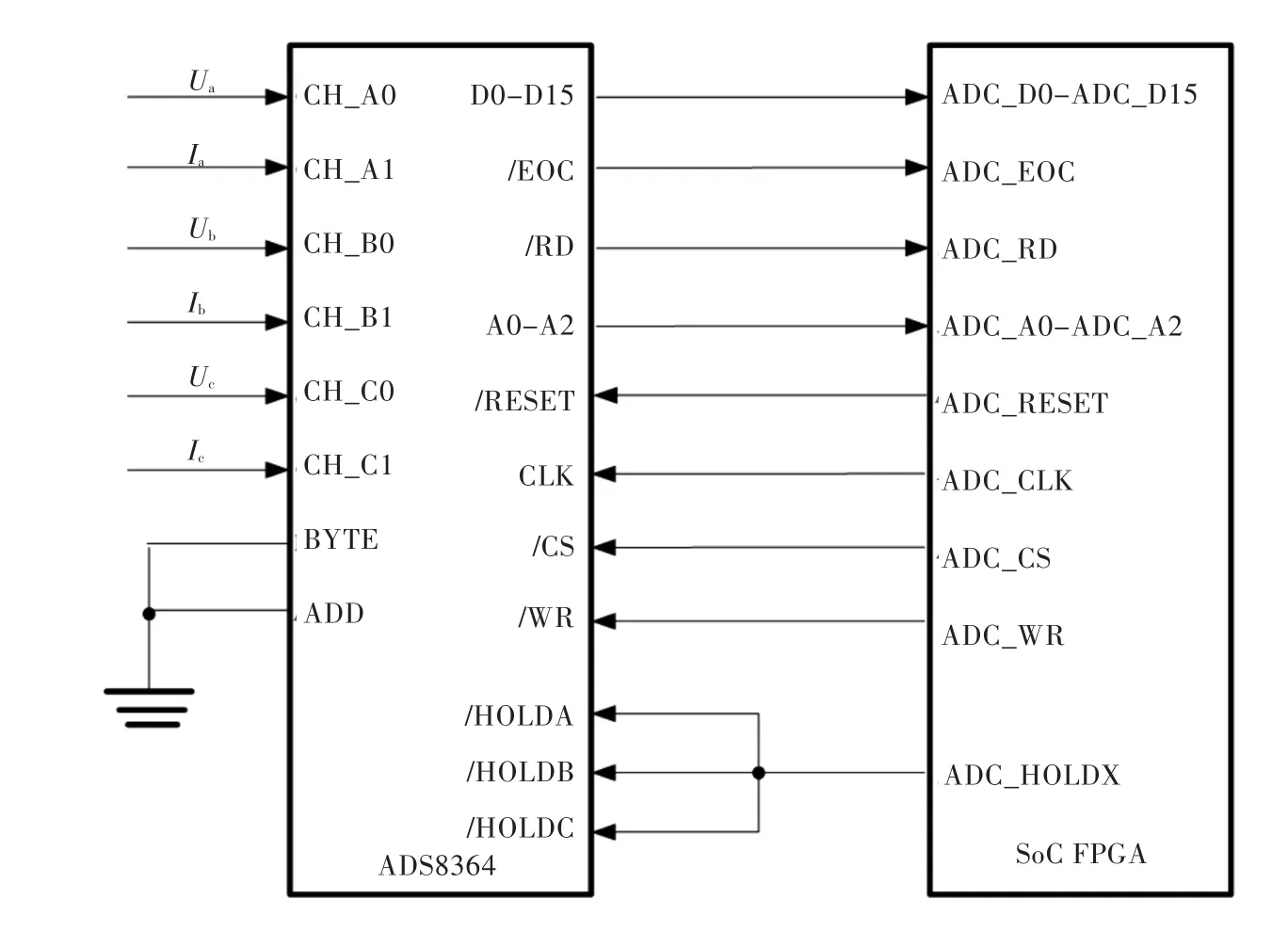

將ADS8364與SoCFPGA的FPGA子系統相連,AD轉換的控制信號由FPGA子系統給出,同時,ADS8364工作所需的時鐘信號也由FPGA給出,這樣可以靈活地改變時鐘速率,以便在不同的速率下進行調整,便于FPGA做整體的時序控制.在模/數轉換過程中,FPGA子系統通過對啟動轉換控制引腳,時鐘引腳等的控制來進行AD轉換.當ADS8364的HOLDX保持至少20 ns的低電平時,開始進行AD轉換.當轉換結束后,轉換結果將被存入輸出寄存器,在ADS8364芯片的------EOC引腳會產生一個低電平信號,此低電平信號會觸發FPGA選通AD芯片的片選信號,同時訪問AD模塊預先設定的地址空間,并讀取AD轉換后寄存器里的數據[9-12].將RD和CS引腳設置為低電平可以讓數據通過并行輸出總線讀出.在讀取數據后,FPGA在下一次數據采集過程之前,完成對數據的處理.數據采集模塊的硬件結構圖如圖3所示.

圖3 數據采集模塊硬件結構圖Fig.3Hardware structure diagram of data acquisition module

4 數據采集系統軟件設計及仿真

4.1 系統軟件設計

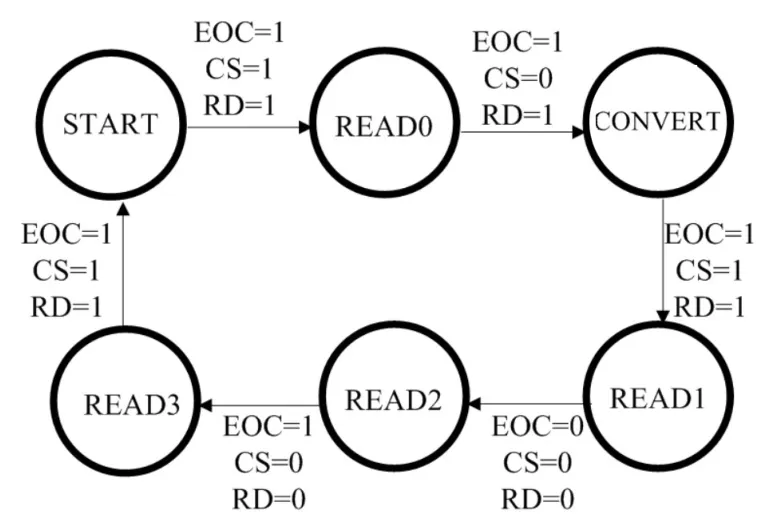

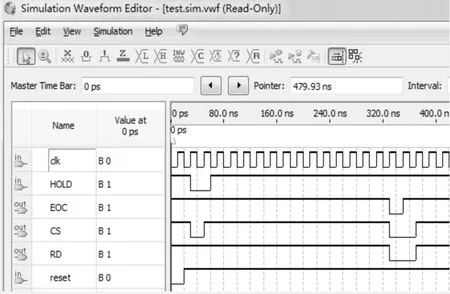

在Altera公司的Quartus II13.0軟件平臺下,使用VHDL硬件描述語言進行邏輯描述,根據ADS8364的工作原理及工作時序分析,把整個工作流程分為START、READ0、CONVERT、READ1、 READ2、READ3六個工作狀態,各個狀態之間的轉換關系及在EDA工具中進行編譯與仿真的ADS8364控制時序圖分別如圖4、圖5所示.對比圖5和圖2可以看出FPGA子系統實現了對ADS8364的正確控制,仿真結果基本與ADS8364的工作時序相符.

圖4 狀態轉移圖Fig.4State transition diagram

圖5 系統仿真圖Fig.5System simulation diagram

4.2 諧波分析

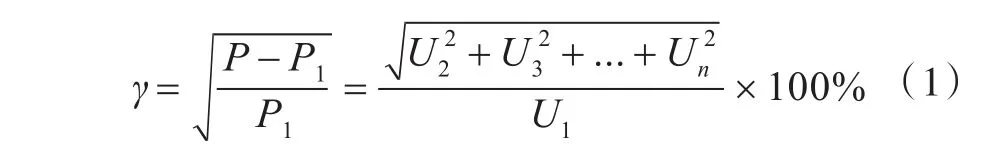

諧波分析的核心是FFT(快速傅里葉變換),將AD轉換產生的數字信號由時域變換到頻域,為后期的諧波分析做準備,對檢測到的一個周期的諧波信號進行傅里葉變換,得到各次諧波的相位和幅值.采用FFT對量化后的被測信號進行處理,獲得基波和各次諧波的電壓,從而計算出失真度,失真度的計算公式為

式(1)中:γ為失真度;P為信號的總功率;P1為基波信號的功率;U1為基波電壓的有效值;U2~Un為諧波電壓的有效值.

FFT運算器采用FFT MegaCore實現.本系統用到Altera公司Cyclone V系列5CSEMA5,該芯片能夠完全支持FFT MegaCore,能有效提高FFT部分的開發效率,縮短工程開發周期[13-15].為了盡量減少轉換時間,將FFT處理器設置成四輸出引擎結構,算法用到了基-4FFT算法,I/O數據流結構設置為Buffered Burst,采樣點數設置為512點,能夠占用更小的內存資源.設計中只需對FFT IP核進行配置以及數據輸入和結果讀取.

4.3 FFT仿真

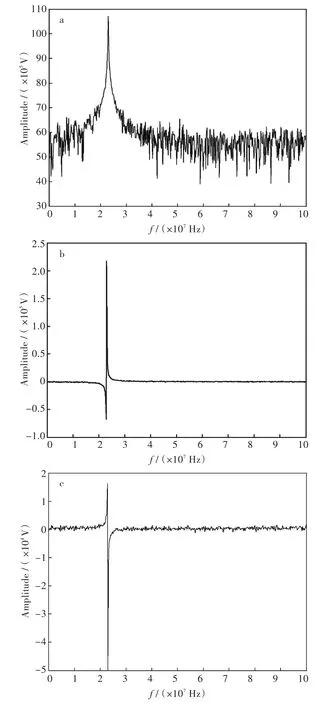

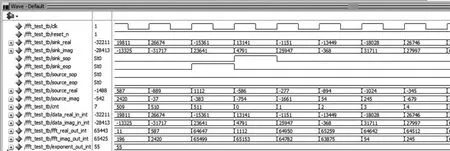

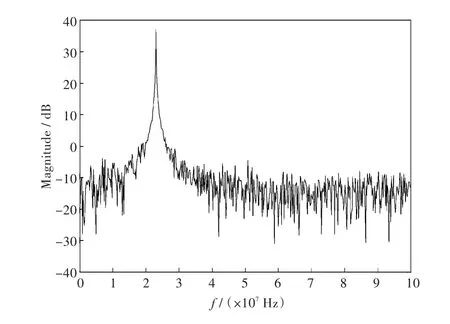

在MATLAB中產生用于測試的輸入數據,將其寫入到.mif文件中,對數據的實部和虛部信息進行保存,用作測試數據,輸入數據信息如圖6所示.在Quartus II 13.0軟件中對FFT IP核進行配置,并且添加兩個ROM分別存儲輸入數據的實部和虛部.FPGA用來對輸入數據做FFT運算.FFT部分在Modelsim中的仿真結果如圖7所示,FPGA對輸入數據的實部虛部信息進行了存儲.MATLAB對FFT運算后的數據分析如圖8所示.

圖6 測試數據信息(a)幅頻特性;(b)測試數據實部;(c)測試數據虛部Fig.6Information of test data(a)Amplitude-frequency characteristics;(b)Real part of test data;(c)Imaginary part of test data

圖7 FFT仿真Fig.7FFT simulation

圖8 MATLAB仿真Fig.8MATLAB simulation

通過對比圖6和圖8,可以看出:FPGA實現了512點的FFT運算.

5 結語

筆者設計的SoCFPGA的同步數據采集系統,實現了SoCFPGA對ADS8364的控制,同時也實現了512點的FFT運算.選用SoCFPGA作為控制器件,充分發揮ADS8364芯片的高速、高精度的特點,使得集成化程度大大提高,數據采集硬件更加簡單,控制更加靈活,另外,FPGA編程方式靈活,軟件工具強大,可縮短系統的開發周期,提高工作效率.因此,本系統可用于高速實時數據采集系統等領域.

[1]劉書明,聶麗斌,余愛民.ADS8364的原理及應用[J].國外電子元器件,2002,33(10):43-45.

LIU S M,NIE L B,YU A M.The principle and application of ADS8364[J].International electronic elements,2002,33(10):43-45.

[2]駱東松,黃錦華,陳若珠,等.電能質量分析儀的研制[J].自動化儀表,2010,31(11):61-63.

LUO D S,HUANG J H,CHEN R Z,et al.Research and development of the quality analyzer for electric power[J].Process automation instrumentation,2010,31(11):61-63.

[3]霍銀龍.基于FPGA+ARM的電能質量監測裝置的研制[D].南京:南京師范大學,2013.

[4]駱曉明,楊拴科,金印彬.基于DSP+ARM的便攜式電能質量分析儀設計[J].現代電子技術,2010,33(5):179-181.

LUO X M,YANG S K,JIN Y B.Design of portable power quality analyzer based on DSP+ARM[J].Modern electronics technique,2010,33(5):179-181.

[5]柏玉峰,靳斌,劉曉飛.ADS8364在高精度電能質量分析儀中的應用[J].中國儀器儀表,2006,12(1):68-70.

BO Y F,JIN B,LIU X F.Application of ADS8364 in high precision power quality analyzer[J].China instrumentation,2006,12(1):68-70.

[6]吳彩林,寧平華,夏興國.基于ARM+FPGA的電能質量分析儀設計[J].齊齊哈爾大學學報,2014,30(4):9-14. WU C L,NING P H,XIA X G.Design of power quality analyzer based on ARM and FPGA[J].Journal of Qiqihar university,2014,30(4):9-14.

[7]辛鳳艷,孫曉曄.基于FPGA的AD轉換控制器設計[J].中國科技信息,2012,35(5):78-79.

XIN F Y,SUN X Y.Design of the AD conversion controller based on FPGA[J].China science and technology information,2012,35(5):78-79.

[8]許孟杰,劉文臣,劉云.基于FPGA的AD采樣設計[J].艦船電子工程,2015,33(1):114-118.

XU M J,LIU W C,LIU Y.Design of AD sampling based on FPGA[J].Ship electronic engineering,2015,33(1):114-118.

[9]劉國營,劉俊,李杰.基于ADS8364和DSP的高精度數據采集系統設計[J].微計算機信息,2007,23(23):190-191.

LIU G Y,LIU J,LI J.Design of high accuracy data acquisition system based on ADS8364 and DSP[J].Microcomputer information,2007,23(23):190-191.

[10]程佩青.數字信號處理[M].北京:清華大學出版社,2007.

[11]龐國龍.基于TMS320VC5509 DSP的FIR數字濾波器的實現[J].電子技術,2011,38(4):47-48.

PANG G L.Implementation of FIR digital filter based on TMS320VC5509 DSP[J].Electronic technology,2011,38(4):47-48.

[12]楊志芳,王澤成,涂坦,等.基于FPGA的多路高速數據采集系統的實現[J].武漢化工學院學報,2006,28(3):58-61.

YANG Z F,WANG Z C,TU T,et al.Multi-channel high speed data acquisition system based on FPGA[J]. Journal of Wuhan institute of chemical technology,2006,28(3):58-61.

[13]楊志方,涂坦,談宏華.基于FPGA和ARM的新型電能質量監測系統的設計[J].長江大學學報,2007,4(2):69-72.

YANG Z F,TU T,TAN H H.Design of a new electric energy quality detection system based on FPGA and ARM[J].Journal of Yangtze university,2007,4(2):69-72.

[14]熊俊俏,周建軍,熊詩琪.快速圖像數據采集與顯示控制器的設計[J].武漢工程大學學報,2012,34(1):61-64.

XIONG J Q,ZHOU J J,XIONG S Q.Design of high speed image acquisition and display controller[J]. Journal of Wuhan institute of technology,2012,34(1):61-64.

[15]崔士杰,汪建華.基于MATLAB的單相全控整流電路功率因數測定[J].武漢工程大學學報,2010,32(1):90-92.

CUI S J,WANG J H.Measurement based on MATLAB of power factor of fully controlled single-phase commutation[J].Journal of Wuhan institute of technology,2010,32(1):90-92.

本文編輯:陳小平

Design of Synchronous Data Acquisition System Based on SoCFPGA

YANG Zhifang,HU Mengdie,CHEN Jue,WANG Lei

School of Electrical and Information Engineering,Wuhan Institute of Technology,Wuhan 430205,China

To meet the requirements of multi-channel data acquisition in power quality analysis system,we designed a synchronous data acquisition system based on SoCFPGA,taking Altera SoCFPGA as the core of the hardware platform and combining with the analog-digital conversion chip ADS8364 to build the 6 channels synchronous data acquisition system.Firstly,we employed both software and hardware for co-design,and described the logic of the AD conversion control process in VHDL,and then the data were processed by FFT core and the amplitude-frequency characteristics of them were displayed,which prepared for the following harmonic analysis.The simulation results indicate that SoCFPGA is able to well control the ADS8364 and 512-point FFT operation.The system makes the data acquisition hardware structure simpler and the degree of integration higher,which shortens the system development cycle,meeting the needs of data synchronous acquisition in practice.

synchronous data acquisition;SoCFPGA;ADS8364;software simulation

TP211

A

10.3969/j.issn.1674-2869.2016.06.014

1674-2869(2016)06-0588-06

2016-06-15

湖北省科技廳自然科學基金項目(2014CKC524)

楊志芳,碩士,副教授.E-mail:frank@wit.edu.cn